随着多芯片系统在半导体领域变得越来越普遍,通用小芯片互连高速(UCIe)规范正在成为焦点。

由于其对高带宽和高性能的支持,以及其灵活性,UCIe有望成为引领新一轮创新浪潮的黄金标准。

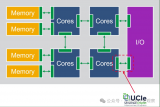

传统的单片 SoC 正在达到超大规模数据中心的人工智能 (AI)、机器学习 (ML) 和高性能计算 (HPC) 等数据密集型应用的功耗、性能和面积 (PPA) 限制。响应号召的是多芯片系统,由单个芯片或小芯片组成,通过支持离散功能或乘以单个芯片的功能来扩展性能。它们集成在标准或高级包中。

虽然单片芯片正在接近制造上限,但多芯片系统可以提供更多的系统功能、增强的 PPA、更好的良率以及更低的成本来支持先进的设计。UCIe 为可定制的、基于标准的封装级小芯片集成提供了支持。一个开放的规范,它定义了封装内小芯片之间的互连。其特性非常适合多芯片系统的要求。

支持当今和未来的带宽需求

虽然已经出现了几种不同的标准来解决多芯片系统的挑战,但UCIe是唯一具有芯片间接口完整堆栈的标准。该规范支持 2D 和 2.5D 包,预计未来将推出 3D 包。其他标准仅关注协议栈的特定层,缺乏确保实现之间互操作性的完整芯片到芯片接口的全面规范。

UCIe 适用于当今每个引脚 8 Gbps 至 16 Gbps 的大部分设计;它还支持每个引脚 32 Gbps 的设计,适用于未来的高带宽应用,如网络和超大规模数据中心。有两种封装变体可供选择。用于高级封装的UCIe支持硅中介层、硅桥和再分布层(RDL)扇出,而用于标准封装的UCIe支持有机衬底和层压板。

UCIe 堆栈本身由三层组成。顶部是协议层,它通过基于流控制单元(基于 FLIT)的协议实现确保最大效率和减少延迟。协议层支持常用规范,包括 PCI Express® (PCIe®)、计算快速链路 (CXL) 和/或用户定义的流式处理协议。在第二层,协议进行仲裁和协商,链路管理通过芯片到芯片适配器进行。该层实现基于循环冗余校验 (CRC) 和重试机制的错误检测和纠正功能。PHY 标记第三层,指定与封装介质的电气接口。在PHY层中,电模拟前端(AFE)、发射器和接收器以及边带通道允许两个芯片之间进行参数交换和协商。Logic PHY 实现了链路初始化、训练和校准算法以及测试和修复功能。

经过验证的 IP 如何实现强大的芯片间链路

为了简化UCIe在多芯片系统设计中的应用,设计人员可以转向PHY、控制器和验证IP。PHY IP 支持标准和高级封装选项,可提供灵活性,而在高级 FinFET 工艺中,可支持高带宽、低功耗和低延迟的芯片间连接。控制器 IP 支持与 PCIe 和 CXL 等常用协议一致的解决方案,并可通过流协议实现延迟优化的片上网络 (NoC) 到 NoC 链路;例如,桥接到 CXS 接口和 AXI 接口。最后,在全栈的每一层支持各种被测设计 (DUT) 的验证 IP 有助于加快运行时间,以及设计的调试和覆盖收敛。

正确的 PHY、控制器和验证 IP 集可以带来可靠、稳健的芯片间链路,具有低延迟和高能效。针对已知良好芯片的内置可测试性功能以及用于纠错的 CRC 或奇偶校验检查支持芯片良率和质量目标。

审核编辑:郭婷

-

soc

+关注

关注

38文章

4174浏览量

218441 -

AI

+关注

关注

87文章

31028浏览量

269384 -

ML

+关注

关注

0文章

149浏览量

34669

发布评论请先 登录

相关推荐

一文解析UCIe技术细节

Chiplet芯片互联再进一步,AMD、ARM、英特尔联手发布UCIe 1.0标准

芯原股份加入UCIe产业联盟 推动UCIe技术标准应用

浅谈UCIe对解决多芯片系统的设计

设计更简单,运行更稳健,UCIe标准如何“拿捏”Multi-Die系统?

深度详解UCIe协议和技术

新思科技发布全球领先的40G UCIe IP,助力多芯片系统设计全面提速

柔性基板异质集成系统的印刷互连技术

为什么UCIe是多芯片系统的集成互连

为什么UCIe是多芯片系统的集成互连

评论