今天是 74LS76双JK触发器,主要是以下几个方面:

1、74LS76 是什么芯片?

2、74LS76 双JK 触发器 引脚排列

3、74LS76双JK触发器工作原理

4、74LS76 双JK触发器 规格参数

5、74LS76双JK触发器特性

6、74LS76双JK触发器等效替代

7、74LS76双JK触发器应用电路

一、74LS76 是什么芯片?

74LS76 带有独立的 JK 时钟脉冲、直接清除输入和直接设置的双JK触发器。触发器的开发方式是,当时钟设置为高电平时,将接收数据使能输入。

74LS76 IC 中的 JK 触发器还具有预设和清除功能,允许 IC 绕过时钟和输入并提供不同的输出。74LS76 是基于 TTL 的,可以与任何基于 TTL 的设备或任何微控制器一起操作。IC 有多种封装形式,使 IC 可以根据要求使用任何硬件。如有必要,可以使用多个 IC 制作更多 IC。

74LS76 的实际应用是在位的存储中,尽管它对其他应用也很有价值。几个特性使 Jk 触发器成为最常见的类型之一。它们包括以下内容:

时钟输入属性

预设输入引脚的存在

同样值得注意的是,JK 触发器可以通过施加时钟脉冲信号来改变它们的状态。请注意,此时钟信号可以是上升沿或下降沿。此外,74LS76 能够忽略无效输出。

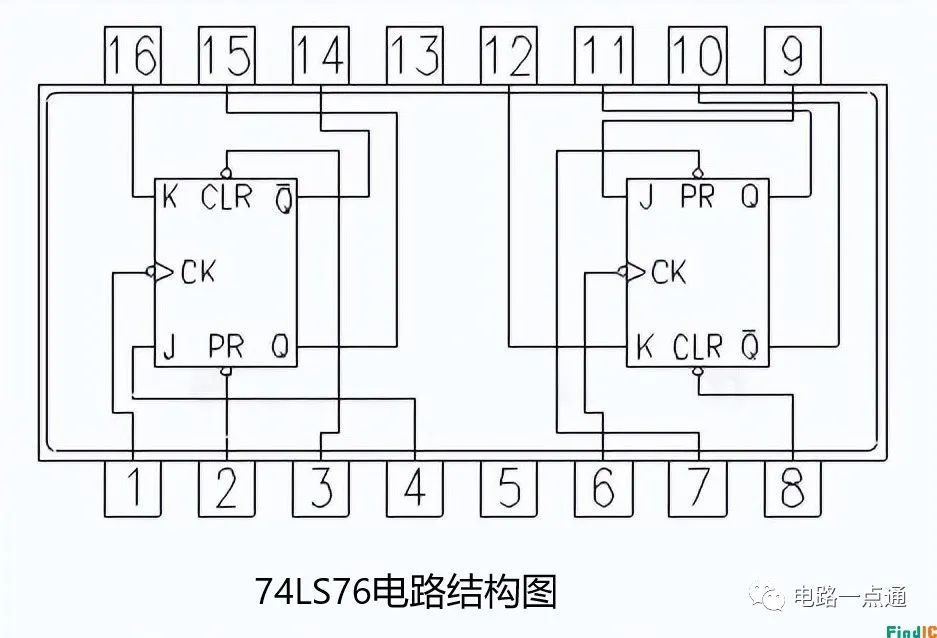

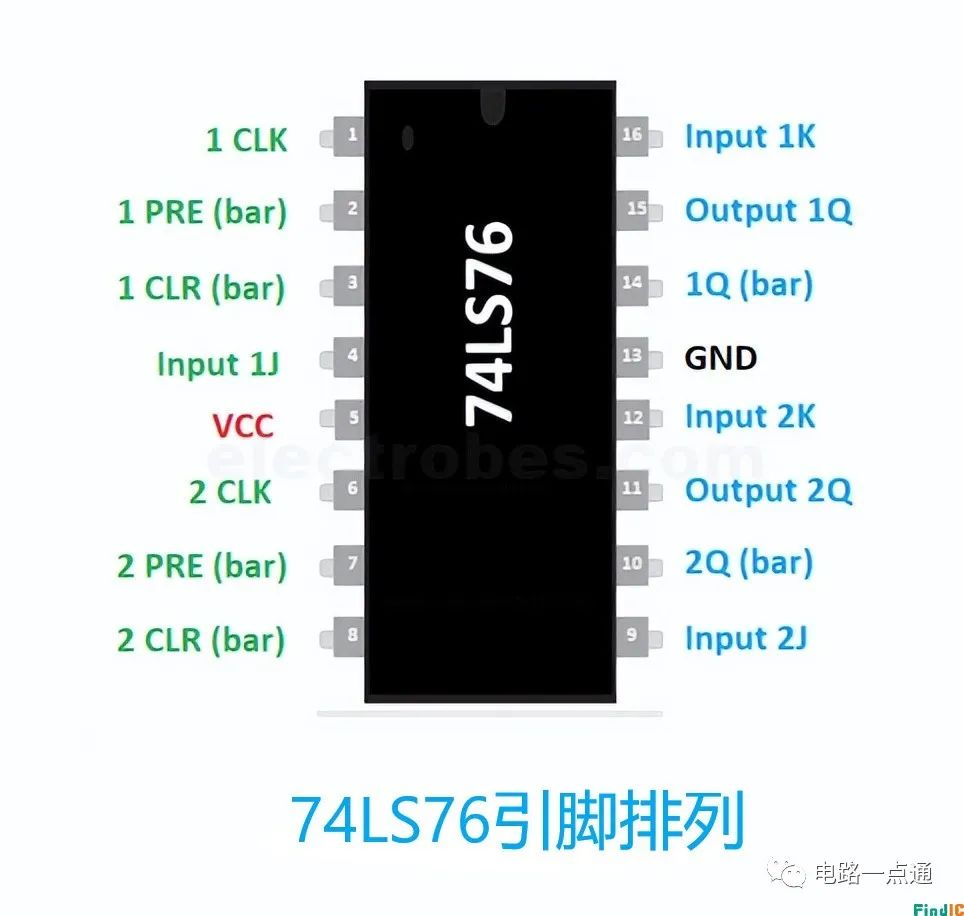

二、74LS76 双JK触发器引脚排列

74LS76 双JK触发器引脚排列

74LS76 双JK触发器引脚排列

74LS76 双JK触发器引脚说明

74LS76 双JK触发器引脚说明

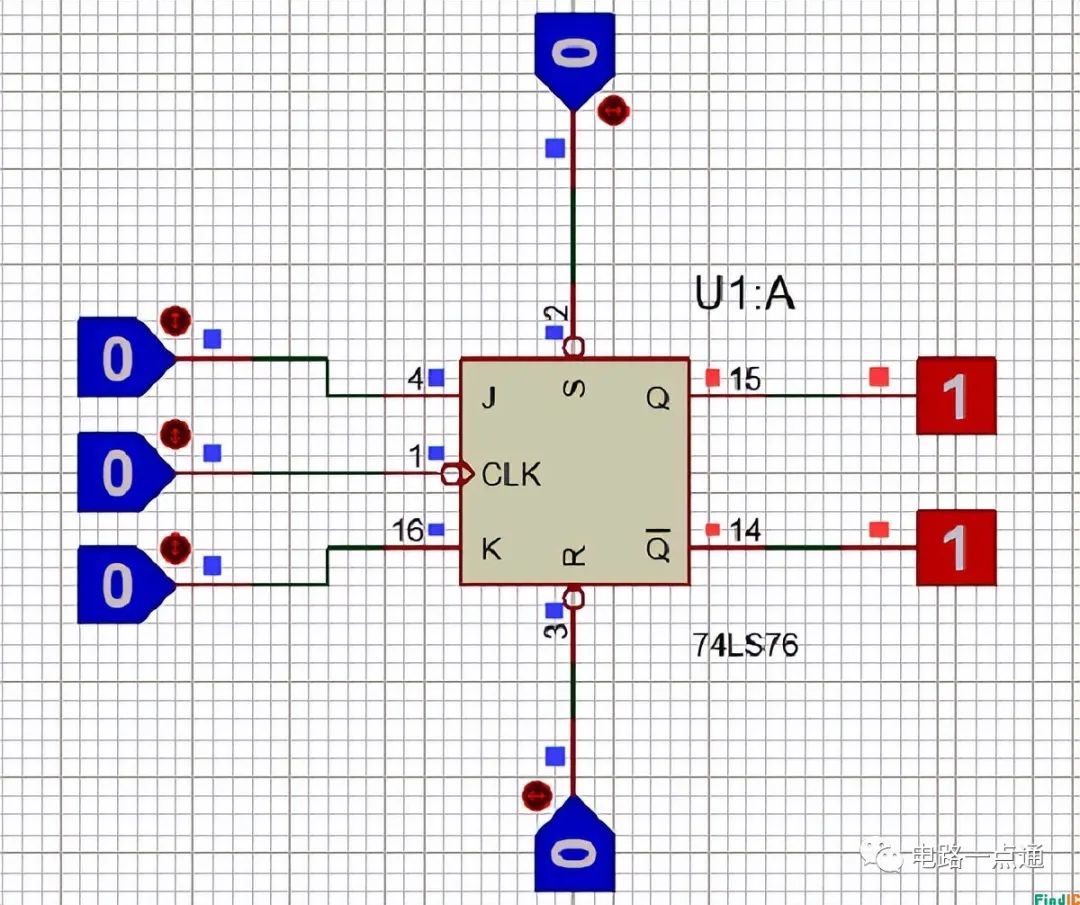

三、74LS76 双JK触发器工作原理

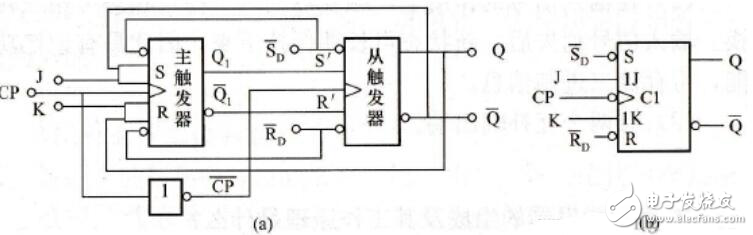

正如前面说的,我们在该 IC 中有两个 JK 触发器,该 IC 通常由 +5V 供电。输入 (J, K) 引脚和输出 (Q, Q bar) 引脚的最小和最大输入和输出电压在上述规格中进行了讨论。JK触发器的工作原理如下图所示 。

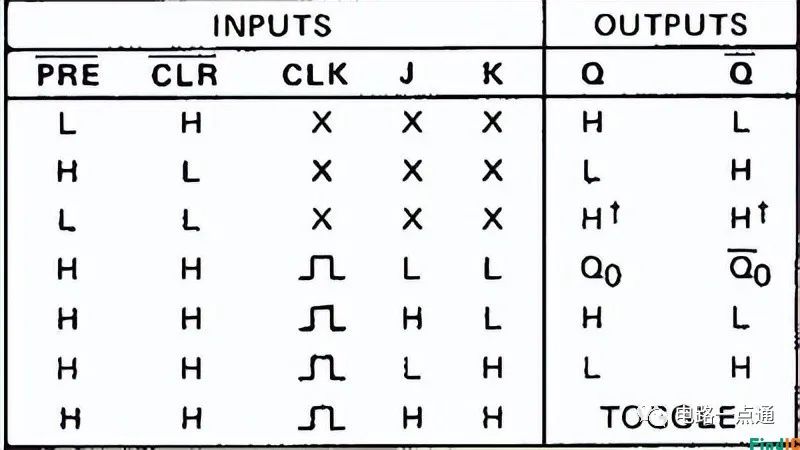

74LS76 双JK触发器工作原理图 预设和清除是异步低电平有效输入。当预设和清除设置为低时,它们会覆盖时钟和 JK 输入,强制输出达到稳态电平。 74LS76 有 5 个输入引脚和两个输出引脚。输出将取决于几乎每个输入引脚。当 IC 在复位引脚处于低电平状态时,输出引脚将为低电平,在反相输出时,状态将为高电平。 现在另一个输入引脚知道为预设。当预设将处于高电平状态时,输出引脚将为高电平,而在反相输出时,状态将为低电平。要使用 IC,我们需要将它们保持在低电平,如果两个引脚上的高电平状态,输出和反相输出都会给出高电平状态。复位引脚和清除将在不同输入处具有这些状态。

74LS76 双JK触发器工作原理 当 clear = 1 和 preset = 1 时,输出将根据 J 和 K 输入在 HIGH 到 LOW 时钟脉冲上变化。当 J 和 K 两个输入都为低电平时,输出不会有任何变化。输出将取决于先前的状态。在 J = 1 和 K = 1 的情况下,输出将在每个时钟脉冲处保持翻转。 其他状态将根据下面的真值表。

74LS76 双JK触发器工作原理 上面两张表解释了 JK FF 的一般工作,这个真值表描述了 74LS76 的功能,具有清晰和预设的特征。

74LS76 双JK触发器工作原理

四、74LS76 双 JK触发器 规则参数

双 JK 触发器封装 IC

工作电压:2V 至 6V

最小高电平输入电压:2 V

最大低电平输入电压:0.8 V

最小高电平输出电压:3.5 V

最大低电平输出电压:0.25V

工作温度 -55 至 -125°C

提供 14 引脚 PDIP、GDIP、PDSO 封装

五、74LS76 双JK触发器特性

首先,它是一个双 JK 触发器,但在 1 个 IC 内。

具有 J、K 时钟、置位和清零输入的两个独立触发器。

7476A 具有多个带有 14 引脚 PDIP、GDIP 和 PDSO 的封装。

功能清除和预设是 74LS76 的两个基本属性。

IC 是TTL输出形式的代名词。因此,它与微控制器和 TTL 设备兼容。

你可以将 IC 74LS76 作为单个触发器操作,而不会中断其他触发器的工作。

标准 TTL 开关电压。

六、74LS76JK触发器等效替代

等效于 74LS76:74LS73、MC74HC73A、SN7476 替代品 JK 触发器:74LS107、4027B

七、74LS76 双JK触发器应用电路

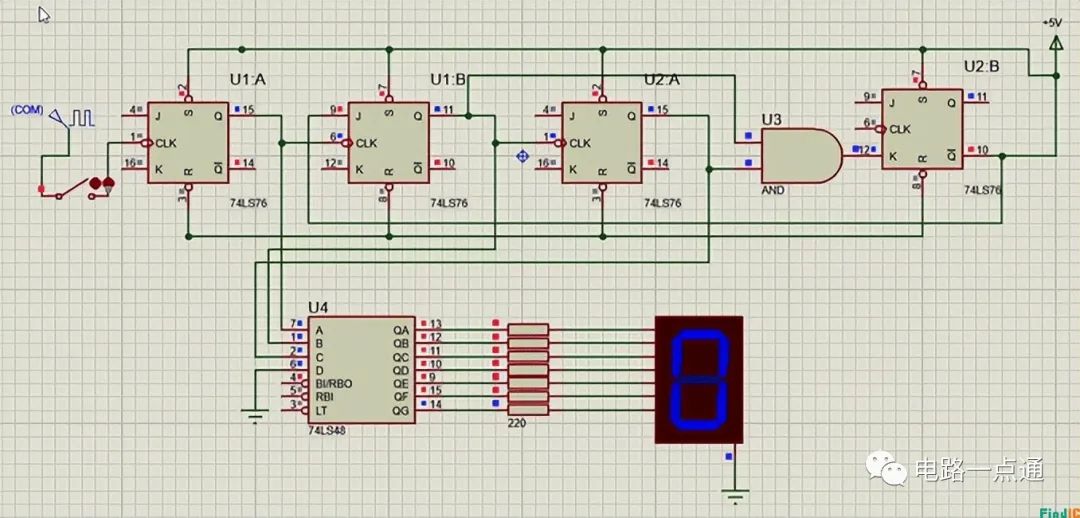

1、74LS76 的 0-9 计数器示例

在此示例中,我们将使用 JK 触发器构建一个 3 位计数器,然后我们将通过将其转换为 7 段上的十进制来显示该值。要设计一个三位计数器,我们需要一个额外的组件,即与门,然后我们将使用四个 JK 触发器。在设计完位计数器后,我们将使用 IC74LS76 将二进制数据转换为共阴极7 段。时钟脉冲将产生输出,IC 将显示 7 段数据。这是图像。

74LS76 的 0-9 计数器示例 在三位数据中,我们可以存储 000 到 111 的数据,即 8 个值,并且 7 段以十进制显示从 0 到 7 的值。JK 触发器存储每个值并在每个时钟脉冲上生成新值。74LS48 用作 BCD 到 7 段解码器,我们可以在时钟脉冲改变之前的任何时间接收到这个值。在微处理器和控制器中,时钟引脚由手动信号控制以替换数据,直到数据保持存储,这个过程使触发器最适合在多个设备中临时存储数据。

2、其他应用

它用于将电荷存储在 RAMS 中。

74LS76 也使用了一个锁存器。

IC可用于设计计数器。

审核编辑:汤梓红

-

IC

+关注

关注

36文章

6481浏览量

186386 -

应用电路

+关注

关注

9文章

468浏览量

50868 -

TTL

+关注

关注

7文章

557浏览量

75040 -

引脚

+关注

关注

16文章

2120浏览量

56030 -

触发器

+关注

关注

14文章

2065浏览量

63564

原文标题:双JK触发器工作原理+应用电路详解

文章出处:【微信号:电路一点通,微信公众号:电路一点通】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

JK触发器基本教程,讲的超详细!!

施密特触发器电路及工作原理详解_施密特触发器特点_施密特触发器的作用

双JK触发器的工作原理和应用电路详解

双JK触发器的工作原理和应用电路详解

评论