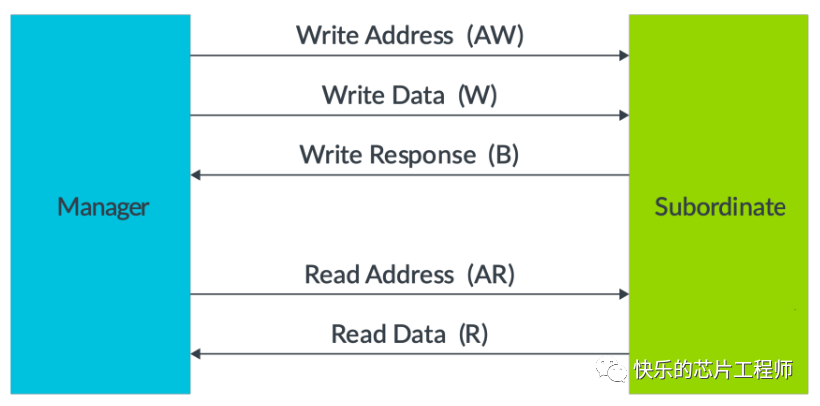

AXI 规范描述了两个接口之间的点对点协议:manager andsubordinate接口。

下图显示了每个 AXI 接口用于通信的五个主要通道:

写操作使用以下通道:

manager在写地址 (AW) 通道上发送地址,并在写数据 (W) 通道上将数据传输给subordinate。

subordinate将接收到的数据写入指定地址。一旦subordinate完成写操作,它就会在写响应 (B) 通道上向manager响应一条消息。

读取操作使用以下通道:

manager在读取地址 (AR) 通道上发送它想要读取的地址。

subordinate在读取数据 (R) 通道上将数据从请求的地址发送到manager。

subordinate还可以在读取数据 (R) 通道上返回错误消息。例如,如果地址无效、数据损坏或访问没有正确的安全许可,则会发生错误。

每个通道都是单向的,因此需要一个单独的 Write Response 通道来将响应传回manager。但是,不需要读取响应通道,因为读取响应作为读取数据通道的一部分传递。

使用单独的地址和数据通道进行读取和写入传输有助于最大化接口的带宽。读写通道组之间没有时序关系。这意味着读取序列可以与写入序列同时发生。

这五个通道中的每一个都包含几个信号,每个通道中的所有这些信号都有如下前缀:

AW 用于写地址通道上的信号

AR 用于读取地址通道上的信号

W 用于写入数据通道上的信号

R 表示读取数据通道上的信号

B 用于写响应通道上的信号

B代表缓冲,因为subordinate的响应发生在所有写入完成之后。

审核编辑:刘清

-

AXI总线

+关注

关注

0文章

66浏览量

14250

原文标题:【AXI--04】AXI channels

文章出处:【微信号:快乐的芯片工程师,微信公众号:快乐的芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AXI VIP设计示例 AXI接口传输分析

Zynq MPSoC系列器件的AXI总线介绍

从应用角度详解什么是AXI

AXI 总线和引脚的介绍

AXI总线协议的几种时序介绍

何谓 AXI?关于AXI3/AXI4的相关基础知识

ZYNQ中DMA与AXI4总线

AMBA 3.0 AXI总线接口协议的研究与应用

全面介绍ZYNQ-AXI互联IP

AXI channels介绍

AXI channels介绍

评论