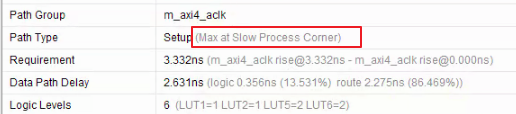

在FPGA的时序分析页面,我们经常会看到Max at Slow Process Corner和Min at Fast Process Corner,具体是什么含义呢?

image-20220806233120287

image-20220806233155182

什么是process corner(工艺角)?

维基百科给出的解释为:

In semiconductor manufacturing, a process corner is an example of a design-of-experiments (DoE) technique that refers to a variation of fabrication parameters used in applying an integrated circuit design to a semiconductor wafer. Process corners represent the extremes of these parameter variations within which a circuit that has been etched onto the wafer must function correctly. A circuit running on devices fabricated at these process corners may run slower or faster than specified and at lower or higher temperatures and voltages, but if the circuit does not function at all at any of these process extremes the design is considered to have inadequate design margin.

再给出知乎上的一段解释:

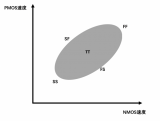

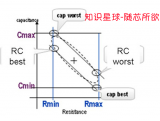

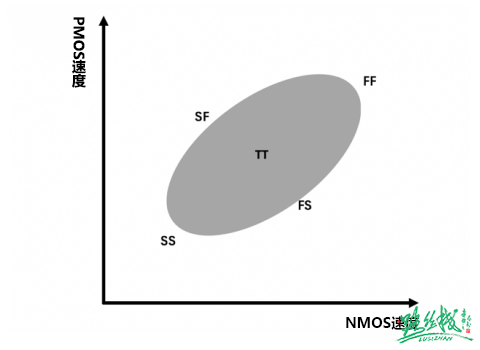

与双极晶体管不同,在不同的晶片之间以及在不同的批次之间,MOSFETs 参数变化很 大。为了在一定程度上减轻电路设计任务的困难,工艺工程师们要保证器件的性能在某 个范围内。如果超过这个范围,就将这颗IC报废了,通过这种方式来保证IC的良率。传统上,提供给设计师的性能范围只适用于数字电路并以“工艺角”(Process Corners)的形式给出。其思想是:把NMOS和PMOS晶体管的速度波动范围限制在由四个角所确定的矩形内。这四个角分别是:快NFET和快PFET,慢NFET和慢PFET,快NFET和慢PFET,慢NFET和快PFET。例如,具有较薄的栅氧、较低阈值电压的晶体管,就落在快角附近。从晶片中提取与每一个角相对应的器件模型时,片上NMOS和PMOS的测试结构显示出不同的门延迟,而这些角的实际选取是为了得到可接受的成品率。因此,只有满足这些性能的指标的晶片才认为是合格的。在各种工艺角和极限温度条件下对电路进行仿真是决定成品率的基础。

再补充点芯片工艺的其他小知识:

即便是同一种FF,在同一个芯片上不同操作条件下的延时都不尽相同,我们称这种现象为OCV(on-chip variation)。OCV表示的是芯片内部的时序偏差,虽然很细小,但是也必须严格考虑到时序分析中去。

产生OCV的原因主要有PVT(Process / Voltage / Temperature)三个方面,而STA要做的就是针对不同工艺角(Process Corner)下特定的时序模型来分析时序路径,从而保证设计在任何条件下都能满足时序要求,可以正常工作。

用白话来说:由于工艺的原因,在这些cornor下可能会有不同的性能。

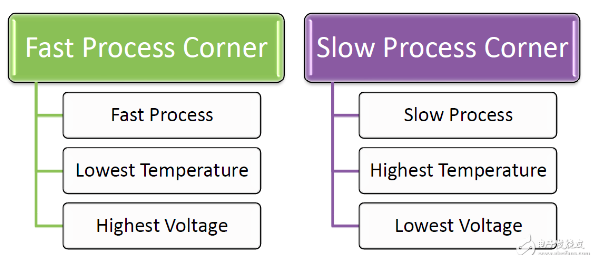

在FPGA设计中的静态时序分析一般仅考虑Best Case和Worst Case,也称作Fast Process Corner 和Slow Process Corner,分别对应极端的PVT条件。

image-20220807095728873

Slow Corner Model: 最高温度,最低电压下的模型

Fast Corner Model: 最低温度,最高电压下的模型

在Vivado中,会对以上两个corner进行时序分析,并给出最差情况的报告。

在setup中分析的是slow process corner,在hold中分析的是fast process corner,这个跟我们第一个图也是对应的。如果在slow process corner模型下能满足setup的要求,那么其他模型也就都能满足;如果在fast process corner模型下能满足hold的要求,那么其他模型下也都能满足。

总结:这两个概念都是跟工艺有关系的,跟fpga开发者的关系并不太大,但对这个概念我们还是要熟悉的,比如同一个路径,setup分析时和hold分析的时延所有所不同,就是因为采用不能的模型分析导致。

-

FPGA

+关注

关注

1637文章

21842浏览量

608596 -

时序

+关注

关注

5文章

392浏览量

37535

发布评论请先 登录

相关推荐

玻璃反光也能误识别?当自动驾驶遇到千奇百怪的corner case

TLV5616和TLV5636两种工作模式FAST和SLOW分别有什么特点,优势,选择时应该注意什么?

怎么在FAST和SLOW广告之间切换

用ADE XLall跑all Corner时 第一个Corner为什么总是会报错?

Dark Corner将在万圣节推出一些恐怖VR体验,迎接万圣节的到来

FPGA时序分析时fast corner和slow corner是什么?

玻璃反光也能误识别?当自动驾驶遇到千奇百怪的corner case

纯python实现(一)Harris corner

温度反转效应它到底为什么会发生呢?

UltraEM®的Corner Sweep仿真实例

FPGA中的fast corner和slow corner介绍

FPGA中的fast corner和slow corner介绍

评论