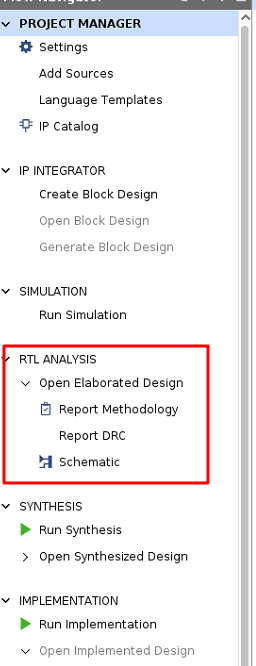

在Vivado的界面中,有个RTL ANALYSIS->Open Elaborated Design的选项,可能很多工程师都没有使用过。因为大家基本都是从Run Synthesis开始的。

elaborate可以翻译为“详尽解析”,就是将RTL源代码翻译转换成对应的电路。

elaborate可以翻译为“详尽解析”,就是将RTL源代码翻译转换成对应的电路。

有同学会问,这不是Synthesis做的工作吗?

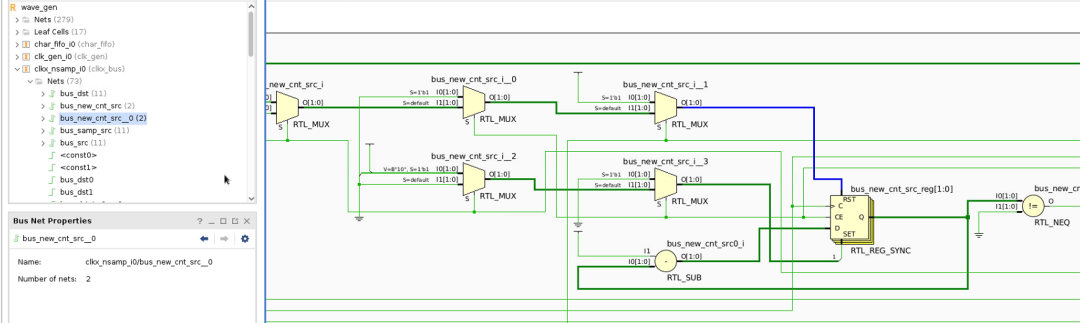

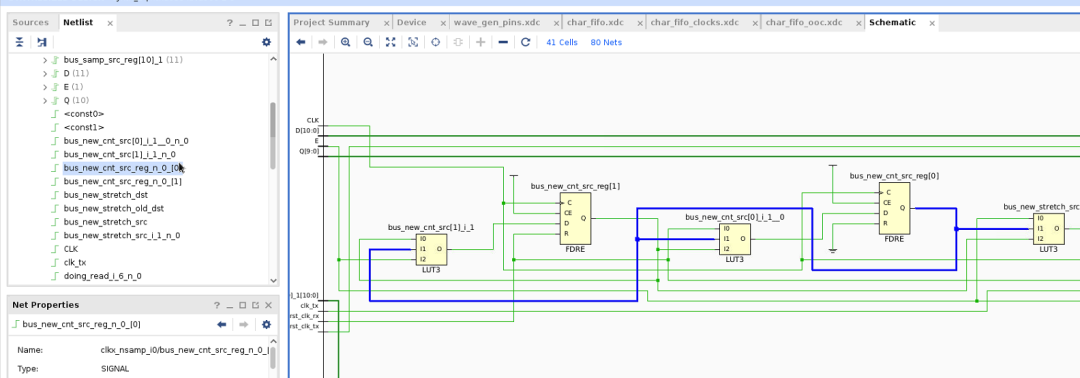

我们可以来比较一下Elaborate和Synthesis后的Schematic就很直观了:

Elaborated Design:

image-20221023165430449

Synthesisd Design:

image-20221023165346017

可以看出,Elaborated Design里面的电路是单纯的对RTL源代码的解析,到了Synthesisd Design,则可以看到Xilinx的具体的库单元,比如LUT3、FDRE等,都是在Xilinx FPGA中真实存在的。

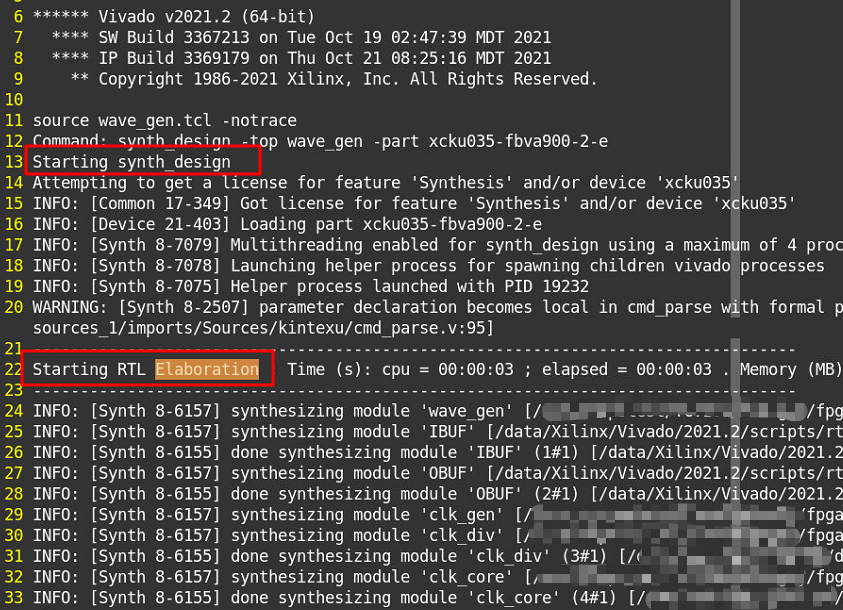

其实在综合的log文件,看到Elaborate的存在,综合的第一步就是先进行Elaborate:

-

RTL

+关注

关注

1文章

385浏览量

59856 -

design

+关注

关注

0文章

158浏览量

45744 -

Vivado

+关注

关注

19文章

813浏览量

66675

发布评论请先 登录

相关推荐

怎么在Vivado 2016.1中关闭特定的DRC违规或警告?

如何从崩溃的vivado安装中恢复或如何卸载部分安装

基于linux系统实现的vivado调用VCS仿真教程

Vivado 2017.1和Vivado 2016.4性能对比分析

Tcl在Vivado中的基础应用

Vivado使用误区与进阶——在Vivado中实现ECO功能

如何在Vivado中应用物理优化获得更好的设计性能

Vivado 2014.1中的许可和激活概述

在Vitis中把Settings信息传递到底层的Vivado

Vivado中的Elaborate是做什么的?

如何在Vivado中添加时序约束呢?

简述Vivado中的Elaborate的作用

简述Vivado中的Elaborate的作用

评论