最近ChatGPT大火,成功破圈,到底是什么?怎么使用?

简单说,它是一个模型,一个语言模型!

它是以对话方式与人进行交互的AI语言模型!

但它能做的事情太多了,可以用它来写一封请假邮件:

image-20221208210153673

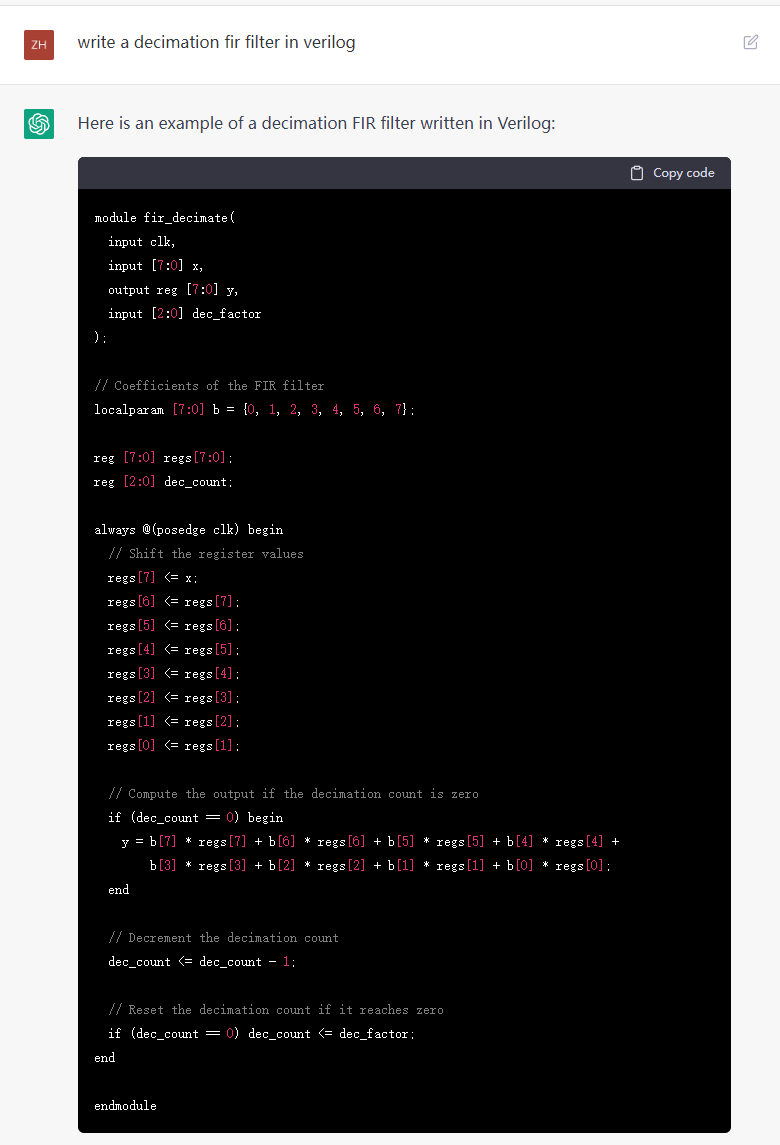

还有人用它来学英语、向它提各种问题,甚至可以用它来写程序,很多软件工程师都尝试过用它来写Python、Java等编程语言,这里我们就不再尝试了。

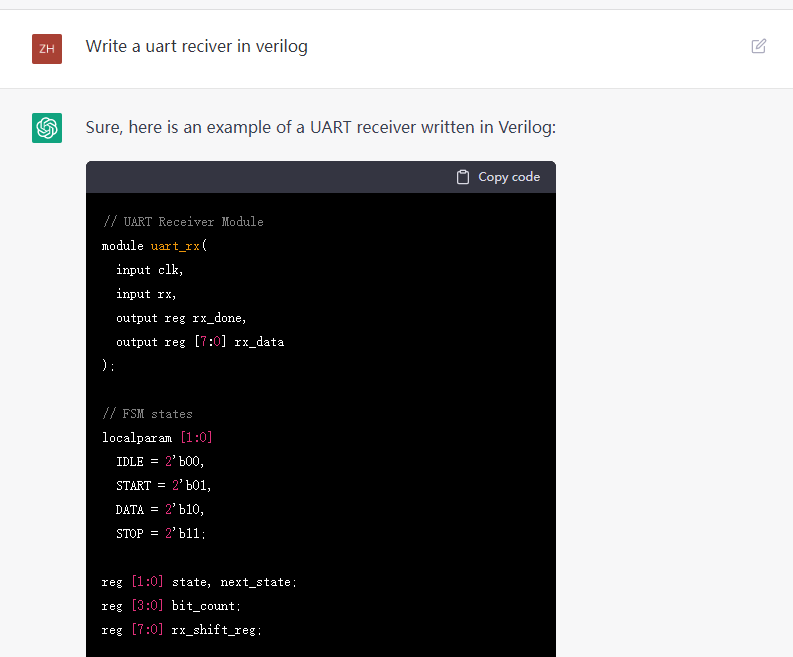

作为FPGA工程师,我们肯定想让它帮我们写Verilog!看看效果怎么样?

,时长00:23

[ ]

image-20221208210533770

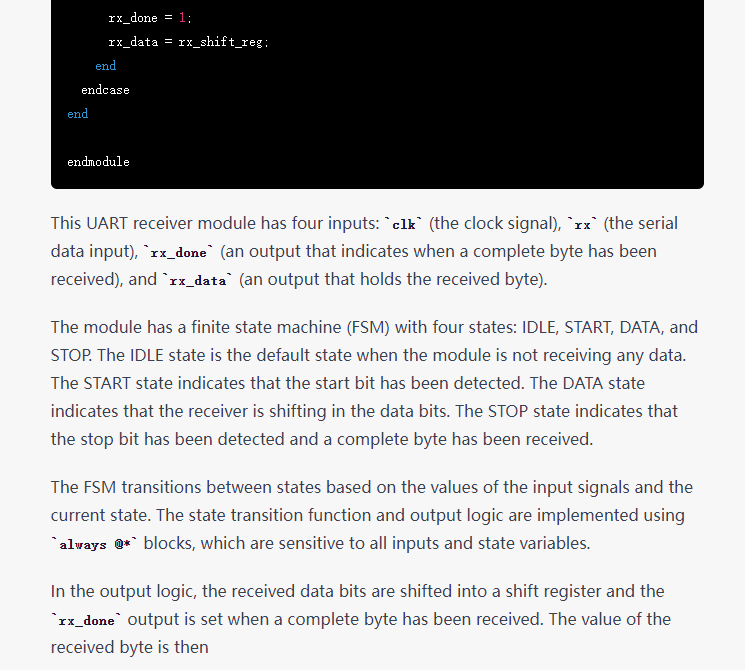

在代码后面甚至还有解释:

image-20221208210631379

完整代码如下:

// UART Receiver Module

module uart_rx(

input clk,

input rx,

output reg rx_done,

output reg [7:0] rx_data

);

// FSM states

localparam [1:0]

IDLE = 2'b00,

START = 2'b01,

DATA = 2'b10,

STOP = 2'b11;

reg [1:0] state, next_state;

reg [3:0] bit_count;

reg [7:0] rx_shift_reg;

// Initialize outputs

always @* begin

rx_done = 0;

rx_data = 0;

end

// State transition logic

always @(posedge clk) begin

state <= next_state;

end

// State transition function

always @* begin

case (state)

IDLE: begin

if (rx) next_state = START;

else next_state = IDLE;

end

START: begin

if (rx) next_state = DATA;

else next_state = IDLE;

end

DATA: begin

if (bit_count == 0) next_state = STOP;

else if (rx) next_state = DATA;

else next_state = IDLE;

end

STOP: begin

if (rx) next_state = IDLE;

else next_state = STOP;

end

endcase

end

// Output logic

always @* begin

case (state)

IDLE: begin

bit_count = 4;

rx_shift_reg = 0;

end

START: begin

bit_count = 3;

end

DATA: begin

bit_count = bit_count - 1;

rx_shift_reg = {rx_shift_reg[6:0], rx};

end

STOP: begin

rx_done = 1;

rx_data = rx_shift_reg;

end

endcase

end

endmodule

虽然没有验证这个功能是否正确,但这个代码的逻辑看起来应该是没有错的。

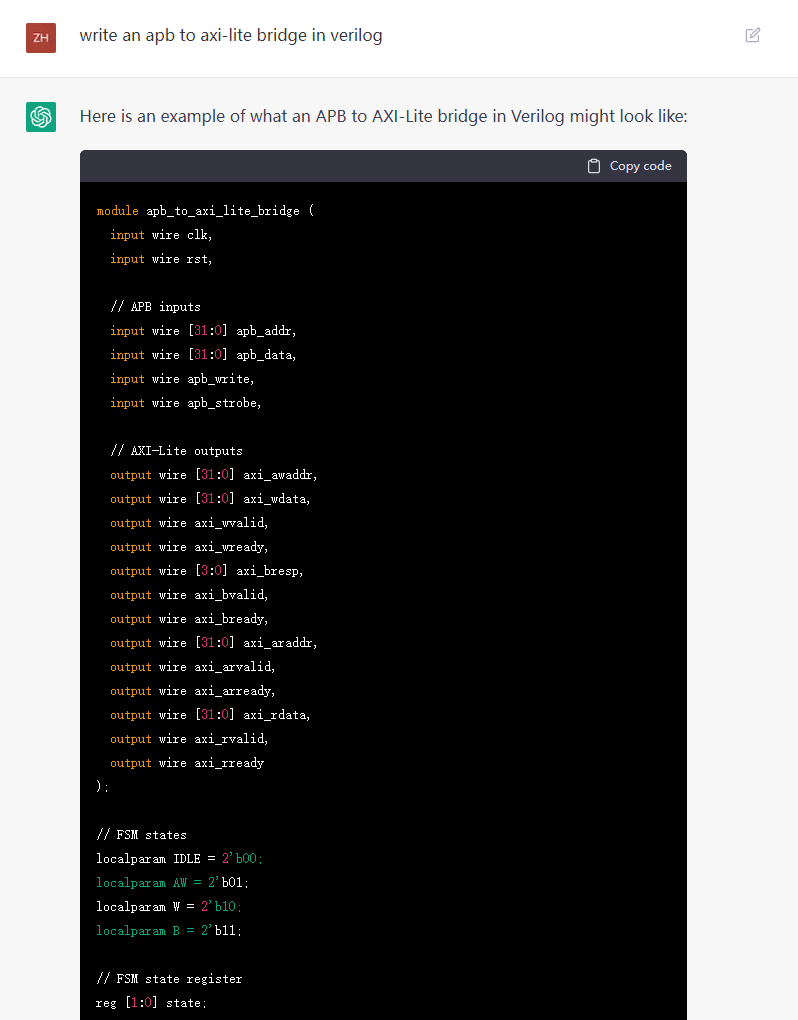

再写个稍微复杂一点但仍然是标准的协议:apb转axi-lite的bridge。

完整代码很长,我也并没有验过,但大概看下来,功能基本都有。

对于过于复杂的,就无能为力了,比如:以太网协议栈。

但有个更有意思的现象,当我第一次让它写以太网协议栈时,它提示太难了,写不出来。

把对话复位后,再让它写,它就会写一个大概的module,里面只有些接口,后面又复位对话后再重新让它写了,写出来的程序就更多了。

说明它的学习能力一直在增长。

可能现在它的功能还并不是很完善,但作为工程师,看到这么强大的功能,不禁有些感慨,我们的核心竞争力是什么?如果真的有一天,AI可以帮我们写代码了,我们该去做什么?

(抖个机灵:是不是到时候只需要验证工程师了?)

最后补充一点,这个网站的注册是需要一个国外的手机号,可能很多人弄不到,所以,如果你有什么有趣的功能想尝试,可以跟我联系,我来帮你试。

-

Verilog

+关注

关注

28文章

1351浏览量

110090 -

AI

+关注

关注

87文章

30844浏览量

269001 -

代码

+关注

关注

30文章

4786浏览量

68568 -

ChatGPT

+关注

关注

29文章

1560浏览量

7631

发布评论请先 登录

相关推荐

用AI来写Verilog代码能行吗

用AI来写Verilog代码能行吗

评论