现代芯片发展的方向是什么?

这是一个很大的问题,可以从多个角度去回答。如果从应用端去而言,那就是数智化,囊括了大数据、云计算、物联网、AI、5G及自动驾驶等创新方向。数智化芯片有两大明显的特征,功能更复杂以及对安全性要求更高,这就对芯片验证提出了更大的挑战。

芯片验证的评判标准——覆盖率

在数智化和摩尔定律等多重因素的推动下,当前的芯片功能越来越强大,内部结构也越来越复杂。回顾今年1月份刚刚发布的苹果M2 Max芯片,内部集成了670亿个晶体管,用以实现强大的CPU(12核CPU)、GPU(38核GPU)和内存系统(96GB内存和更大的L2缓存)等功能。

苹果M2 Max芯片当然是一款非常强大的产品,然而让数百亿个晶体管像人体细胞一样组成器官,然后再整体配合正常工作可不容易,因此要对功能模块和IP进行充分验证。我们都知道,这需要通过EDA工具完成芯片验证,包括架构设计、软件仿真、硬件仿真和原型验证等。

高效的验证工具能够从两个维度帮助芯片设计公司。一是降低成本,实现一次性流片成功。下一代先进SoC将采用3nm制程,根据市场研究机构International Business Strategies(IBS)的数据,3nm芯片的设计费用约达5-15亿美元,流片失败的损失将是巨大的。

其二是缩短研发周期。随着终端产品迭代速度提升,芯片成为一个真正的“风口”属性产品,需要在特定的时间周期内推出并满足市场需求,一旦延后也就失去了这颗芯片的价值。根据行业经验,验证在典型SoC项目中的工作量占比约70%。

验证的目标是获得无BUG的RTL(Register Transfer Level,电路寄存器传输级)代码,也就是在流片前的验证环节里,确保IP功能正确以及IP和功能模块的系统性功能正确。高昂的工艺成本已经不允许SoC在流片后才发现系统微码无法解决的BUG。

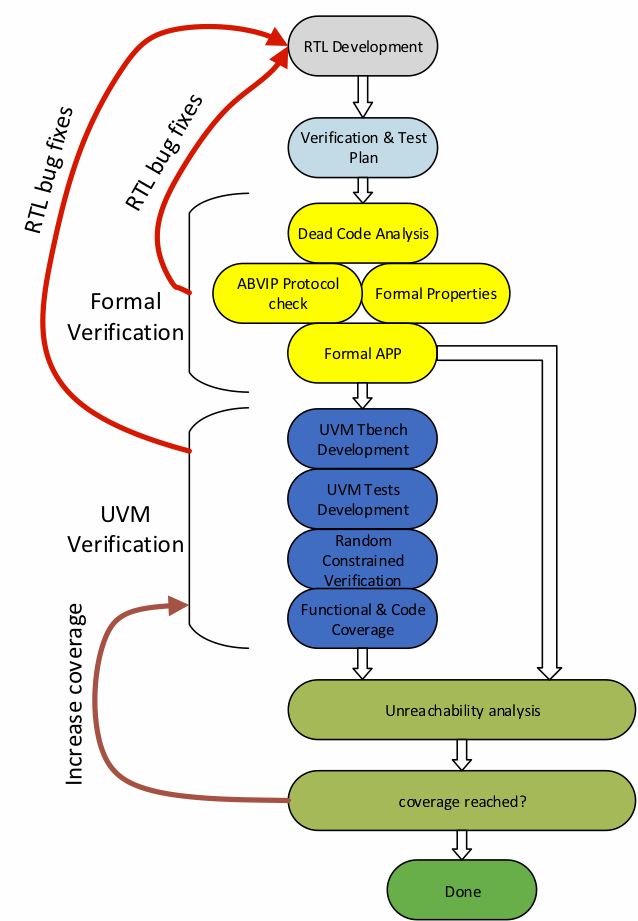

为了达到这一目的,芯片验证无论是从方法还是方式上都在积极创新。比如,UVM验证需要构建平台和测试用例,然而测试用例难以覆盖所有的边界情况,这样引入Formal工具的价值便体现了出来,能够以类似穷举的方式快速且全面地找到隐藏的BUG,那么就可以将有Formal工具的模块剥离出来,能够显著降低测试用例的复杂性。

图2:IP新的验证流程示意图

(图源:How formal verification saves time in digital IP design技术博文,作者:DAVID VINCENZONI )

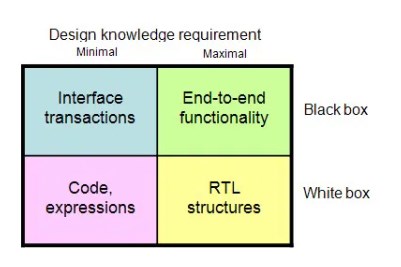

这就引出了一个当前验证的主流基准——覆盖率,包括功能覆盖率和代码覆盖率。其中,功能覆盖率是通过编写covergroup和coverpoint去覆盖数据、地址和控制信号,寻找在用户想要的全部功能中是否有代码遗漏;代码覆盖率包括断言(assertion)、行(line)、状态机(FSM)、分支(branch)、表达式(condition)和信号翻转(toggle),目标是评估代码质量,包括查看代码完整性以及去除不必要的冗余。

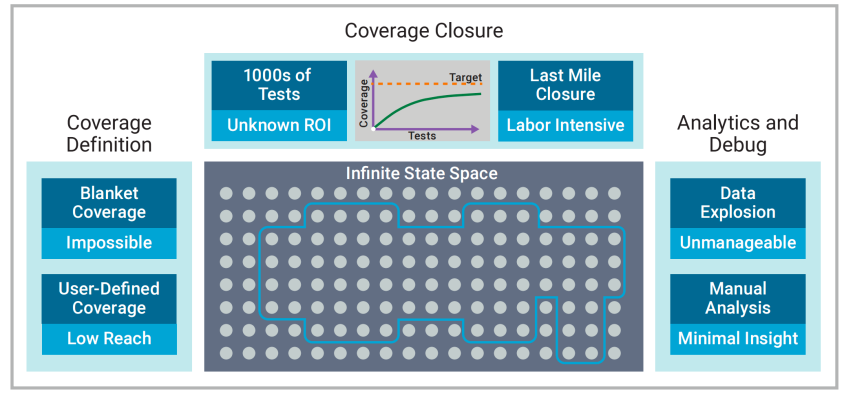

提升覆盖率是个体力活

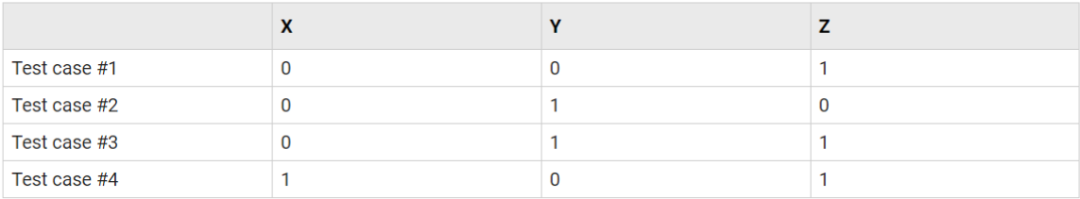

虽然基准和核心目标很清晰,不过基于传统的EDA工具去提升覆盖率还是会遇到很多方面的挑战。如下图所示,在仿真(simulation)验证中,需要做到功能覆盖率和代码覆盖率的结合,当功能覆盖率和代码覆盖率都达到100%时,验证工作结束。不过,在实际芯片验证过程中,代码覆盖率中的表达式和信号翻转类型很难达到100%,状态机类型也可能出现这种问题,因为很多状态之间并不存在相互关系;功能覆盖率理论上是要将具体功能细化到一个个不可分割的小点,然后编写coverpoint进行覆盖,不过功能分割和测试用例没有通用标准,基本主要依靠工程师的个人经验、认知以及思维逻辑。这就导致,仿真工具收集数据进而得到的覆盖率报告存在一定程度的不足。

图3:仿真验证中的覆盖率挑战(图源:新思科技)

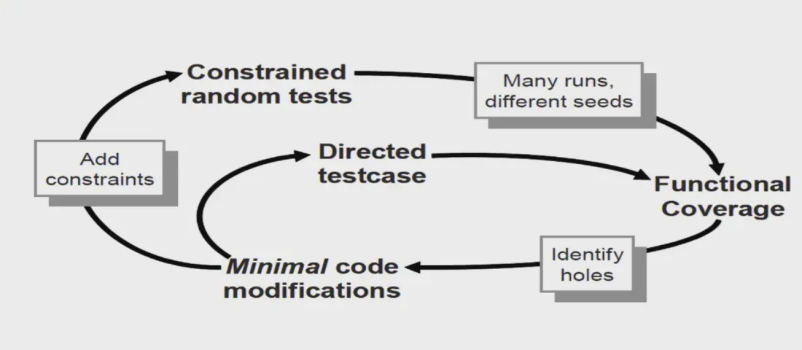

为了实现待测设计的覆盖率达标,往往首次拿到覆盖率报告后,功能覆盖率只是覆盖了立项中最主要的一些功能。如上图所示,很多代码结构并没有被触发过。那么研发人员就需要走下图里的外围路径,也就是重做测试用例,对现有用例的随机约束、callback机制等进行手动调整。

图4:功能覆盖率的反馈回路(图源:西安电子科技大学)

看起来上图中也只是增加了一条测试用例的路径,但实际上是一个需要经过多轮次往复的工作流,虽然目前有很多加速覆盖率收敛、回归的工具可以使用,但这个过程依然会耗费大量机器、人力和时间等宝贵资源。

更具挑战性的是,当覆盖率回归测试到达“最后一公里”阶段时,往往经过很多轮修改都无法获得更好的覆盖率收敛,验证工程师有时候会在这个环节陷入覆盖率分析和用例调整的“迷宫”,有时候甚至需要回归到最开始的功能点划分或者增加RTL代码并重新运行回归以验证错误是否被修复。

更糟糕的情况是,当覆盖率达到100%依然存在新的设计漏洞,这个时候就证明是存在明显的功能覆盖率缺失,也就是用例配置错误。有研究发现,当回归测试的代码覆盖率达到90%时,平均只有54%被监测,因此需要高质量的用例来找到剩余代码的漏洞。这就是为什么我们强调,对于功能覆盖率来说,验证人员自身经验非常重要。

实际上,上述这些内容主要是从测试质量(QOR)和测试时间(TTR)角度来考虑。作为验证工程师,还需要关注达成结果所需的成本(COR),随着芯片复杂度提升,增加验证工程师和运算服务器都会增加额外的成本。并且,每次芯片改版(re-spin)都会带来不小的成本增加。

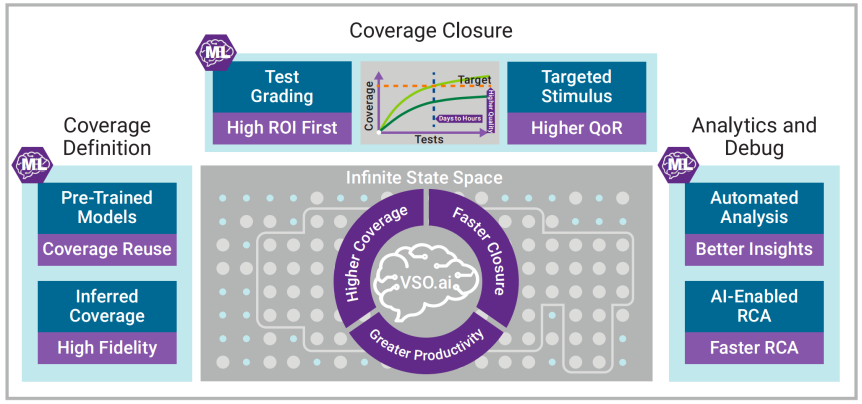

VSO.ai用AI驱动验证

在人类验证工程师的经验成为芯片验证的明显瓶颈时,产业将希望寄托于人工智能(AI)。AI,尤其是机器学习(ML)最大的魅力就在于能够在迭代循环中不断成长,并基于大数据发现代码中难以察觉的错误,进而实现更快速、更高质量的覆盖率收敛。

VSO.ai作为新思科技推出的全新一代VCS工具中用于覆盖率提升的一项技术,提供业界首个人工智能驱动的验证解决方案,帮助验证团队更快、更高质量地实现覆盖收敛。

图5:VSO.ai对仿真覆盖率的改进(图源:新思科技)

VSO.ai能够从三个方面给验证工程师带来非凡的助力:

首先是实现更快的覆盖率收敛。对于验证工程师而言,覆盖率并没有具体的指标,并存在大量的重复性工作,因此手动进行回归优化的效率非常低,对给定设计进行上万次测试是很常见的。VSO.ai可执行粗粒度基准测试,提供自动化的、自适应的测试优化。在运行过程中,VSO.ai会率先运行具有最高ROI的测试,同时消除冗余测试,从而加速覆盖收敛并节省计算资源。

其次是实现更高的测试质量。如上所述,由于传统工作流中功能覆盖率主要依赖验证工程师的经验,导致很多时候覆盖率收敛的效果很差。VSO.ai也可执行细粒度的基准测试,通过调整随机约束激励来针对未被验证的覆盖点,自动发现测试覆盖率中难以捉摸的错误,进而提升测试质量。

第三点是攻克“最后一公里”的验证难题。在验证的最后阶段,过往验证工程师的手动调整到这个时候覆盖率收敛和ROI都会显著降低,原因在于此时验证工程师对已获取的验证大数据所具有的洞察力和分析能力已经很低。VSO.ai可执行根本原因分析(RCA),以确定为什么没有达到特定的覆盖点,通过AI解决最后的难题。

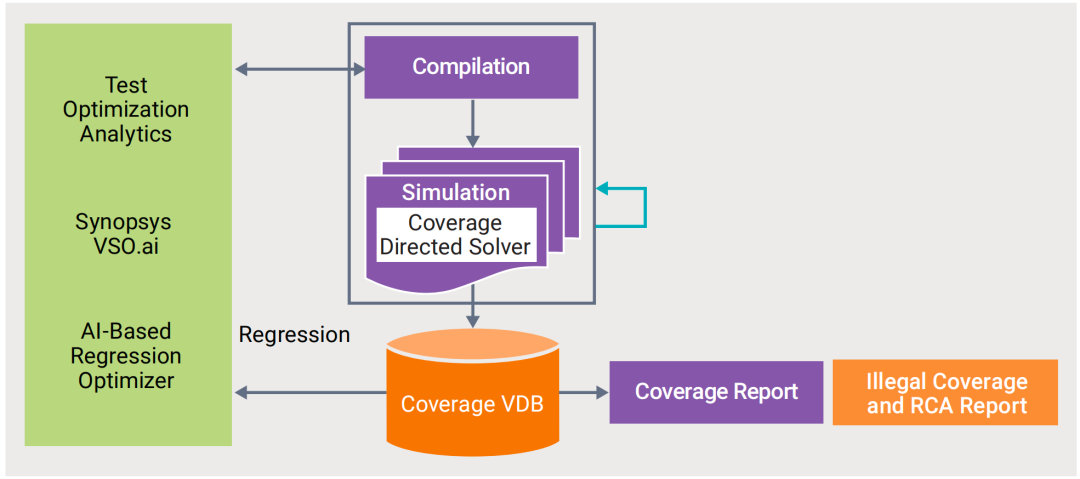

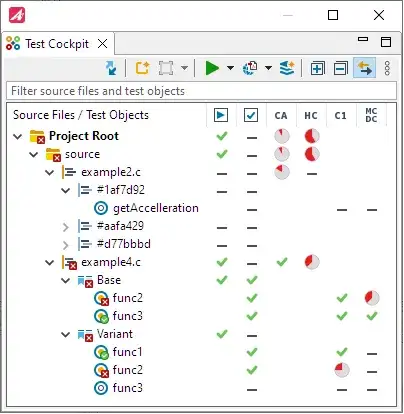

当前,AI要在EDA领域发挥作用,依然需要融入到传统工具中,VSO.ai也不例外,因此工具的可集成特性是非常重要的。如下图所示,VSO.ai可以轻松集成到现有的新思科技VCS(R)回归环境中,而无需对设计或测试平台进行任何代码更改。

图6:使用同步系统VSO.ai的仿真测试流程(图源:新思科技)

对于芯片验证而言,一旦设置了芯片设计的RTL并配置了设计状态空间,验证过程就开始了。VSO.ai在工程师编译设计时就开始介入,它会自动识别和编排测试,用自动生成的覆盖率来替代工程师编写的代码覆盖率和功能覆盖率融合设计,以最大限度地减少用户选择的目标函数,例如回归CPU时间、测试运行次数、模拟周期或每秒周期数。

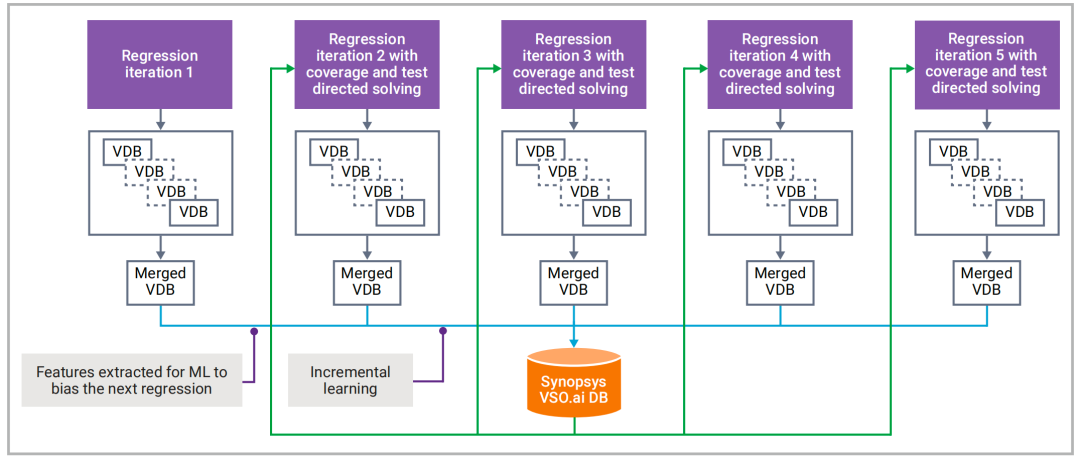

如下图所示,在整个仿真测试流程中,每一次运行VSO.ai都能够提供新的信息来改进约束求解和优化回归测试。验证工程师在此过程中可以灵活设置自己的覆盖率目标,比如验证工程师如果并不需要更高的覆盖率,那么VSO.ai产生的覆盖率就可以少得多。

图7:VSO.ai如何使用ML来改进回归分析(图源:新思科技)

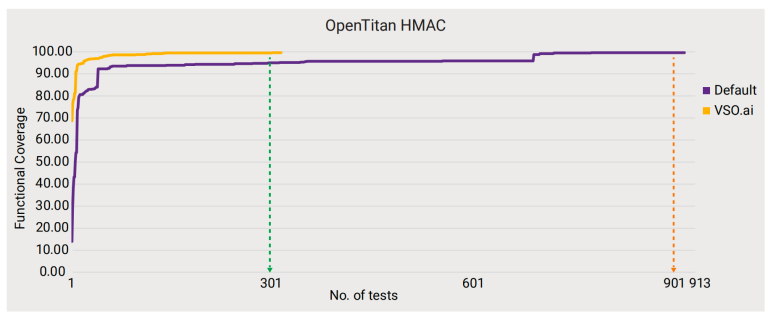

综上所述,新思科技VSO.ai是一套自主工作系统,用以替代验证工程师负责的编译设计和编排测试等工作,以尽可能快、尽可能低开销地达到覆盖率目标,并获得最高质量的验证结果。比如,在OpenTitan HMAC这款IP验证示例中,VSO.ai在实现100%功能覆盖率的速度上是传统方案的3倍。

图8:OpenTitan HMAC同步系统中VSO.ai的验证效果(图源:新思科技)

VSO.ai的典型应用

在实际应用中,验证IP功能是VSO.ai的一个典型场景。日本芯片厂商瑞萨科技共享研发核心IP部门开发总监Takahiro Ikenobe表示,“由于设计复杂性的上升,芯片设计使用传统技术来满足质量和上市时间的限制正在变得困难。使用Synopsys VSO.ai的人工智能驱动验证,我们在减少功能覆盖率缺陷方面取得了高达10倍的改进,IP验证生产率也提高了30%,这表明人工智能有能力帮助我们应对日益复杂的设计带来的挑战。”

根据新思科技方面给出的数据,VSO.ai既可以扩大目标覆盖面,又可以加快IP验证过程,可以实现IP 99%的覆盖率。

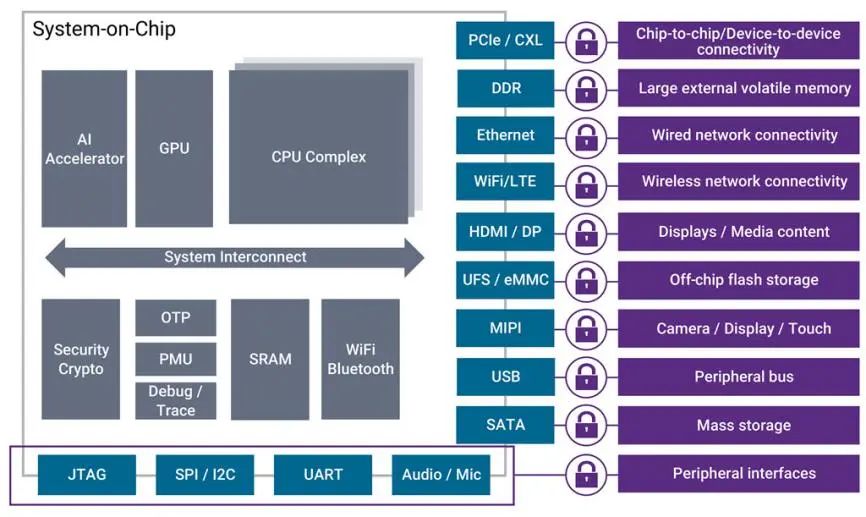

IP验证是SoC芯片验证的重要一环,特别是在数智化趋势下,接口IP的安全性和芯片本身的安全性直接挂钩。如下图所示,SoC上需要确保安全性的接口非常多,包括DDR、PCIe、CXL、以太网、MIPI、USB、UFS等。

图9:SoC上需要确保安全性的接口(图源:新思科技)

为什么VSO.ai能够给IP验证带来如此巨大的提升呢?答案在于新思科技长期以来都在深耕安全接口。新思科技安全接口的优势在于其涵盖了开发者在HPC、移动、物联网和汽车等各种不同应用中需要考虑的所有接口。因此,新思科技的安全接口IP不仅在SoC设计中被广泛应用,同时对安全接口IP设计和应用的理解也领跑全行业。庞大的应用数据基础加上出色的行业理解,促成了VSO.ai在IP领域的高效表现。

结语

当前,AI已经逐渐渗透到EDA工具的每个工作流程中,让芯片设计工程师和验证工程师从反复循环的工作中解脱出来,能够专注于创建差异化的IP和SoC系统。随着工艺水平提高,以及终端应用迭代速度加快,AI在芯片验证中正如一场及时雨,为这项复杂工作节省时间的同时,也带来了更好的成本优化。相信随着AI+EDA融合逐渐深入,芯片验证这个“拖后腿”的毛病也能够被治愈,让我们拭目以待。

审核编辑:刘清

-

EDA工具

+关注

关注

4文章

268浏览量

31981 -

soc

+关注

关注

38文章

4218浏览量

219274 -

晶体管

+关注

关注

77文章

9796浏览量

139067 -

芯片验证

+关注

关注

5文章

34浏览量

47295

原文标题:AI+EDA,提升芯片验证覆盖率的利器

文章出处:【微信号:Rocker-IC,微信公众号:路科验证】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

英诺达发布全新静态验证产品,提升芯片设计效率

ADS1281怎样评判采集到的结果是否准确?

常见的波特率标准和协议

synopsys 的design ware:DW_fpv_div,浮点数除法器,默认32位下,想提升覆盖率(TMAX),如果用功能case去提升覆盖率呢?

物联网系统高速率WiFi传输方案_WIFI芯片详解

利用静态检查工具完善功能安全中测试覆盖率

对于一个放大电路如何评判它的指标性能好坏?

2025年智能水表将覆盖全北京!超声波测量技术助力智能水表实现全天候高精度流量监测

单元测试工具TESSY 新版本亮点速览:提供测试驾驶舱视图、超级覆盖率、代码访问分析、增强覆盖率审查

如何将SystemVerilog断言属性和覆盖属性置于在设计上?

芯片测试和芯片验证的区别

如何选择IP DV与SOC DV

AI(VSO)赋能的VCS验证流程

芯片验证的评判标准—覆盖率

芯片验证的评判标准—覆盖率

评论