12为什么静态线远端会出现近端串扰噪声

上一篇文章讲到,从动态线耦合过来的噪声会在静态线的近端产生近端耦合噪声,同时在静态线的远端产生远端耦合噪声。不过现实中,在静态线的远端也存在近端串扰噪声,这是为什么呢?

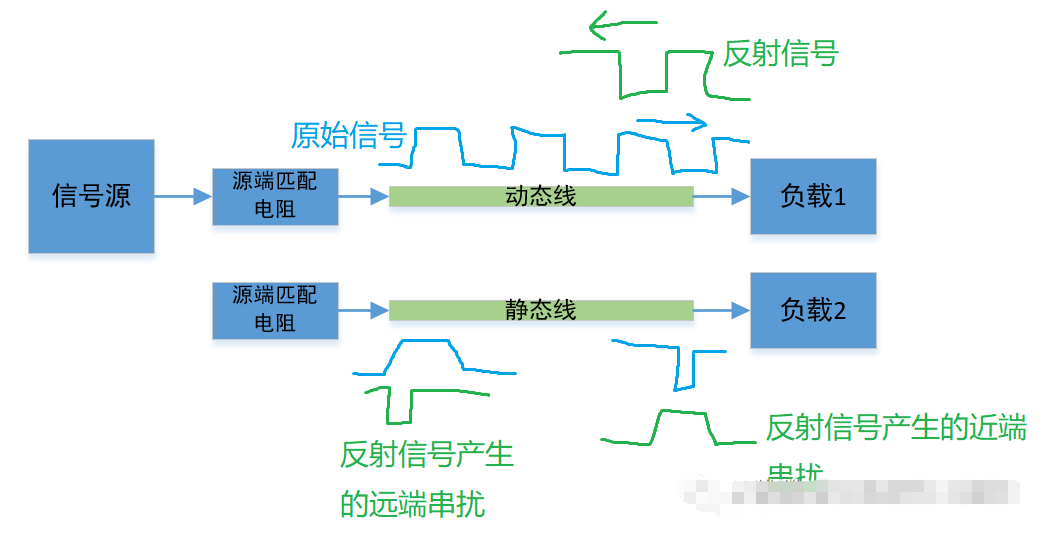

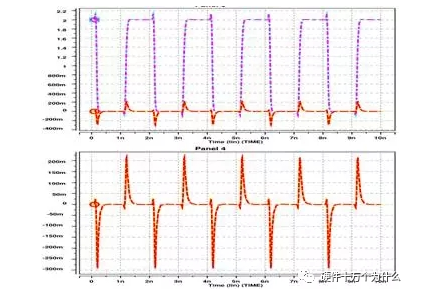

如下图。蓝色信号是从动态线近端,通过传输线发送到负载1。在信号传输的过程中,在静态线产生蓝色的近端串扰信号和蓝色的远端串扰信号。当蓝色信号到达负载1时,会有些许的反射信号(绿色信号)从负载1传回到信号源。这些反射信号在静态线同样会产生串扰信号,如图中绿色的近端串扰信号和绿色的远端串扰信号。这个反射信号产生的近端串扰信号就位于静态线的远端,即负载2。因此负载2处的串扰是蓝色远端串扰和绿色近端串扰的组合,只是它们的源头不同。

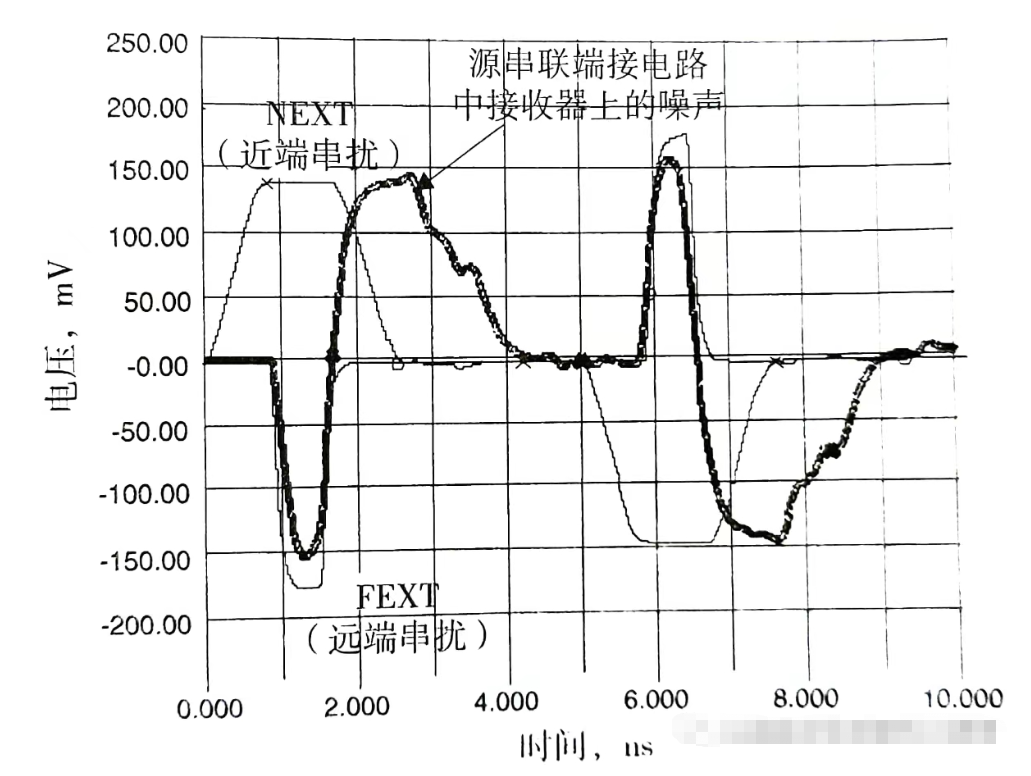

如下图中,细线分别是标准的近端串扰波形和远端串扰波形。粗线是在负载2上得到的串扰噪声,可以看到包含了近端串扰波形和远端串扰波形。

13多条动态线对同一条静态线的影响

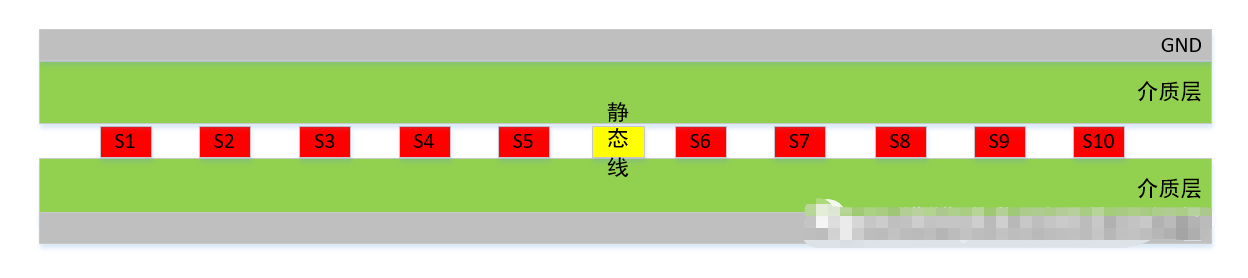

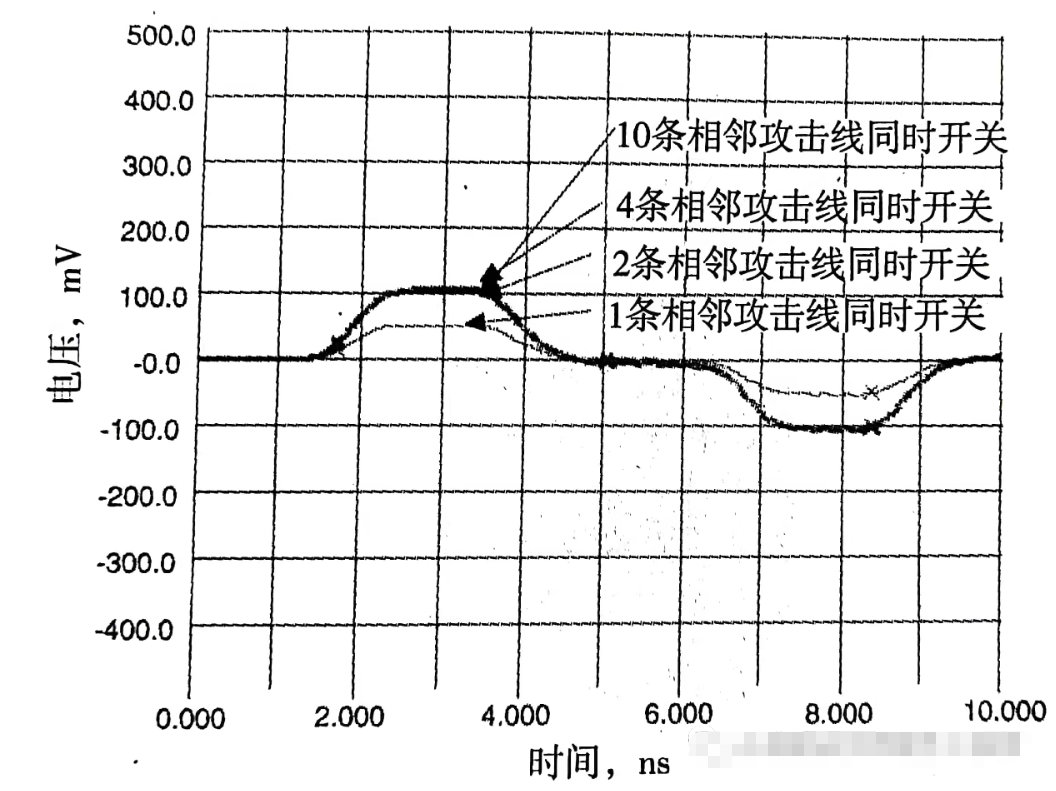

在一个比较复杂的系统中,同一条静态线可能会有多条动态线对其影响,每一条动态线都会在静态线上产生噪声。下图是一个案例,有11条线宽和间距都是5mil的50欧姆带状线。最中间那条黄色的是静态线,其他是动态线。动态线上有幅度为3.3V,频率是100MHz的信号通过。

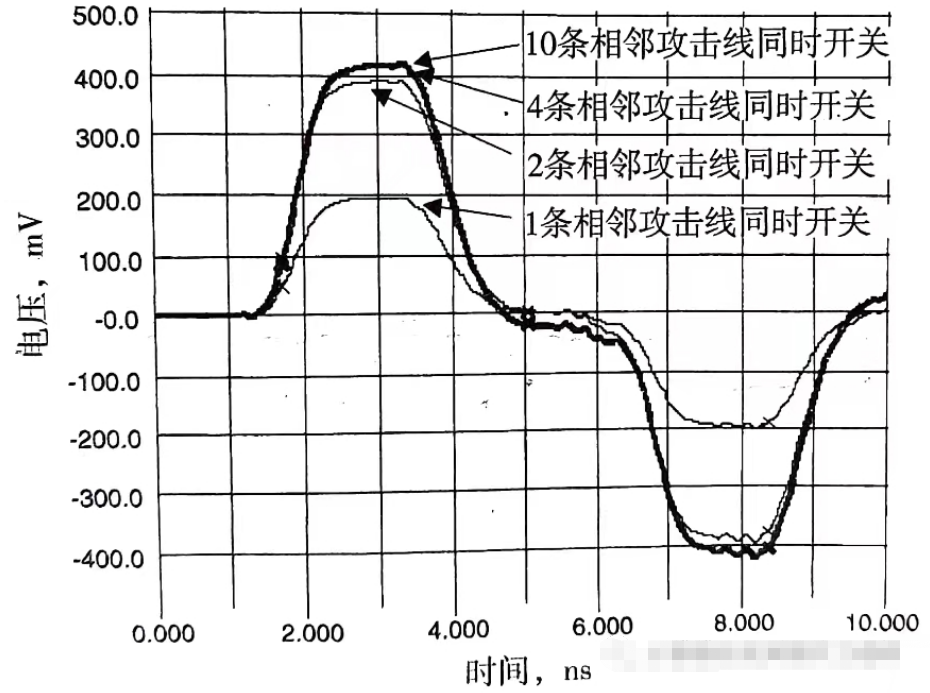

下图是:分别当1根动态线上有信号、2根动态线上有信号、4根动态线上有信号、10根动态线上有信号时,静态线上的噪声波形。可以看出2根动态线信号引起的噪声接近1根动态线信号引起噪声的2倍。而后即使增加到10根动态线都有信号,对噪声幅度的影响也不是很大。所以静态线左右临近的动态线对噪声幅度影响最大。其他稍远点的动态线对噪声的影响很小了。以本图的数据看,当10根动态线都有信号时,靠近静态线最近的左右两根动态线带来的噪声占据全部噪声的95%。这也提示我们在进行串扰仿真时,选择静态线附近的2根动态线,至多选择4根动态线就足够用了。

注:因为是带状线,因此基本没有远端噪声,上图波形只是近端噪声。

接下来,针对上例,保持线宽为5mil,线间距增加到10mil(即3W布线),看看结果是什么。

可以看到2个结论。

一个是整体的噪声幅度在下降。之前线宽等于线距时,串扰系数是400mv/3.3v=12%。执行3W布线后,串扰系数下降到100mv/3.3v=3%。换句话说,PCB设计保持3W原则,只有3%的串扰噪声会到达静态线。

另一个是2根动态线和10根动态线的影响差不多,即在进行3W布局后,所有的串扰噪声都可以说是由距离静态线最近的2根动态线带来的,其他更远的动态线可以不用考虑其影响了。

14在动态线和静态线之间增加防护线

(一)各种端接的防护布线对噪声的影响

上述增加动态线和静态线间距(3W原则)是一种降低串扰噪声的办法。之前还提到过尽量使用带状线设计是另一种降低远端串扰噪声的方法。除此之外,在动态线和静态线之间增加防护线也是一种方法。当信号在动态线上传输时,它会将噪声耦合到防护线上,防护线上的这些噪声再耦合到静态线上。防护线影响了动态线和静态线之间的电场和磁场,最终使耦合电容和耦合电感减小。

通常执行3W原则后,可以将串扰噪声降低到3%左右。但是在有些设计中,对此要求更高。例如在射频接收单元,要求它与数字信号的隔离度能达到-100dB,也就是串扰噪声系数在0.001%。通过在动态线和静态线之间增加防护线,有机会将串扰噪声降到更低。

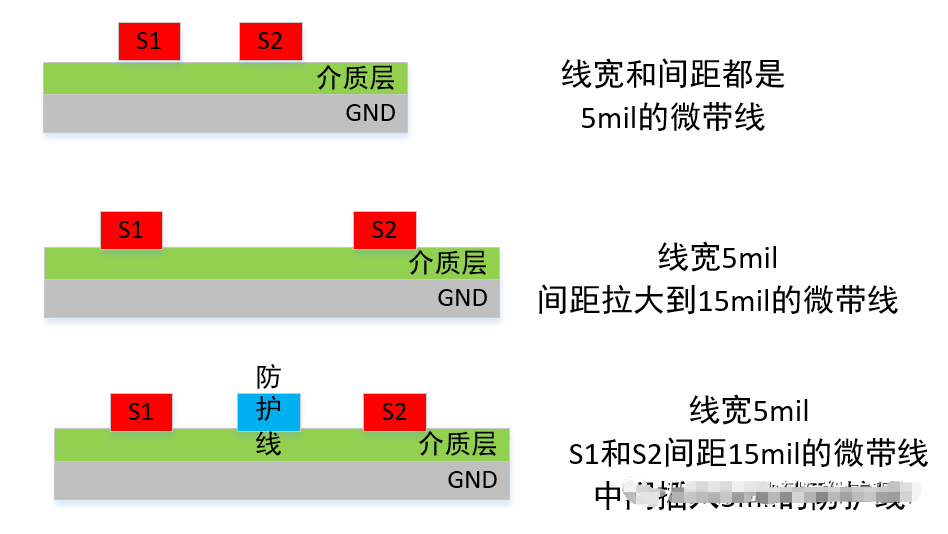

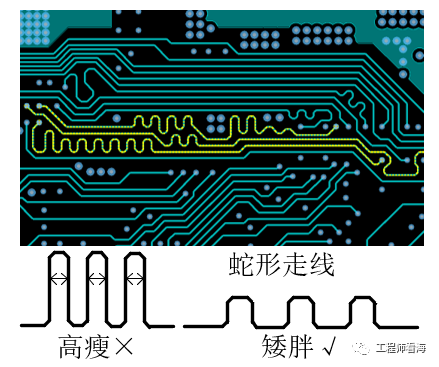

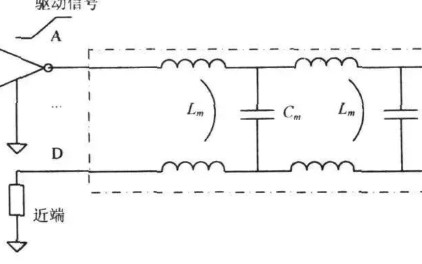

一般防护线应该尽量宽,这可以增大动态线和静态线之间的距离。在微带线和带状线中都可以插入防护线。不过在微带线中加入防护线的效果不是很明显。除了防护线的宽度、距离,防护线两端的端接方式也对串扰隔离有影响。常见的防护线端接方式有开路、短路、端接匹配电阻。下图是一个例子。针对以上几种情况进行讨论。

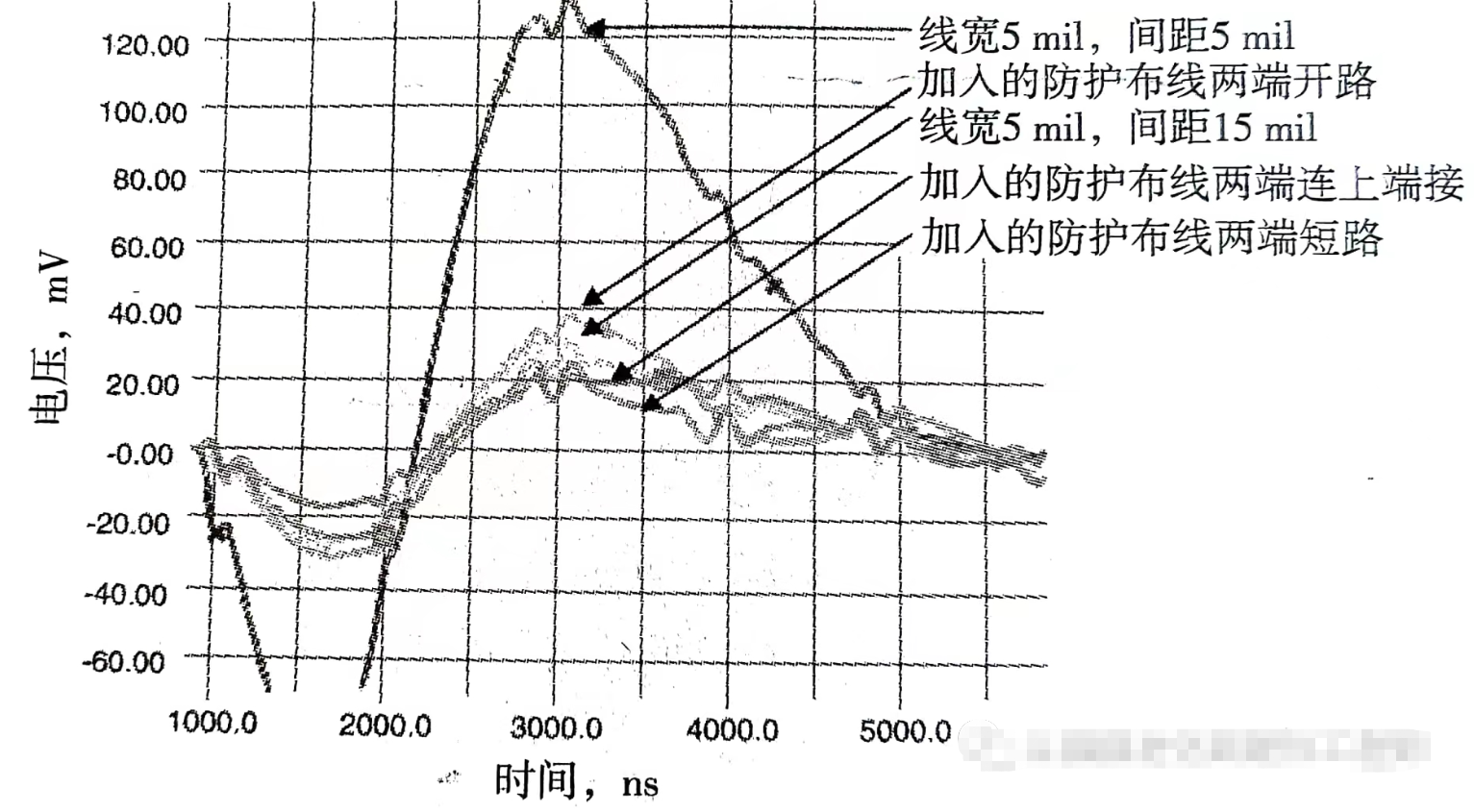

看不同配置下的波形:当动态线信号幅度为3.3V时,不同配置下的静态线噪声是:

①线宽和线距都是5mil时,噪声幅度130mV

②线间距拉大到15mil时,噪声幅度39mV

③插入一条两端开路的5mil防护线时,噪声幅度接近40mV

④插入防护线两端端接50Ω电阻时,噪声幅度接近25mV

⑤插入防护线两端短路时,噪声幅度接近22mV

因此就结果看,增加动态线和静态线之间的距离、插入两端短路的防护线,效果最好。为什么呢?

随着信号沿着动态线传输,噪声被耦合到防护线。①在防护线上的后向耦合噪声到达防护线近端的短路处并且发生反射,因为短路,反射系统是-1。所以防护线上后向传输的近端噪声和由它自己带来的前向传输的负反射近端噪声(因为短路造成)相互抵消,最终在防护线上的近端噪声会非常小,甚至消失。这样在防护线上就没有多少近端噪声再被耦合到静态线上了。②同样的在防护线上有前向耦合噪声向着防护线的远端传输,当到达远端时,因为防护线远端也是短路的,反射系数也是-1,远端净噪声也为零。

注:有些设计中,两端开路的防护线和没有防护线相比,会带来更多的耦合噪声。

(二)防护线沿线过孔的影响

防护线上的过孔间距(常见的是在动态线和静态线之间插入的GND线上打via)对噪声也有影响。因为防护线上的远端噪声只在过孔之间的区域产生。过孔间距越小,防护线上的最大远端噪声越小。过孔越多,防护线上的远端噪声越小。这意味着从防护线耦合到静态线的噪声也越小。其实这些过孔不直接影响动态线耦合到静态线的噪声,它们只是抑制防护线上的噪声幅度。

经验法则是:先计算动态线信号上升时间的空间延伸距离,而后在防护线上以此距离为单位,每单位至少打3个via。

例如:一个信号的上升时间是1ns,在FR4 PCB上信号速度是6in/ns,则空间延伸距离是6in。那么在防护线上每6in至少需要3个via。再举一例,如果信号上升时间是0.7ns,那么空间延伸是4.2in,则在防护线上每4.2in需要3个via,即每1.4in打一个via。

看起来随着信号上升时间越短,过孔间距也需要越小。由此需要考虑过孔数量和成本的平衡。其实在防护线上增加过孔数对静态线的噪声影响很小。

总之:当设计中对信号串扰要求很高时,优先走带状线,并且增大动态线和静态线距离,而且插入防护线,增大防护线间距。可以将隔离度降低到-160dB,即串扰噪声系数是0.000001%。

另外,防护线和静态线的距离会影响静态线的阻抗。通常防护线和静态线的距离在2倍线宽范围内,对静态线的阻抗影响很小。否则,需要通过调整其他参数得到合适的静态线阻抗。

还有一个信息:使用较小的介电常数材料,例如从FR4(介电常数4.5)换成聚酰亚胺(介电常数为3.5),可以在一定程度上降低串扰,只不过影响有限。同时为了保证传输线在介质材料变化后,仍旧保持在50欧姆目标阻抗,会缩小信号层和返回路径层之间的介质厚度。

15串扰带来的静态线上信号延迟

首先看带状线。发生在带状线之间的串扰,不会影响静态线上原有信号的速度,也即不会影响它的时序。

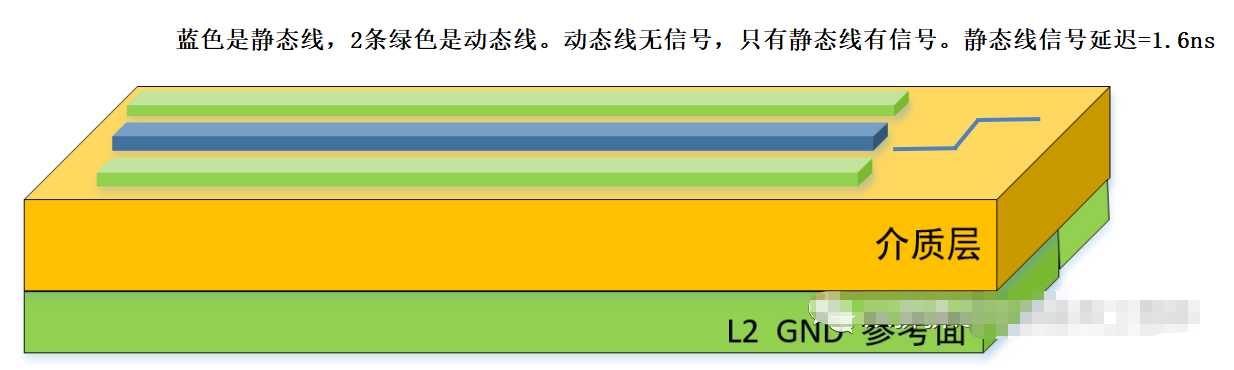

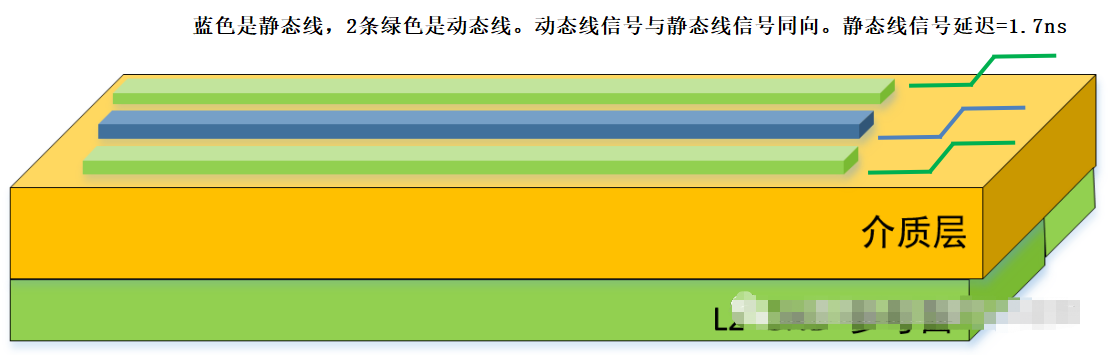

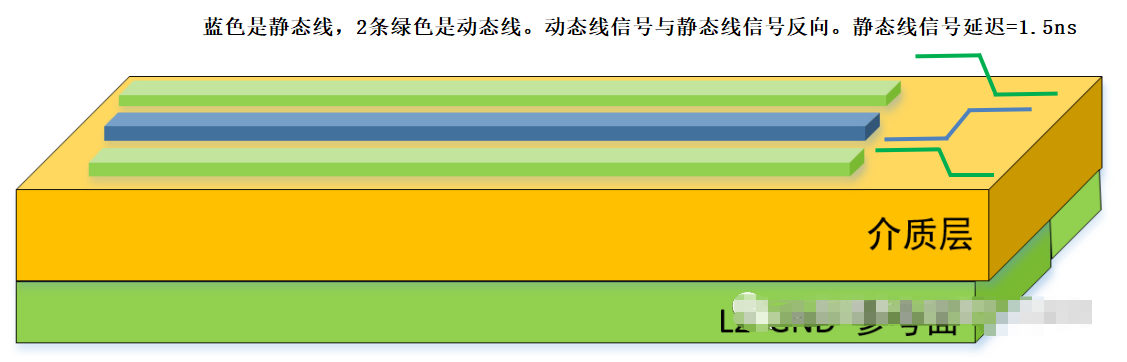

不过对于微带线,串扰对静态线上信号的速度和时序就有影响了。例如三根10in长的50Ω微带线,线和线间距是5mil。中间蓝色线是静态线,两边绿色线是动态线。动态线上没有信号时,静态线信号本身由于10in长度,造成延迟是1.6ns。动态线上有信号时,而且信号方向与静态线信号同向,静态线延迟会增加。动态线上有信号时,而且信号方向与静态线信号反向,静态线延迟会减少。

这是由于介质材料不对称(信号线下方是FR4,信号线上方是空气),和传输线之间电磁场不相同造成的。不过只有动态线和静态线之间的距离很近(例如1倍线宽),它们之间的电磁场重叠严重时,串扰才会影响静态线信号时延。

16非均匀返回平面带来的问题

当返回路径不是均匀平面,或者介质材料不均匀时(例如芯片封装内部、连接器和接插件上),回路互感中的感性耦合参数会变大。导致在和动态线信号dI/dt相对应的返回路径上发生地弹。只有减小传输线回路互感,才能将返回路径上的地弹降下来。有几个方法可以降低回路互感。

①减小回路长度,互感会减小。即选用小尺寸的连接器。

②增加信号线间距,互感会减小。不过这受到PCB尺寸限制。

③减小信号线和它自己的返回路径之间的距离。互感会减小。

17总结:降低串扰的方法

①增加动态线和静态线之间的间距

②使用完整的大平面作为返回路径

③动态线和静态线之间的耦合长度尽量短

④使用带状线布线

⑤使信号路径阻抗值在目标范围内偏下限。

⑥使用介电常数小的PCB介质

⑦动态线和静态线不要共用返回引脚,主要是在芯片封装内部和连接器中。

⑧使用两端和整条线上有短路过孔的防护线。

-

耦合

+关注

关注

13文章

589浏览量

101101 -

噪声

+关注

关注

13文章

1130浏览量

47603 -

信号完整性

+关注

关注

68文章

1418浏览量

95848 -

波形

+关注

关注

3文章

383浏览量

31747 -

串扰

+关注

关注

4文章

189浏览量

27064

发布评论请先 登录

相关推荐

常见信号完整性的问题之PCB设计串扰的原因与Altium Designer中的串扰消除技术

信号完整性之串扰(三)

信号完整性之串扰(三)

评论