蒋修国 /文

编者注:对于PCB layout工程师而言,绝大数的时候都局限于长度限制,等长,包地,过孔数量等等,其实,很多时候这些都不是一成不变的,换个角度,会有不一样的结果。

有一位微信好友问我:他们的PCB板上的USB3.0布线长度超标了200mil,在他们的产品上有没有风险?对于这类反手就给了一个回复:你猜!!!当然,这不太符合一位SI工程师的作风,一般要回复他一句至理名言:It depends!

当然,话是这么说,其实这个问题的根源在于很多工程师并没有特别理解“传输线长度标准范围”的这一概念。

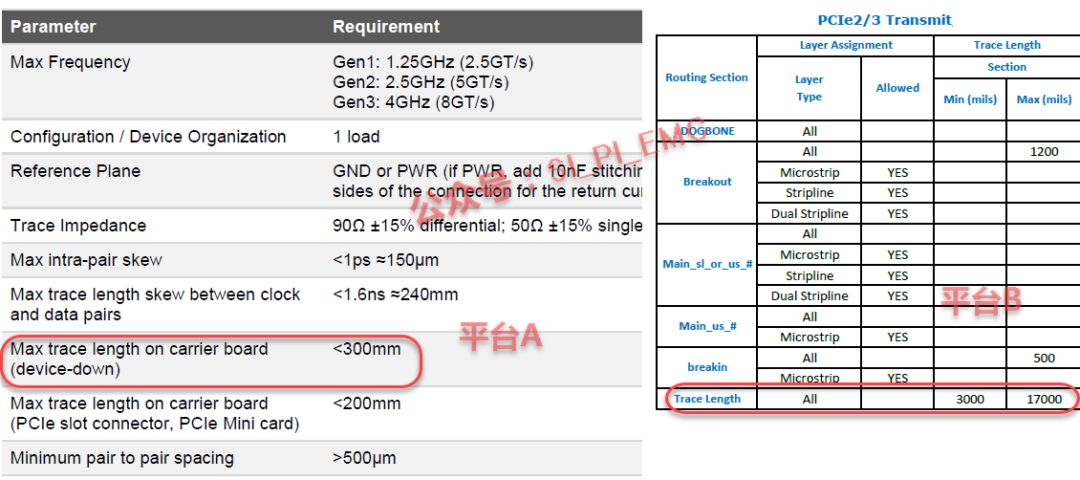

翻遍各类总线规范,基本找不出总线对长度的定义,那么这些长度的标准又来自于哪里呢?当然,大概归纳起来就两个来源,一个是芯片设计手册,所谓的designguide;另一个来源就是本公司(或者个人)的经验。但是,不管是哪一种,都会在一些不相同的应用场景时,存在一些偏差。比如如下是两个不同平台的设计手册针对PCIE3.0的要求:

显然,平台A最长只能12inch,而平台B的可以达到17inch。所以如果工程师把B平台的规则放到A平台上,这就会导致长度超标,最终有可能导致产品设计失败。而如果把A平台的规则放置到B平台上进行设置,虽然功能可能可以调试出来,但是如果非得要设计到17inch的长度,就会导致成本增加。

回到开始的那个问题,之所以会那样回答,就是因为在什么都不清楚的情况下,只能像算八字一样掰着手指算一算就猜。

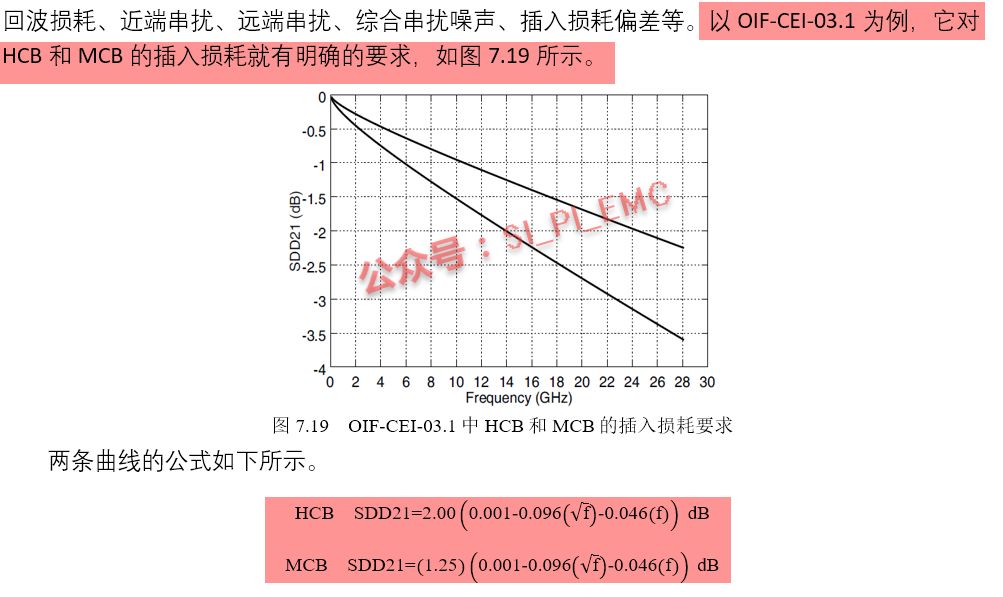

那规范中这些长度是如何给出来的呢?为什么每一个芯片平台又不一样呢?这其实就与每一颗芯片的驱动能力有关。所以我们在一些总线规范中会看到有对总线的损耗有一个要求,在《ADS信号完整性仿真与实战》一书中也有给大家介绍到这个问题。如下图所示:

规范中定义了这个损耗,在设计的时候产品的时候,就按照这规范以及实际电路的设计来确定PCB设计的长度等,这里要补充说明下,损耗不仅仅与长度有关系。这时就通过仿真能快速地获得这个设计的长度要求,从而得出设计的规则。

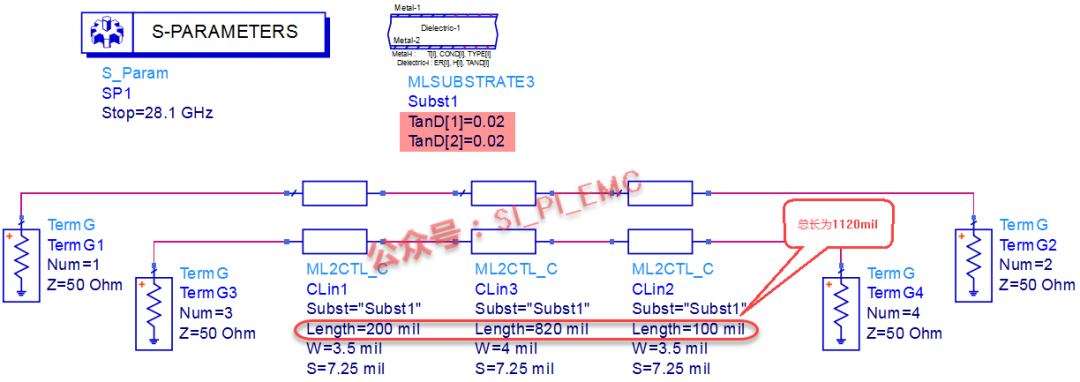

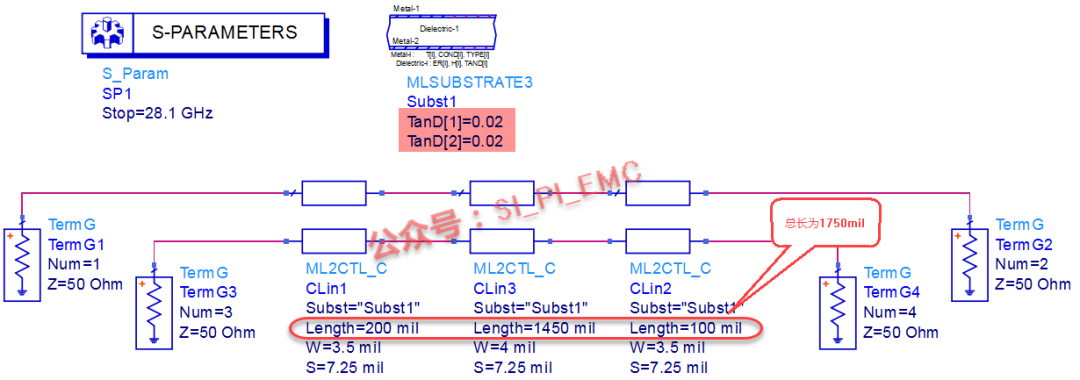

下面以HCB的要求为例,通过仿真来简单介绍下。在仿真工具(ADS)中建立一个仿真模型,如下图所示,传输线的总长度为1120mil,PCB材料的介质损耗角为0.02:

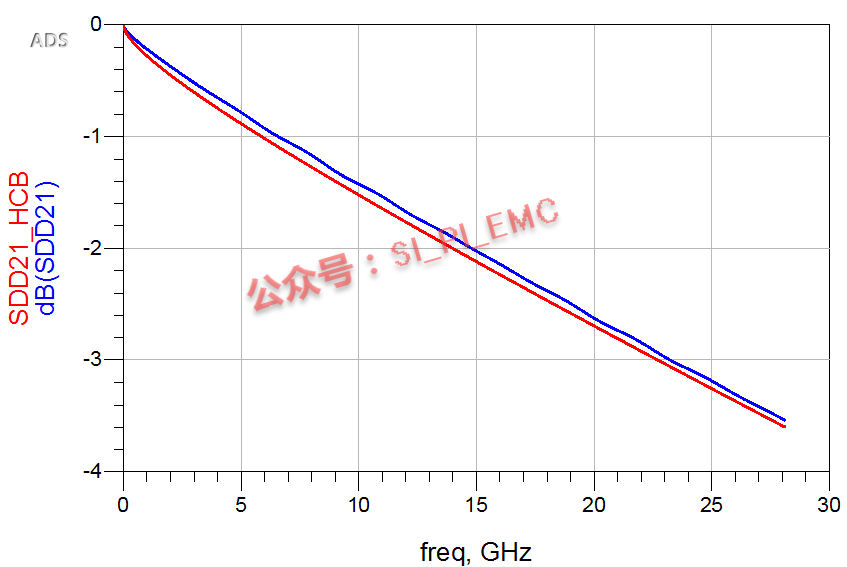

仿真得到的结果如下图所示,红色的曲线为规范要求,蓝色的曲线为传输仿真获得的结果。

显然,这时传输线的总长度为1120mil是符合要求的。那当长度变为1750mil时,我们看看结果会变成什么样呢?

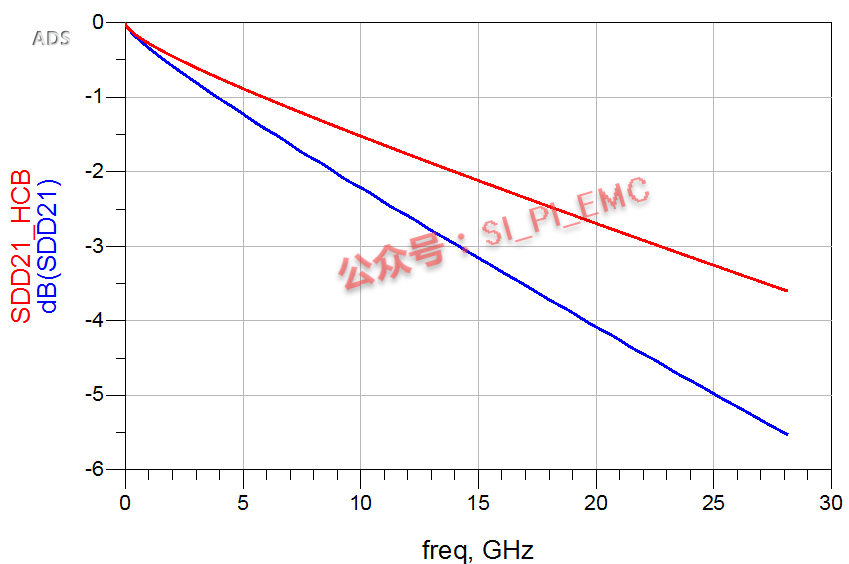

仿真得到的结果如下图所示,红色的曲线为规范要求,蓝色的曲线为传输仿真获得的结果。

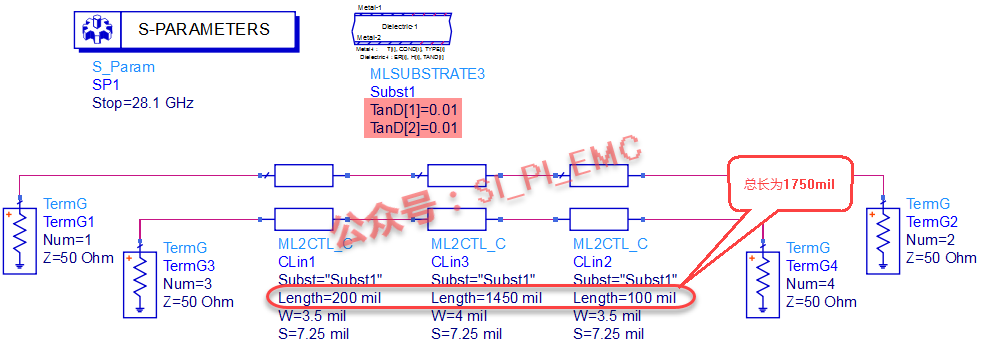

从上面这个结果可以看到,这个长度的损耗远远超过了规范要求的数值。这样设计出来的产品肯定是不符合设计要求的。所以到这里,可能很多工程师就会说这个长度太长了,显然不能满足设计要求。结果真是这样的吗?如果把PCB材料的介质损耗角变为0.01时,长度还是为1750mil,如下图所示:

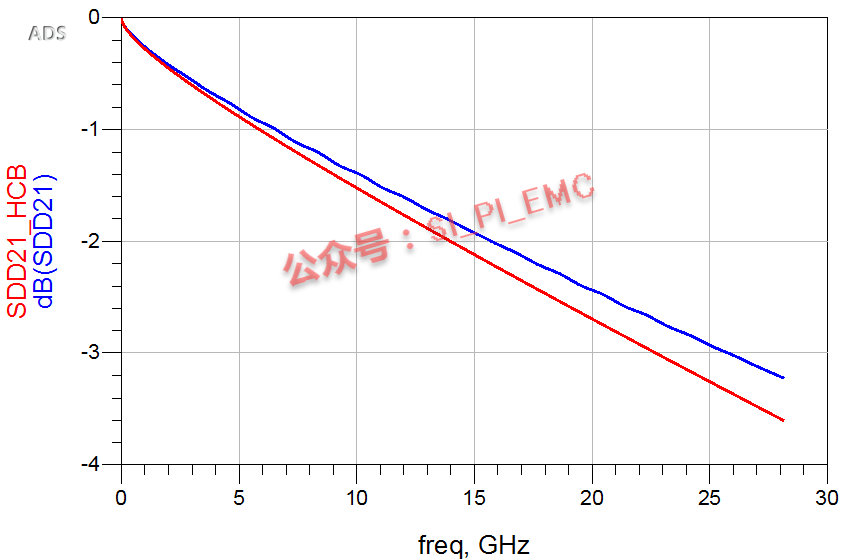

仿真得到的结果如下图所示,红色的曲线为规范要求,蓝色的曲线为传输仿真获得的结果。

从以上结果我们可以看到显然,即使长度变长了,只要改变PCB材料参数,结果同样也是符合规范要求的。

综上所述,在不同的条件下,不管传输线的长度是1120mil还是1750mil,它们都有可能满足规范或者设计系统的要求。所以我们不能单一地以某一长度来作为设计的准则,而是要根据实际设计的情况来确定。通过对实际情况的了解,通过建模仿真,就可以打破一些设计规则的约束,从而获得符合自己特定场景的应用。

当然,并不是所有的规范都有一个非常明确的损耗要求,如果没有这个损耗要求的时候怎么办呢?大家可以在留言区说说你们的看法,后续我会再与大家分享。

审核编辑:汤梓红

-

pcb

+关注

关注

4319文章

23108浏览量

398203 -

PCB设计

+关注

关注

394文章

4690浏览量

85738 -

总线

+关注

关注

10文章

2887浏览量

88128 -

Layout

+关注

关注

14文章

405浏览量

61819 -

传输线

+关注

关注

0文章

376浏览量

24040

原文标题:传输线长度长了一点行不行呢?

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

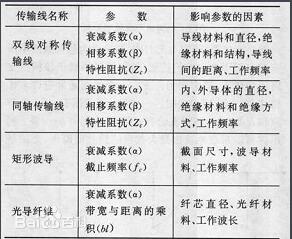

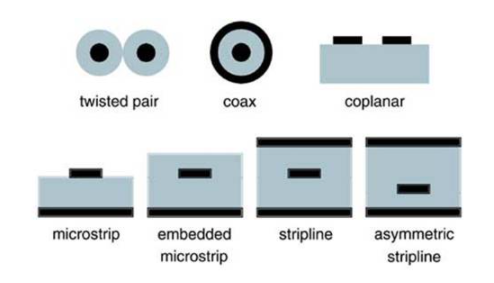

PCB传输线参数

传输线阻抗匹配有了一点经验总结

差分线传输线长度差有关的问题

如何用LOTO示波器TDR方法测试电线长度?

工程师头疼的差分线传输线长度差问题资料下载

PCB传输线参数

传输线长度长了一点行不行呢?

传输线长度长了一点行不行呢?

评论