5.1模式自适应

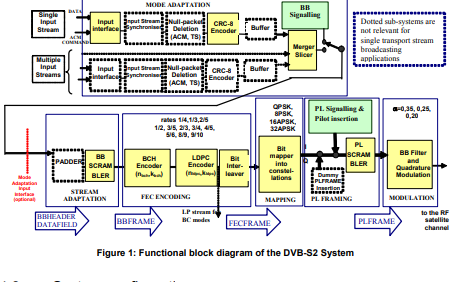

该子系统应在DATAFIELD中执行输入接口、输入流同步(可选)、空包删除(仅针对TS输入流和ACM)、用于错误检测的CRC-8编码(仅针对分组的输入流)、输入流合并(仅针对多个输入流)和输入流切片。最后,插入基带信令,通知接收方所采用的模式自适应格式。

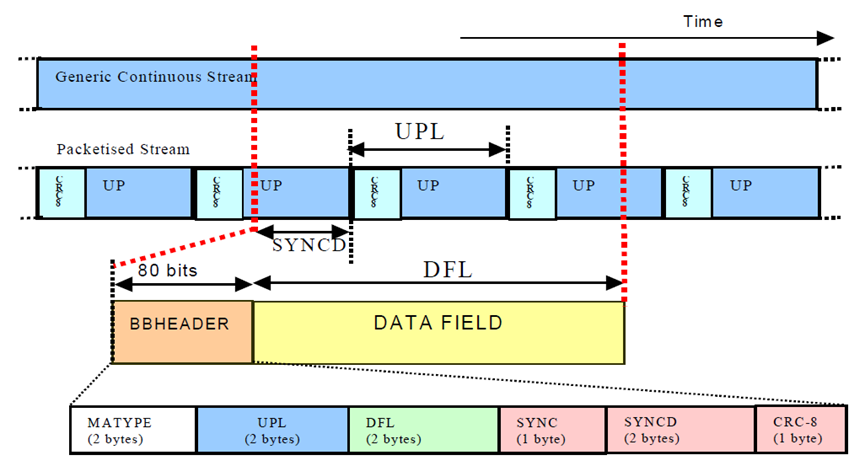

由图3可知,输入序列为:

单个或多个传输流(TS)。

单个或多个通用流(分组或连续)。

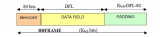

输出序列是一个BBHEADER(80bit),后面跟着一个DATA FIELD。

5.1.1输入接口

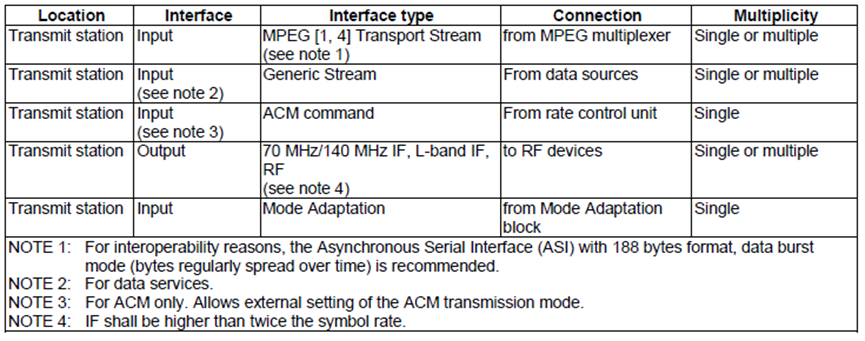

本文件所定义的系统应以表2所示的接口为界。

表2:系统接口

输入接口子系统应将输入电气格式映射为内部逻辑比特格式。第一个接收到的比特将被表示为最高有效位(MSB)。

传输流应由恒定长度UPL =188 × 8比特(一个MPEG包)的用户包(UP)来表征,第一个字节是同步字节(47HEX)。

通用流的特征是连续的比特流或长度为UPL比特(UPL最大值为64k, UPL = 0D表示连续流,参见5.1.5)的定长用户包(UP)流。变长包流或超过64k bit的定长包应被视为连续流。

对于一般的分组流,如果一个同步字节是UP的第一个字节,则保持不变,否则在每个包之前插入一个同步字节= 0D, UPL增加8。UPL信息可以通过静态调制器设置得到。

“ACM命令”信令输入应允许通过外部“传输模式控制单元”设置DVB-S2调制器将采用的传输参数,用于输入数据的特定部分。ACM命令应根据第D.1条。

模式自适应(可选输入)应是一系列数据字段(根据第5.1.5条),其中每个单独的数据字段之前都有一个BBHEADER(根据第5.1.6条和图3)和流适应命令(根据第I.1条),允许通过外部“3模式适应单元”设置DVB-S2调制器对每个特定MA包采用的传输参数。模式自适应应根据第I.1条(独立信令电路)或I.2条(带内信令)。

5.1.2 输入流同步器(可选,与单个TS - BS无关)

DVB-S2调制器中的数据处理可能会对用户信息产生可变的传输延迟。输入流同步器子系统(可选)应提供适当的方法来保证对分组输入流(例如传输流)的恒定比特率(CBR)和恒定的端到端传输延迟。此过程应遵循附件D中给出的规范。TR 102 376 [i.5]给出了接收机实现的示例。

5.1.3 空包删除(仅限ACM和传输流)

对于ACM模式和传输流输入数据格式,必须识别MPEG空包(PID = 8191D)并删除。这样可以降低信息速率并增加调制器中的错误保护。该过程的执行方式是将被删除的空包重新插入到接收器中,在它们最初所在的确切位置。这一过程应遵循附件D中规定的规范。

5.1.4 CRC-8编码器(仅用于分组流)

如果UPL = 0D(连续通用流),该子系统将不加修改地传递输入流。

如果UPL≠0D,则输入流是一个长度为UPL位的用户数据包序列,前面有一个同步字节(当原始流不包含同步字节时,同步字节= 0D)。

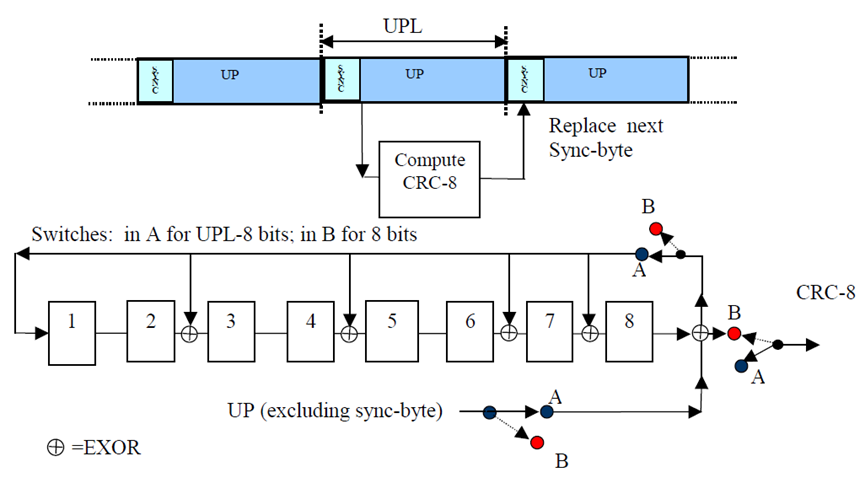

UP的有用部分(不包括同步字节)应由系统的8位CRC编码器处理。生成器多项式应为:

CRC编码器输出应计算为:

CRC = remainder [u(X) : g(X)]

其中u(X)为系统编码的输入序列(UPL - 8位)。图2给出了通过移位寄存器实现CRC生成器的可能方法。

在每个序列的第一个比特进入电路之前,寄存器应被初始化为全零。

计算出的CRC-8将取代后续UP的同步字节。如第5.1.6节所述,同步字节被复制到BBHEADER的SYNC字段中进行传输。

图2:CRC-8编码器的实现

5.1.5 合并/切片

根据图3,合并/切片器输入流被组织为通用连续流或分组输入流。UP长度为UPL位(其中UPL = 0表示连续序列)。输入流应被缓冲,直到合并/切片器读取它们。

切片器应从其输入(单个输入流)或其中一个输入(多个输入流)中读取(即切片)一个由DFL位(数据字段长度)组成的数据字段,其中:

Kbch-(10 × 8)≥DFL≥0(根据表5的Kbch, 80 bit专用于BBHEADER,见第5.1.6条)。

合并应在单个输出中连接从其中一个输入读取和切片的不同数据字段。对于单个流,只应用切片功能。

数据字段(DATA FIELD)应由来自单个输入端口的位组成,并应以同质传输模式(FEC代码和调制)传输。合并/切片器优先级策略依赖于应用,应遵循表4(单一传输流广播服务)和表D.2(用于其他应用领域)中描述的策略。

根据应用的不同,合并/切片器应该分配一个等于最大DATA FIELD容量的输入位(DFL = Kbch -80),从而在后续的DATA FIELD中分解UP,或者应该在DATA FIELD中分配一个整数个UP,使DFL变量在上述指定的边界内。

当在合并/切片器请求的任何输入端口上没有数据字段时,物理层帧子系统应生成并传输一个DUMMY PLFRAME(见第5.5.1条和表12)。

当同步字节被CRC-8替换后(见5.1.4),有必要为接收端提供一个恢复UP同步的方法(当接收端已经同步到DATA FIELD时)。因此,从DATA FIELD开始和第一个完整UP (CRC-8的第一个比特)开始的比特数(见图3)将被合并/切片器检测并存储在基带标头的SYNCD字段(即SYNC Distance)中(见第5.1.6条)。例如,SYNCD = 0D意味着第一个USER PACKET与DATA FIELD对齐。

图3:MODE ADAPTER输出端的流格式

5.1.6 基带头(Base-Band Header)插入

在DATA FIELD前面插入一个10字节的固定长度基带报头(BBHEADER),描述其格式(假设内部码率为1/2,由BBHEADER引入的最大效率损失为0.25 % nldpc =64 800, 1% nldpc = 16 200)。

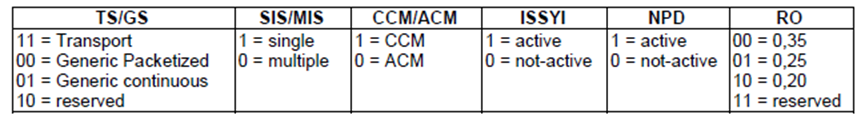

MATYPE(2 byte):描述输入流格式、模式自适应类型和传输滚降因子,如表3所示。

第一个字节(MATYPE-1):

TS/GS字段(2 bit):传输流输入或通用流输入(分组或连续)。

SIS/MIS字段(1 bit):单输入流或多输入流。

CCM/ACM字段(1 bit):固定编码和调制或自适应编码和调制(VCM信号为ACM)。

ISSYI(1 bit),(Input Stream SynchronizationIndicator):如果ISSYI = 1 = active,则ISSY字段在UP之后插入(见附件D)。

NPD(1 bit):空包删除激活/不激活。

RO(2 bit):传输滚降系数(α)。

第二字节(MATYPE-2):

如果SIS/MIS =多个输入流,则第二个字节=输入流标识符(ISI);否则保留第二个字节。

UPL(2字节):用户数据包长度,单位为比特,取值范围为0 ~ 65535。

例1:0000HEX=连续流。

例2:000AHEX= UP长度为10bit。

例3:MPEG传输流数据包的UPL = 188x8D。

DFL(2字节):数据字段长度,单位为bit,取值范围0 ~ 58112。

例4:000AHEX=数据字段长度为10bit。

SYNC(1字节):用户数据包同步字节的副本

对于分组传输或通用流:用户包同步字节的副本;

对于连续通用流:SYNC= 00 - B8保留传输层协议信令根据参考ETR 162 [i.4];SYNC=B9-FF用户私有)。

例5: SYNC = 47HEX,MPEG传输流数据包。

例6: SYNC = 00HEX,当输入的通用分组流不包含同步字节时, (因此接收端在CRC-8解码后,应该删除CRC-8字段而不重新插入同步字节)。

SYNCD (2 bytes):

对于分组传输或通用流:从数据字段的开始到该帧的第一个UP (CRC-8的第一个比特)的距离,单位为比特。SYNCD = 65535D表示DATA FIELD中没有UP启动;

对于连续通用流:SYNCD= 0000 - FFFF保留供将来使用。

CRC-8(1字节):应用于BBHEADER前9个字节的错误检测码。

CRC-8采用图2的编码电路计算(开关A为72位,开关B为8位)。

BBHEADER的传输顺序来自TS/GS字段的MSB。

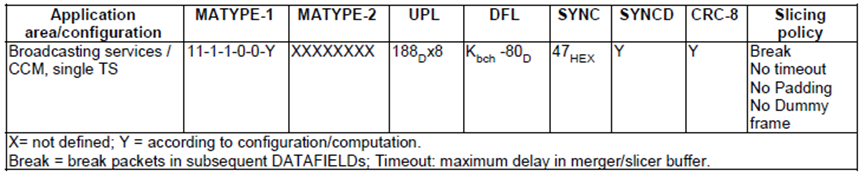

表4显示了单个传输流广播服务的BBHEADER和切片策略。对于其他应用领域,BBHEADER和合并/切片策略定义如表D.2所示。

表3:MATTYPE-1字段映射

表4:单传输流广播服务的BBHeader(模式适应特征)和切片策略

审核编辑:刘清

-

DVB

+关注

关注

1文章

90浏览量

36184 -

调制器

+关注

关注

3文章

978浏览量

48737 -

同步器

+关注

关注

1文章

117浏览量

15698 -

ACM

+关注

关注

0文章

40浏览量

10795 -

CRC效验

+关注

关注

0文章

30浏览量

1385

原文标题:DVB-S2标准协议:模式自适应(中文版)

文章出处:【微信号:FPGA算法工程师,微信公众号:FPGA算法工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

国内外主流DVB-S ,DVB-S2及ISDBT 方案,功能

N5182A信号发生器能生成dvb-s2信号吗?

采用MSD7S45的海外DVB-S2高清机顶盒方案

基于MSD7S01的DVB-S2机顶盒方案

DVB-S/DVB-S2信号发生器 (DVB-S/S2 Si

基于人工神经网络的DVB-S2数字信号调制模式识别

基于PXA270 和STi710x 的双CPU DVB-S2

基于PXA270和STi710x的双CPU DVB-S2标准

国际市场大丰收 从直播星到DVB-S2

澜起科技发布DVB-S2解调芯片M88DS3103

SUNNISKY TS2000-S2 DVB-S2卫星数字信号处理器

澜起科技推出DVB-S2/S卫星数字电视接收前端单芯片M88RS6000

DVB-S2新一代数字卫星广播标准资料免费下载

DVB-S2标准协议:模式自适应

DVB-S2标准协议:模式自适应

评论