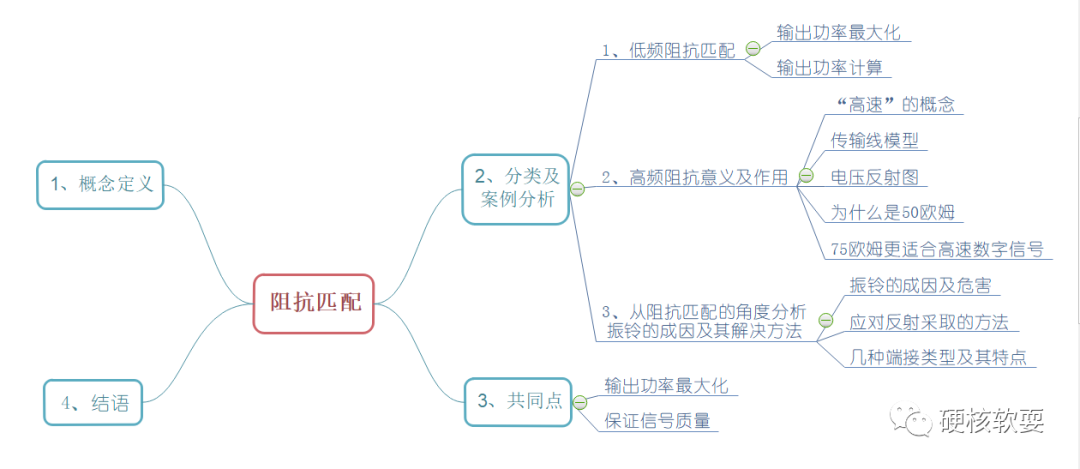

为什么要阻抗匹配?

在高速数字电路系统中,电路数据传输线上阻抗如果不匹配会引起数据信号反射,造成过冲、下冲和振铃等信号畸变,当然信号沿传输线传播过程当中,如果传输线上各处具有一致的信号传播速度,并且单位长度上的电容也一样,那么信号在传播过程中总是看到完全一致的瞬间阻抗。 由于在整个传输线上阻抗维持恒定不变,我们给出一个特定的名称,来表示特定的传输线的这种特征或者是特性,称之为该传输线的特征阻抗。

特征阻抗是指信号沿传输线传播时,信号感受的瞬间阻抗的值。 特征阻抗主要参数与PCB导线所在的板层、PCB所用的材质(介电常数)、走线宽度、导线与平面的距离等因素有关,与走线长度无关。 特征阻抗可以使用软件计算。 高速PCB布线中,一般把数字信号的走线阻抗设计为50欧姆,这是个大约的数字。 一般规定同轴电缆基带50欧姆,频带75欧姆,对绞线(差分)为100欧姆。

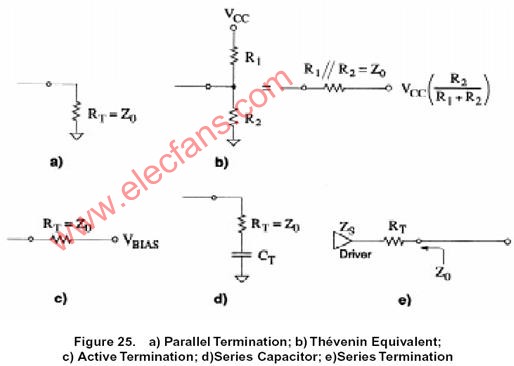

而减小反射的方法是根据传输线的特性阻抗在其发送端串联端接使源阻抗与传输线阻抗匹配或者在接收端并联端接使负载阻抗与传输线阻抗匹配,从而使源反射系数或者负载反射系数为零。 常用的端接方式为:串联端接、简单的并联端接、戴维宁端接、RC网络端接等。

下面我们将分别对这几种端接方式进行分析

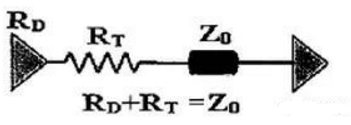

1、串联端接

串联端接

在信号源端阻抗低于传输线特征阻抗的条件下,在信号的源端和传输线之间串接一个电阻R,使源端的输出阻抗与传输线的特征阻抗相匹配,抑制从负载端反射回来的信号发生再次反射。

匹配电阻选择原则:匹配电阻值与驱动器的输出阻抗之和等于传输线的特征阻抗。 常见的CMOS和TTL驱动器,其输出阻抗会随信号的电平大小变化而变化。 因此,对TTL或CMOS电路来说,不可能有十分正确的匹配电阻,只能折中考虑。 链状拓扑结构的信号网路不适合使用串联终端匹配,所有的负载必须接到传输线的末端。

串联匹配是最常用的终端匹配方法。 它的优点是功耗小,不会给驱动器带来额外的直流负载,也不会在信号和地之间引入额外的阻抗,而且只需要一个电阻元件。

常见应用:一般的CMOS、TTL电路的阻抗匹配。 USB信号也采样这种方法做阻抗匹配。

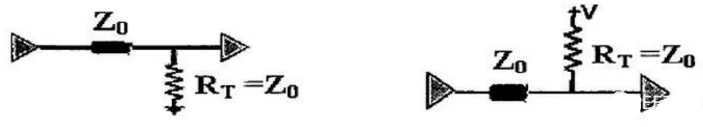

2、简单的并联端接

并联端接

在信号源端阻抗很小的情况下,通过增加并联电阻使负载端输入阻抗与传输线的特征阻抗相匹配,达到消除负载端反射的目的。 实现形式分为单电阻和双电阻两种形式。

匹配电阻选择原则:在芯片的输入阻抗很高的情况下,对单电阻形式来说,负载端的并联电阻值必须与传输线的特征阻抗相近或相等; 对双电阻形式来说,每个并联电阻值为传输线特征阻抗的两倍。

并联终端匹配优点是简单易行,显而易见的缺点是会带来直流功耗:单电阻方式的直流功耗与信号的占空比紧密相关; 双电阻方式则无论信号是高电平还是低电平都有直流功耗,但电流比单电阻方式少一半。

常见应用:以高速信号应用较多。

(1) DDR、DDR2等SSTL驱动器。 采用单电阻形式,并联到VTT(一般为IOVDD的一半)。 其中DDR2数据信号的并联匹配电阻是内置在芯片中的。

(2) TMDS等高速串行数据接口。 采用单电阻形式,在接收设备端并联到IOVDD,单端阻抗为50欧姆(差分对间为100欧姆)。

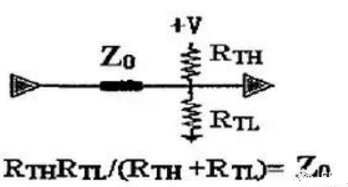

3、戴维宁端接

戴维宁端接

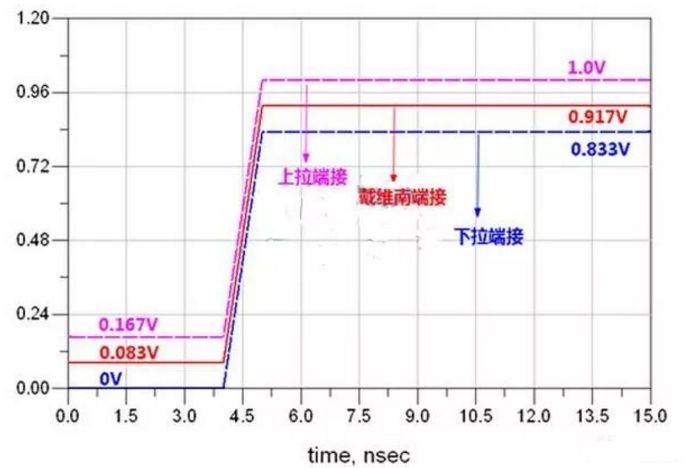

上拉端接会拉高低电平,下拉端接会降低高电平,这两种端接方式虽然都可以抑制过冲和振铃,但同时也会减小信号裕量,如果使用不当还会造成信号电平的误触发。 戴维南端接方式既可以抑制过冲,又没有这些缺陷。

常见应用:以DDR2地址、控制命令等信号。

以上三终端接比较

戴维南端接优势更大

缺点就是在逻辑高和逻辑低状态下,都有直流功耗,所以该端接方式功耗较大,同时所用器件 较多,容易造成PCB布线紧张。

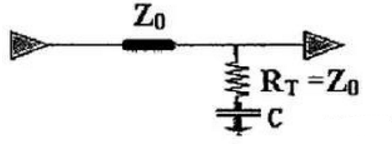

4、RC端接

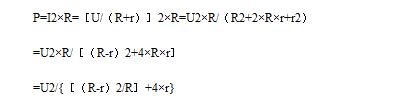

戴维南端接在电路没有工作的时候,上拉电阻和下拉电阻上依然会有电流,这样会增加电路的功率消耗。 为了解决这个问题,RC端接被派上了用场。 有些地方也叫AC端接,其实就是在并联端接的基础上增加了一个电容,电容一般采用0.1uF多层陶瓷电容,由于电容通低频阻高频的作用,因此电阻不是驱动源的直流负载,故这种端接方式无任何直流功耗,交流功耗也非常小,该端接主要用于时钟电路。

RC端接

为实现阻抗匹配,R的电阻值也要等于传输线的阻抗值。 电容的容值对信号有什么影响呢

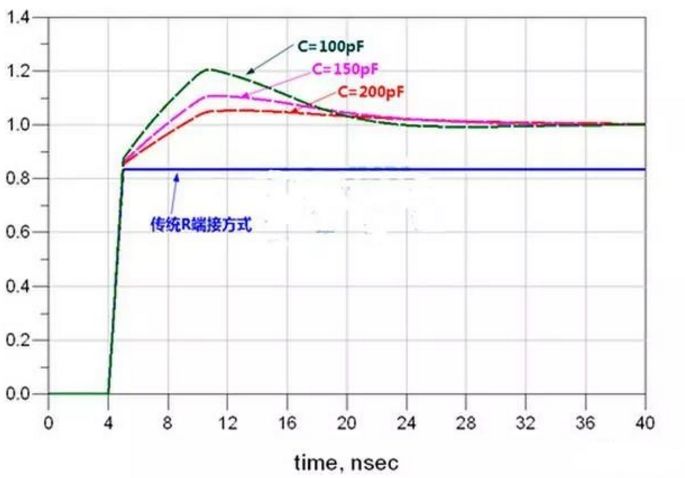

RC端接电容的影响

蓝色波形是传统的下拉端接。 绿色,紫色和红色,分别是电容取100pF,150pF和200pF的时候对应的波形。

需注意,此RC电路可能会因此电路上升沿变换,虽然会降低EMC,但如果过缓,则会引起数据线是叙问题。 在数据线上使用这种电路时,需特别小心。

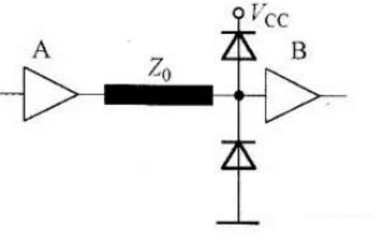

5、终端肖特基并联端接

肖特基端接

又叫二极管并联端接,通常应用在器件内部。 现在很多器件自带有输入保护二极管,该端接能有效减小信号过冲和下冲,但并不能消除反射; 同时二极管的开关速度会限制响应时间,所以较高速系统不合适。

最后,在实际的工程应用中,具体使用哪种端接,需要具体问题具体分析。 信号性质不同,对信号质量的要求也不同。 最主要的是需要了解各种端接的优缺点以及系统对信号的要求,来最后确定使用那种端接方案。

审核编辑:汤梓红

-

二极管

+关注

关注

147文章

9669浏览量

166920 -

pcb

+关注

关注

4323文章

23128浏览量

398675 -

电路设计

+关注

关注

6678文章

2457浏览量

204845 -

阻抗匹配

+关注

关注

14文章

354浏览量

30845 -

高速电路

+关注

关注

8文章

158浏览量

24253

原文标题:高速电路设计阻抗匹配的几种方法

文章出处:【微信号:射频问问,微信公众号:射频问问】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何处理高速电路阻抗匹配?看完本文就懂了

PCB阻抗匹配的方法

分立元件组成的阻抗匹配电路

高速PCB中的阻抗匹配

怎样理解阻抗匹配_pcb阻抗匹配如何计算

高速电路设计阻抗匹配的几种方法

高速电路设计阻抗匹配的几种方法

评论