远程通信系统和远程监控系统对信号传输有两方面的要求:一方面要求接口灵活且有较高的数据传输带宽;另一方面要求系统的传输距离远。传统接口如UART,USB,以太网等在传输带宽和传输距离上均无法满足要求。

低压差分信号(LVDS)是一种低摆幅的差分信号技术。LVDS的恒流源模式及低摆幅输出使传输速度可以从数百Mb/s到2 Gb/s以上。差分传输方式使LVDS信号对共模输入噪声有更强的抵抗能力。LVDS技术功耗低,100Ω的负载电阻功耗仅有1.2 mW。这些特点使得LVDS技术广泛应用在许多要求高速度与低功耗的领域。

随着半导体工艺进步,现场可编程逻辑阵列(FPGA)的性能和集成度在不断提高,同时成本在下降。FPGA片内资源丰富且灵活性强。通过配置逻辑资源和I/O,可以生成支持各种标准的接口,适合完成接口间的通信工作。FPGA的可重构性使相同的硬件环境可以实现不同的功能,节约了系统升级和更改的成本。

1 系统构成及原理

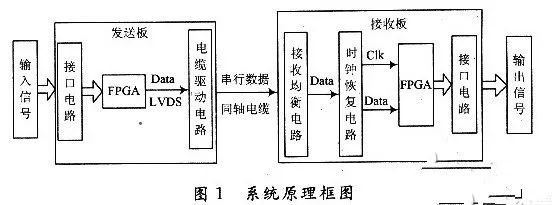

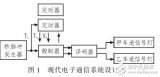

高速数据传输系统的原理框图如图1所示。整个系统由发送板、接收板和传输线三部分组成。

发送板主要由接口电路、FPGA和电缆驱动电路组成,完成的功能是将输入的各种信号转换为串行数据帧通过传输链路进行传输。接收板主要由接收均衡电路、时钟恢复电路、FPGA和接口电路组成,实现将串行数据帧接收并恢复成原始信号的功能。传输线选用同轴电缆。与双绞线相比同轴电缆的抗干扰能力强、传输距离远,与光缆相比同轴电缆的成本低。同轴电缆适合本系统这种传输速率低于200 Mb/s,传输距离小于300 m的应用场合。

系统的输入信号包括串口信号、网络信号和并行视频信号等。分别选用MAX232,RTL8201,SN74LVC4245等芯片组成接口电路,将输入信号转换为FPGA支持的LVTTL/LVCMOS电平信号,起到保护器件和增加信号驱动能力的作用。

接收板FPGA首先完成系统输入信号的接收工作,再将异步时钟域的信号转换到统一的系统时钟下,接下来将信号并串转换并添加起始位、停止位和校验位组成特定的帧格式,然后对其进行8 B/10 B编码,通过差分I/O以LVDS电平输出。接收板FPGA接收到串行信号后将信号解码、解帧,抽取出原始数据进行恢复,通过相应的I/O将恢复后的信号输出给各接口。

从FPGA直接输出的LVDS信号在100 Mb/s传输速率下传输距离不足10 m,需要使用电缆驱动电路增加LVDS信号的驱动能力,同时使用接收均衡电路补偿通过电缆传输后衰减的信号,达到加强系统长距离传送能力的目的。

如果使用1根同轴电缆传输时钟,其余传输数据,会因为无法保证这些电缆严格等长导致接收数据的建立时间和保持时间无法满足后级电路的要求。另一方面,经过传输后时钟信号的Jitter会增加,使FPGA内部的PLL无法锁定时钟。本系统电缆上传输的都是数据信号,接收端同步时钟通过时钟恢复电路从串行数据中还原。

2 系统的硬件设计

2.1 FPGA部分电路设计

系统选用Xilinx公司Spartan3系列的FPGA:S3C500E。它有10 476个逻辑单元,232个I/O,4个时钟管理模块(DCM),存储器包括360 Kb的块RAM和73 Kb的离散RAM。所有I/O可以组成92组LVDS差分对,输入输出速率高到622 Mb/s,所以系统不需要额外的电路实现LVDS接口。DCM模块可以将输入时钟灵活的倍频或降频,工作频率达到311 MHz。以上参数和性能不仅满足当前的设计需求,而且为系统的升级保留了充足的设计余量。FPGA外围电路包括时钟部分和配置部分。时钟使用电路板上的晶振提供,通过GCLK脚与FPGA相连。GCLK是专用时钟引脚,这个脚的驱动能力强,到所有逻辑单元的延时基本相同。配置电路采用主动SPI模式。相比其他模式,主动SPI模式的外围电路简单、体积小、成本低。而且SPI FLASH的容量大,除了存储配置文件,还可以存储其他用户数据。S3C500E的配置文件大小为2 Mb,本系统采用存储量为16 Mb的M25P16作为配置存储器。

2.2 传输部分电路设计

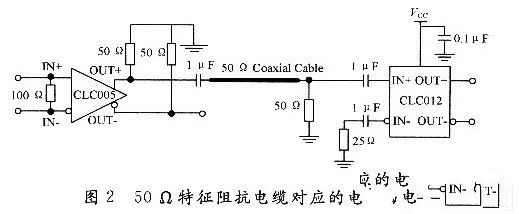

传输部分设计包括选择同轴电缆和设计相应的发送接收电路。本系统选用的同轴电缆型号为SVY-50-3,成本低、性能好。这款电缆的特征阻抗为50 Ω,速率150 MHz时信号传输100 m的衰减为18.01 dB。它具有良好的屏蔽特性,可以在复杂的电磁环境中正常工作。电缆驱动电路和接收均衡电路分别选用National Semiconductor公司的芯片CLC005和CLC012。CLC005支持LVDS电平输入,传输速率达到622 Mb/s,输出信号峰一峰值从O.7~2 V。CLC012可以自动均衡频率在50~650 MHz的信号。时钟恢复器件选用CLC016,它的输入信号来自CLC-012,输出时钟和数据接FPGA,恢复的时钟在数据上升沿有效。CLC005和CLC012用于特征阻抗为75 Ω的传输系统,针对本系50 Ω特征阻抗的同轴电缆,需要改动外围电阻配置,否则会因为阻抗不匹配引起信号反射,终导致信号传输质量下降。相应的配置方式如图2所示。

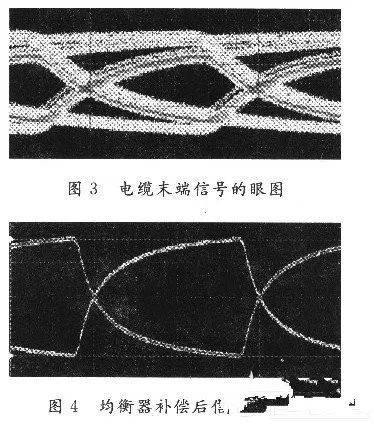

通过测试,此组传输器件可以驱动LVDS信号通过SVY-50-3型号电缆传输至少200 m。信号经过传输后,在电缆末端衰减严重,噪声和抖动也较严重。此时信号眼图如图3所示,可以看出信号质量差。直接接收此信号,会产生信号电平误判,而且信号的抖动将导致后级电路无法正常工作。接收均衡器CLC012自动为信号损耗提供补偿后,信号上的噪声和抖动均得到了改善,信号的眼图如图4所示。

LVDS驱动器由恒流源构成,因此需要做终端匹配。通常情况下在输入端并联100 Ω电阻从而满足互联系统要求的差分阻抗。在强噪声环境下,交流耦合连接时可以采用戴维南终端匹配方式提供1.2 V的偏置电压,同时满足100 Ω差分阻抗的设计要求。具体方法是将LVDS的+/-端通过130 Ω电阻上拉至VCC,同时下拉82 Ω电阻到地,如图5所示,电阻精度要求在1%。

2.3 电路PCB设计

在PCB设计过程中,要注意电路板的布局。模拟电路和数字电路需要分开,使用单点接地的方式相连。将边沿速率变化快的VTTL/LVCMOS信号与LVDS信号布在不同信号层上,并用电源和底层隔开,减小耦合到LVDS线路上的串扰。LVDS走线要遵循以下规则:

(1)差分对两根信号从芯片扇出后就尽量靠近(紧耦合),这样有助于消除反射,确保耦合的噪声是共模形式。

(2)对内信号的布线长度要保持一致,以减小信号延时,长度匹配控制在10 mil以内。

(3)对内信号保持固定的线间距,避免因为线间距变化导致差分阻抗不连续。

(4)差分对间尽量远离,减少线间串扰,必要时在差分对间放置隔离用的接地过孔。

(5)尽量减少差分信号线上过孔的个数,避免走90°拐角,使用圆弧或者45°折线代替。

(6)LVDS信号不能跨平面分割,否则会因为缺少参考平面而导致阻抗不连续,要给LVDS信号设置完整的参考平面。

(7)匹配电阻尽可能靠近接收端。

3 系统的逻辑设计

3.1 时钟部分设计

时钟信号由电路板上40 MHz晶振提供。通过数字时钟管理单元DCM钟倍频得到120 MHz的系统的工作时钟。使用DCM模块时,注意DCM的输入和输出需要通过BUFG单元与全局时钟资源相连。全局时钟资源使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,使全局时钟到达芯片内部所有逻辑单元的时延和抖动都为。DCM在时钟锁定后使能LOCK信号,表示时钟倍频工作完成,使用这个信号作为FPGA内部其他逻辑的复位。

3.2 异步时钟域变换

系统输入信号工作在不同的异步时钟域,需要在FPGA内部将信号变换到同一个时钟域。

串口信号速度低,可以使用系统时钟高速采集的方式。根据奈奎斯特抽样定律,抽样频率大于2倍信号频率,就可以从抽样信号中无失真地恢复原信号。本系统使用高于5倍串口波特率的时钟去采集串口数据。经过误码仪的大量测试,串口数据能够被正确接收和恢复。

视频信号是并行信号,采用高速采集的方法会增加数据量,不适合本系统。本系统采用双口FIFO完成异步时钟域转换。S3C500E片内的Block RAM资源可以灵活的生成双口FIFO,与普通逻辑单元生成的双口FIFO相比,它的稳定性高,读写速度快,产生亚稳定状态的概率小。双口FIFO的输入端连接系统输入信号的时钟和数据;在输出端连接系统时钟数据。双口FIFO的读取时钟速度必须高于写入速度,以避免FIFO存满后溢出导致有效数据丢失。另一方面,慢时钟域向快时钟域转换的时候,FIFO会出现读取空的状态,此时将取出无效数据(这些数据是FIFO中一个数据的重复)。无效数据通过串行数据帧传输到接收端,会导致恢复后输出信号出现误码。所以系统将FIFO的空标志empty信号添加到数据帧,用于识别无效数据。

3.3 数据组帧及编码

同步传输需要将原始数据组成数据帧再进行发送,即在数据间添加起始位、停止位和校验位。数据帧的起始位过长会影响传输效率,过短会增加接收端识别的难度。本系统选用80 b为一帧,起始位为8 b,停止位为2 b,奇校验位为1 b。接收端逻辑通过对多个数据帧分析后,定位数据帧的起始位。由于每帧数据长度固定,所以找到某一帧的起始位后可以周期性的计算出接下来各帧的起始位置,不再需要反复做识别工作。

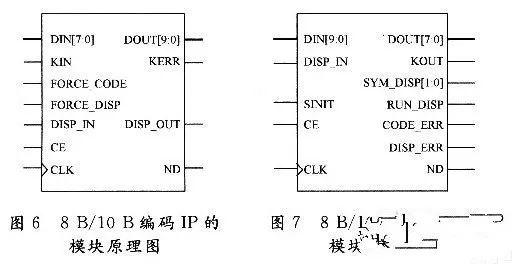

数据组帧后信号的平均位速率可能低于CLC012的工作频率,不能直接用于传输,还需要对其进行8B/10B编码。8B/10B技术是将8个数据位经过某种映射的机制转化为10个数据位的字码,可使发送的“O”、“1”数量保持一致,连续的“1”或“0”基本不超过5位。8 B/10 B编码技术保证了传输的DC平衡,增加了信息传输的可靠性。系统使用Xilinx公司提供的8 B/10 B编码和解码IP核,减少了系统的开发周期,增加了系统的稳定性。8 B/10 B编码及解码IP的模块原理图如图6和图7所示。

4 结语

介绍了一种基于FPGA的高速通信系统,通过电缆驱动器和接收均衡器,拓展了LVDS信号的传输距离。经过测试,使用同轴电缆的传输距离达到200 m,单个通道传输速率达到120 Mb/s。FPGA的可重构性使系统灵活多变,可以适应不同的应用需求。

审核编辑:汤梓红

-

FPGA

+关注

关注

1630文章

21796浏览量

605872 -

pcb

+关注

关注

4326文章

23159浏览量

399826 -

通信系统

+关注

关注

6文章

1204浏览量

53454 -

lvds

+关注

关注

2文章

1045浏览量

65988 -

高速通信

+关注

关注

0文章

25浏览量

10894

原文标题:基于FPGA的高速通信系统设计

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于FPGA的高速通信系统设计

基于FPGA的高速通信系统设计

评论