对于DFF,之前理解的,DFF在时钟的上升沿进行对D端的数据采集,再下一个时钟的上升沿来临,Q端输出D端采集的数据。能这么理解,是离开书本时间太长了,又观察到了ModelSim仿真波形的影响,这么理解只是在描述仿真波形的表征现象,并非根本的原理。比如,在Modelsim仿真中,若通过DFF将数据组进行延时,用时钟将寄存器进行多个时钟周期的同步,并带有异步复位,对应Verilog描述如下:

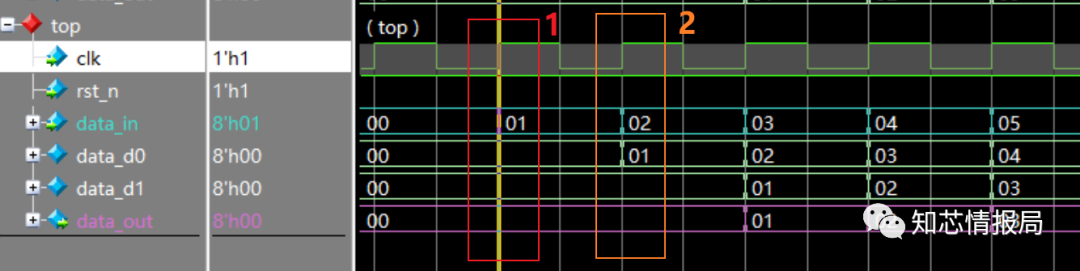

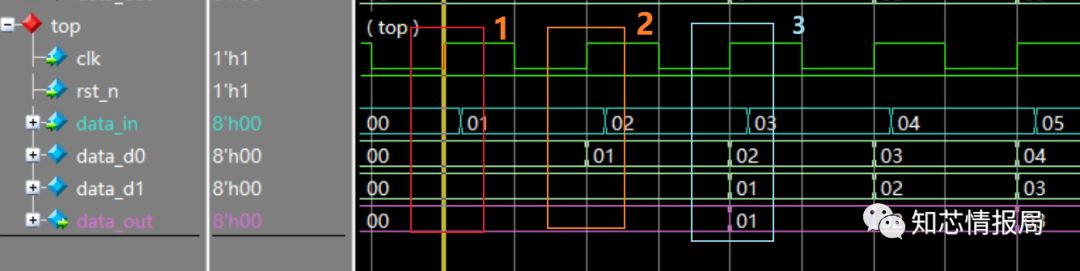

reg [7:0] data_d0, data_d1, data_d2; always @ ( posedge clk or negedge rst_n ) begin if ( !rst_n ) begin data_d0 <= 8'b0; data_d1 <= 8'b0; end else begin data_d0 <= data_in; data_d1 <= data_d0; end end对应仿真波形如下:

此时,时钟上升沿和数据的变化沿都是对齐的,就产生了不正确的理解:通过Modelsim的wave窗口查看仿真波形的时候,如果将光标打到时钟的上升沿时候(比如心在光标在Event 1时刻),对应的数据data_in应该是从8‘h00->8‘h0’1,可是光标处data_in的数值显示为8’h01。

这样,我就理解成了在Even1时刻,时钟的上升沿对data_in(值为8’h01)进行捕获(接入到寄存器data_d0的D端),在下一个时钟的上升沿到来的时刻(Event2时刻),寄存器data_d0的Q端数据发生改变(值为8’h01)。上述理解完全是根据波形描述出来的,是不全面的,是非本源的,是错误的。

正确的理解

正确的理解应该从DFF本身出发,通过DFF的电路原理图分析DFF的电路工作原理,了解时钟上升沿之前和之内部逻辑的如何变化,如何影响了从D端到Q端的数据输出。

D锁存器

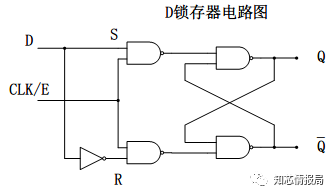

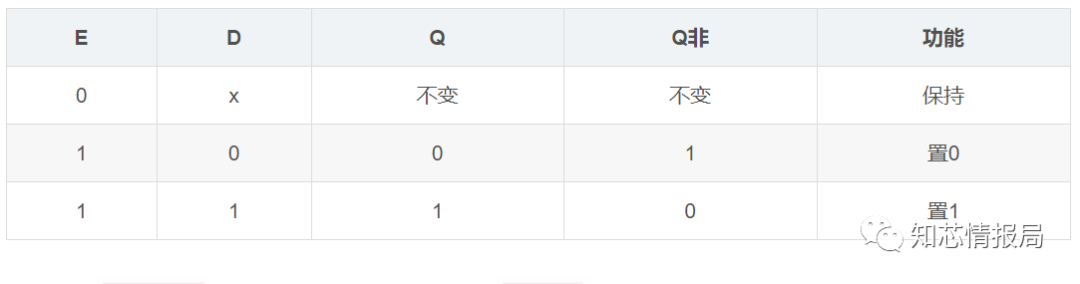

在网上找到的很多电路图讲的都是D锁存器,D锁存器的电路为消除逻辑门控SR锁存器不确定状态,在电路的S和R输入端连接一个非门(Inverter),从而保证了S和R同时为0的条件,参考下图由与非门构成的D锁存器电路图:

如果D信号在E=1期间发生变化,电路提供的信号路径将使Q端信号跟随D端变化。

在E由1跳变为0以后,锁存器将锁存跳变前瞬间D端的逻辑值,可以暂存1位二进制数据。又因为有Inverter的存在,SR锁存器不会存在S&R==1的状态,所以就有了D锁存器的捕获数据,E为0的时候会一直维持数据状态。此D锁存器的功能表为:

D触发器

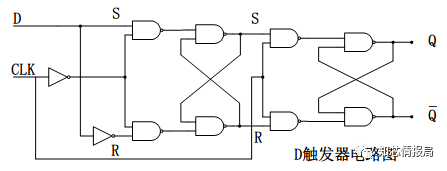

触发和触发器——时钟脉冲边沿作用下的状态刷新称为触发,具有这种特性的存储单元电路称为触发器。D触发器的电路图如下(图中的SR为了标注有两级SR锁存器,方便逻辑推理):

以上升沿触发为例,进一步分析D触发器在上升沿捕获数据,并维持锁存的过程。

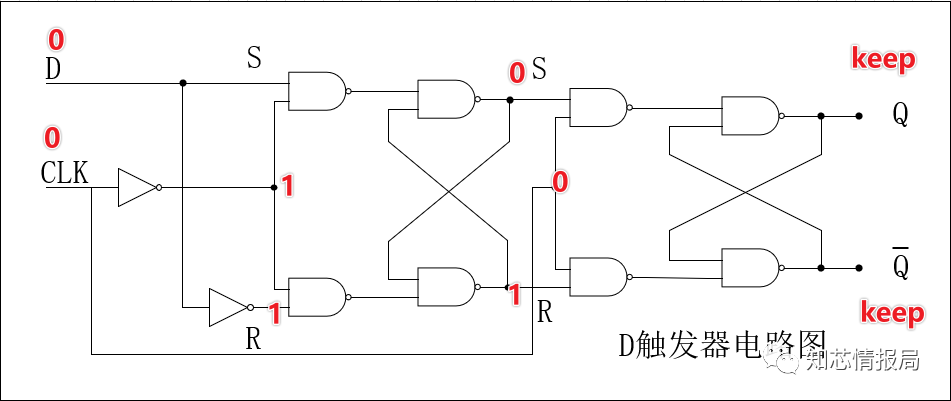

当D端为0,CLK为0时,此时第一级的D锁存器输出为0,第二级SR锁存器处于保持状态,详情参考下图:

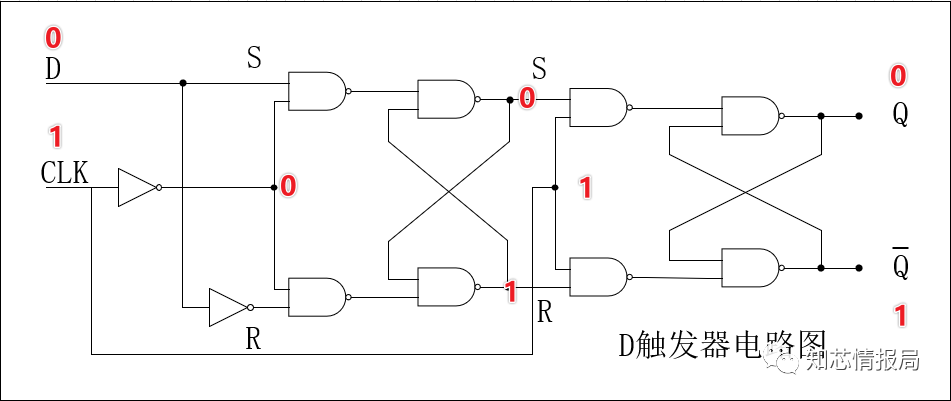

若继续保持D端为0,CLK变为1时,第一级D锁存器处于保持状态,第二级的SR锁存器将上一次的D值传递到Q端输出,详情参考下图:

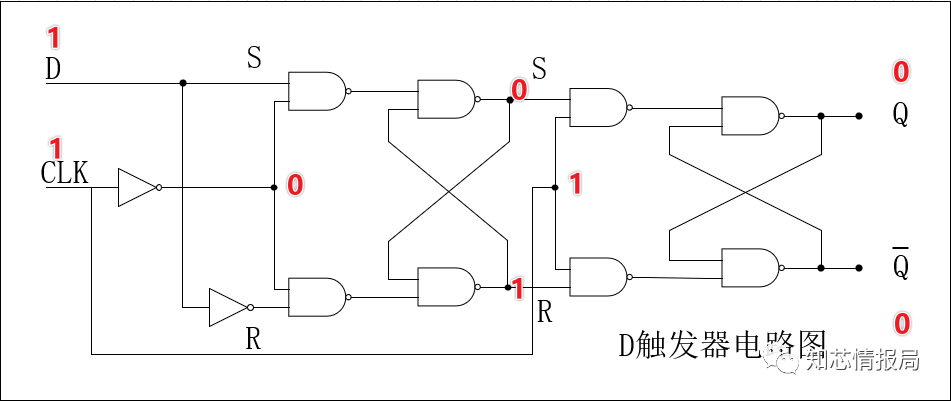

若在D端数值发生改变为1,且CLK仍然为1,第一级的D锁存器仍处于保持状态,不会由于D端的变化而改变,更不会影响最后Q端的输出。

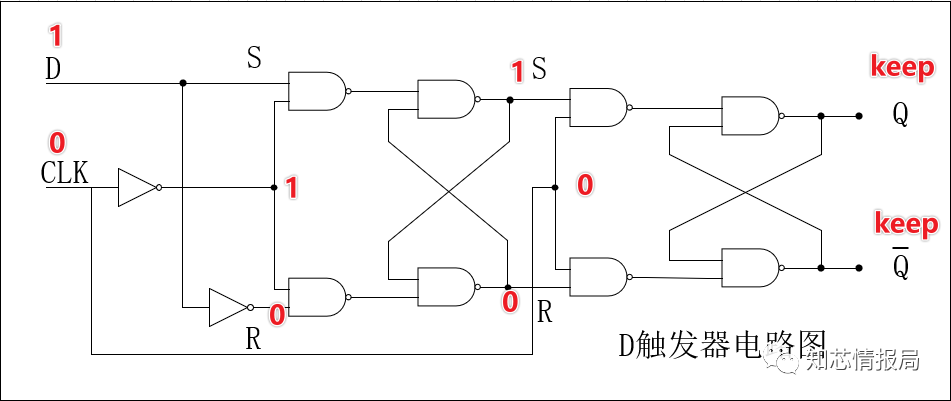

若D端继续保持为1,CLK转换为0,此时第一级D锁存器的输出为D端的数据,Q端输出仍为保持状态。

若D端数据继续保持为1,CLK转换为高,第一级D锁存器的结果就会输出到Q端,Q端的值也就随着CLK的上升沿,捕获到了1,并进行输出到Q端;

从逻辑图中,也可以看出DFF的数据捕获和输出都需要满足一定的时间约束。比如:

时钟上升沿之前前后的数据要做够稳定,否则在时钟跳变时刻,可能无法将其传递到Q端进行输出;

时钟上升沿捕获数据之后,到Q端输出也需要一定的时间,稳定之后才能用于下一级工作;

DFF捕获时钟上升沿的D端数据,并在Q端输出,一直维持到下一时钟上升沿到来之前。在此期间,D端的数据变化不会直接影响到Q端的输出。

ModelSim仿真

将tb文件中的data_in输入做5个单位的传输延时,仿真结果见下图:

可以看出,在时钟的上升沿前后数据是不发生变化的,对于寄存器做延时的时序理解为:

Event 1时刻:

在Event 1时刻,时钟上升沿之前data_in(值为8’h00),data_d0的D端为data_in(值为8’h00);

在Event 1时刻,时钟上升沿之后data_in(值为8’h00),data_d0的Q端为data_in(值为8’h00);所以在Event 1时刻,data_d0的Q端保持为8’h00不变;

Event 2时刻:

在Event 2时刻,时钟上升沿之后data_in(值为8’h01),data_d0的D端为data_in(值为8’h01);

在Event 2时刻,时钟上升沿之后data_in(值为8’h01),data_d0的D端为data_in(值为8’h01);所以在Event 2时刻,data_d0的Q端从8’h00变为8’h01;

Event 3时刻:

在Event 3时刻,时钟上升沿之后data_in(值为8’h02),data_d0的D端为data_in(值为8’h02);

在Event 3时刻,时钟上升沿之后data_in(值为8’h02),data_d0的D端为data_in(值为8’h02);所以在Even 3时刻,data_d0的Q端从8’h01变为8’h02;

可以看出在Event 1到Event 2一个时钟周期内,data_d0的数值保持为8’h00;Event 1到Event 2一个时钟周期内,data_d0的数值保持为8’h01;在时序上就表明了使用data_d0寄存器,通过clk对data_in进行了1个时钟周期的延时。在Modelsim仿真中,若数据的变化沿与时钟的上升沿对齐,cursor在时钟上升沿时刻,对应的数据需要往后加入延时,才能与实际电路情况相符合。

总结

DFF捕获时钟上升沿的D端数据,并在Q端输出,一直维持到下一时钟上升沿到来之前。在此期间,D端的数据变化不会直接影响到Q端的输出。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5343浏览量

120340 -

Verilog

+关注

关注

28文章

1351浏览量

110091 -

时序电路

+关注

关注

1文章

114浏览量

21700 -

MODELSIM仿真

+关注

关注

0文章

15浏览量

7287 -

dff

+关注

关注

0文章

26浏览量

3417

原文标题:时序电路之DFF再理解

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

组合电路和时序电路的讲解

时序电路之触发器

DFF的电路工作原理与ModelSim仿真

什么是时序电路?

什么是同步时序电路和异步时序电路,同步和异步电路的区别?

时序电路之DFF理解

时序电路之DFF理解

评论