本文来自 AMD XILINX 工程师 Fancheng Meng

1Versal 设备的 Axi bridge mode

Versal 系列的 DMA axi bridge 模式可以在 PL 的 QDMA IP 或者在 CPM(The integrated block for PCIe Rev. 4.0 with DMA and CCIX Rev. 1.0)的 QDMA IP 中选中,CPM 内嵌在CIPS (Control Interfaces and Processing System) 中。不同系列的 Versal 的产品可支持的 PCIE 最高速率不同,能够支持PCIE5.0协议的产品,例如 VPK120,其 CIPS 内使用的是 CPM5,而只能支持到 PCIE 4.0 协议的产品,例如 VCK190,其 CIPS 内使用的是 CPM4。虽然 CPM5 和 CPM4 的地址转换参数都可以在界面中配置,但是 CPM5 与 CPM4 地址转换的配置方式相差很大。如果要在 Versal 系列设备的 PL 中使用 AXI bridge mode,需要打开QDMA的IP, 选择axi bridge mode。这一点与 Ultrascale 系列不同,Ultrascale 系列设备的 axi bridge mode 需要在 XDMA IP 中打开。

2CPM4 AXI bridge mode 的地址转换

如何将 AXI 地址转换为 pcie 地址?

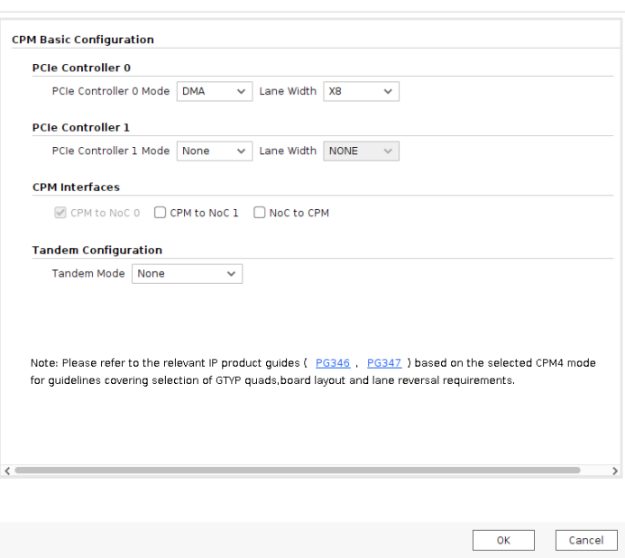

在 CPM4 的 GUI 配置界面中,通过配置 AXIBAR 的参数,来实现将 AXI4 memory map (MM) 的地址范围映射到 PCIe的地址范围。在Vivado 2022.1中打开block design,在block design中添加 CIPS IP。在配置 CPM 时,在 PCIe Controller 0 mode 中选择 DMA,在 Lane width 中选择 PCIE lane 的数目。

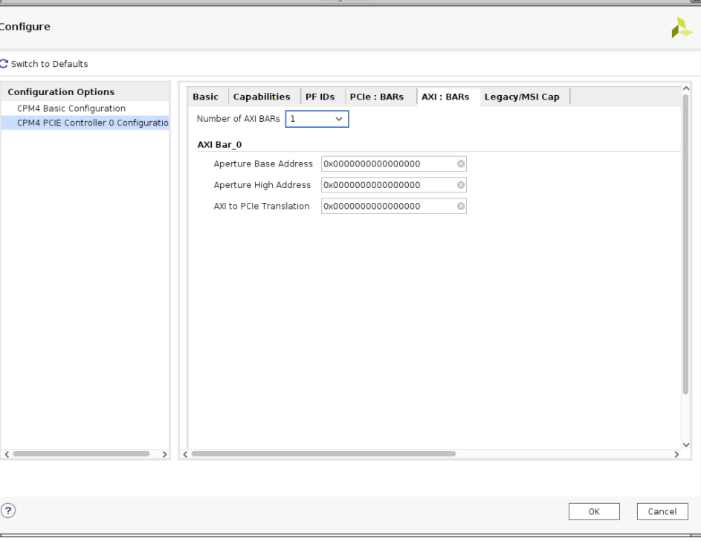

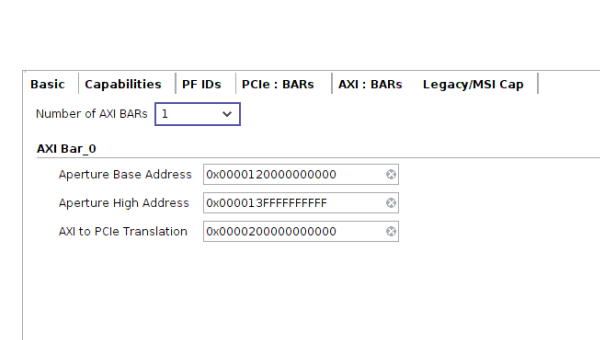

在 CPM4 PCIE Controller 0 Configuration interface 中,在 Basic、Capabilities 和 legacy/MSI Cap 等界面中选择所需的参数,然后打开 AXI:BARs 界面:

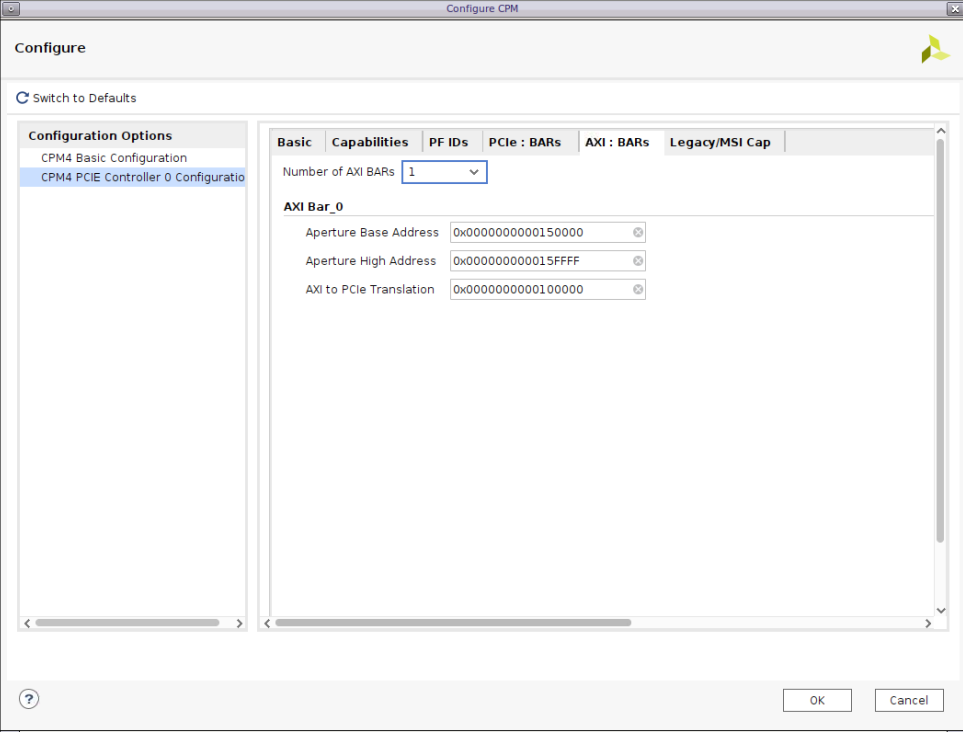

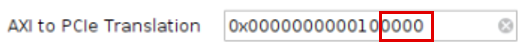

选择 AXI bar 的数量,AXI bar 的数量取决于用户需要几段地址映射,想要将几段 AXI 的地址域映射到 PCIE 域,就选择几个 bar。在进行地址映射时,可以选择将 AXI 地址映射到32位的PCIE 地址或64位的 PCIE 地址,如果想要映射到 32bit 的 PCIE 地址,在 AXI to PCIE Translation 选项中,32到64位需要配为零,以生成32位地址的 TLP包,如果想要将 AXI 地址映射到64位的 PCIE 地址,需要把 AXI to PCIE Translation 的32到64位需要配成非0,才能生产64位地址的TLP包。Aperture base address 和 Aperture High address 分别填写映射到 PCIe 地址域的 AXI 的起始地址和结束地址,以下通过举例分别对 AXI 地址映射到32位和64位 PCIE 地址,这两种情况进行说明。

示例1

示例1是将 AXI 地址映射到32位的 PCIe 地址,使用下图所配置的参数,可以将 AXI 地址150000-15FFFF 映射到 PCIE 地址 100000-10FFFF。如果发送地址为 150001的 AXI 数据包,则该 IP 会将其转换为地址为 100001 的 PCIe 数据包。

根据 AXI 地址域的大小,AXI to PCIE Translation 的位0-11位必须设置为零。

示例2

示例2是将 AXI 地址映射到64位 PCIe 地址,使用下面的参数,可以把 AXI 的地址 0X120000000000-0x13FFFFFFFFFF 映射到PCIe地址0X200000000000-0X21FFFFFFFFFF。当发送AXI 数据包的地址为 0X12FFFFFFFFFF 时,该 IP 会将地址为0X12FFFFFFFFFF 的 AXI 数据包转换为地址为 0X20FFFFFFFFFF 的 PCIe 数据包。

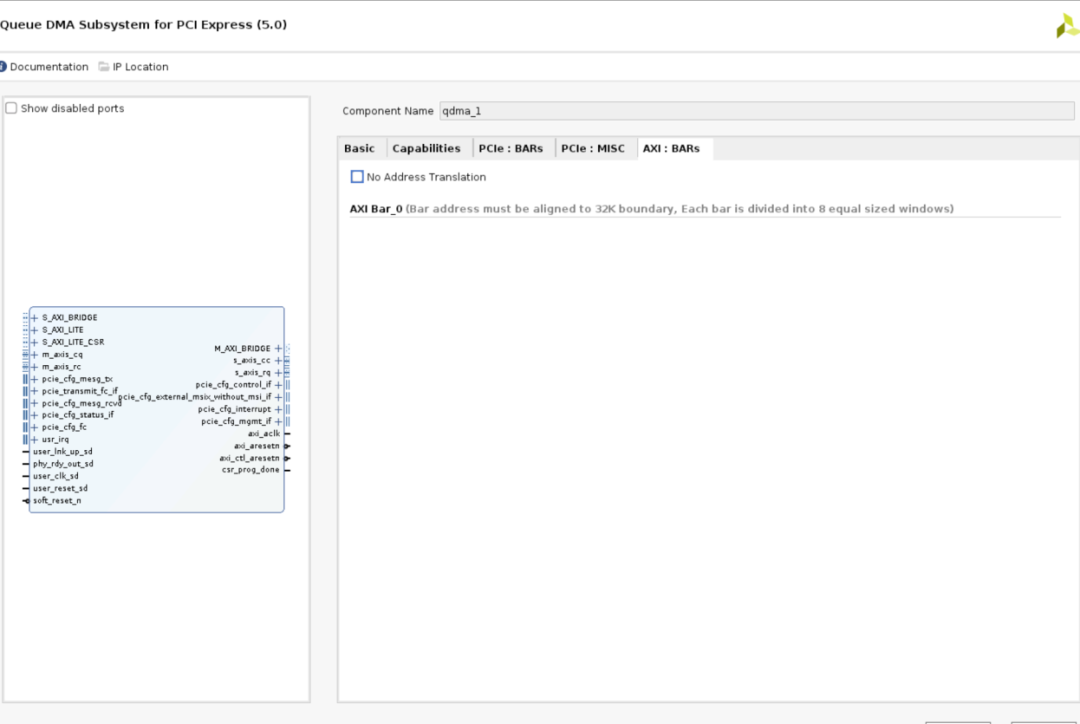

3PL Axi bridge mode 的地址转换

在 block design 中打开 QDMA IP,在 IP 的 function mode 中选择 axi bridge mode,在切换到 axi bridge mode 即可看到如下图所示,在 GUI 界面中多了 AXI:BARs 选项,可以在下面选项中选择是否使用地址转换。

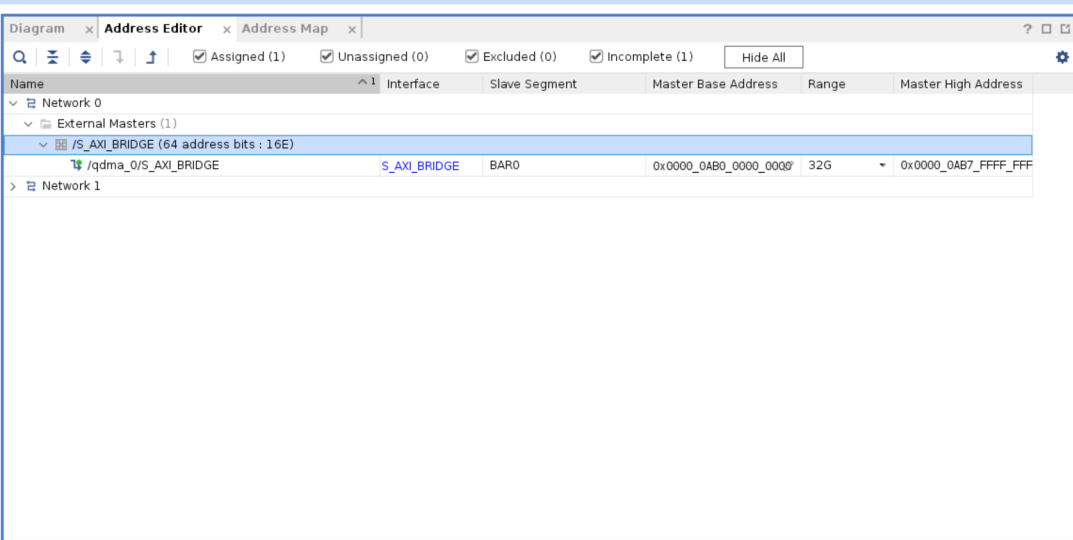

如果要使用地址转换功能,不要勾选上图选项。在进行地址转换时,地址的高位,以及转换的空间大小都需要在 block design 的 address editor 中选择,本次示例所选择的地址高位为 AB0_0000_0000,空间大小为 32G,具体配置如下图所示,起始地址、结束地址和空间大小分别是 AB0_0000_0000,AB7_FFFF_FFFF,32g。

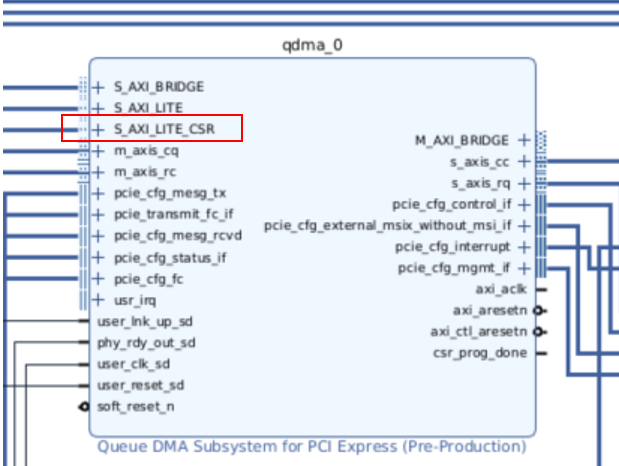

在进行完以上配置后,32GB 的空间就被平均分成了8份。在 AMD Xilinx 的手册中,通常称之为 window,每个 window 的大小是固定的 4GB,每个 window 的 AXI 起始地址和结束地址也固定了。用户可选择的是使用哪几个 window,以及每个 window 使用多少空间。如何对每个 window 进行配置呢?在PG344 上对此有所解释,AXI 的地址转换的细节是基于 BDF table 进行配置,BDF table 可以理解为 AXI 地址域到 PCIE 地址域的地址转换配置表,这张表可以通过 s_axil_csr_*. 接口进行配置,CSR 接口如下图所示,这个接口在 IP 配置界面中是可以选中的。

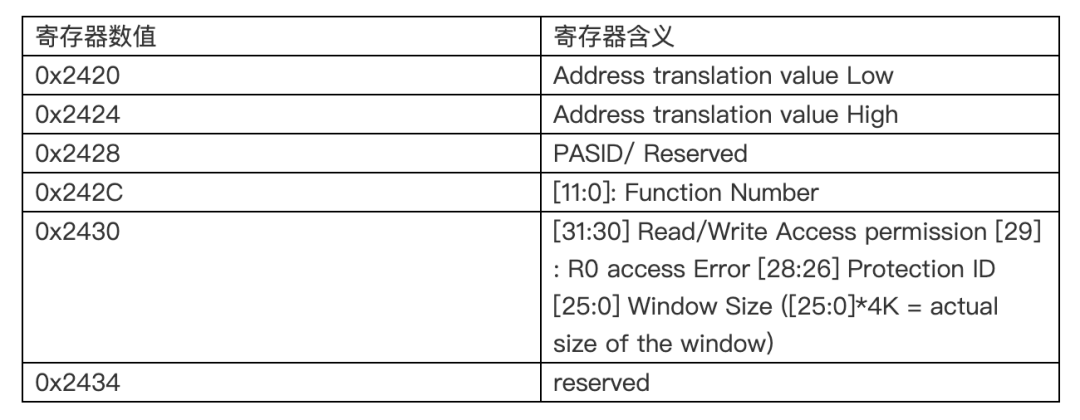

每个 window 都有6个寄存器与之对应,如果想要 window 生效,需要对这6个寄存器进行配置,第一个 window 的 6 个寄存器如下所示:

a. 0x2420

b. 0x2424

c. 0x2428

d. 0x242C

e. 0x2430

f. 0x2434

之后每个 window 的起始地址为 0x2420 + (0x20 * i),i 表示第几个 window。6个寄存器代表的含义如下表所示:

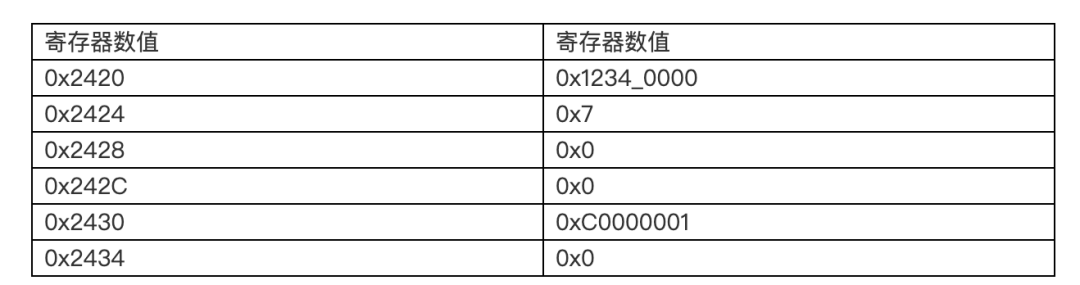

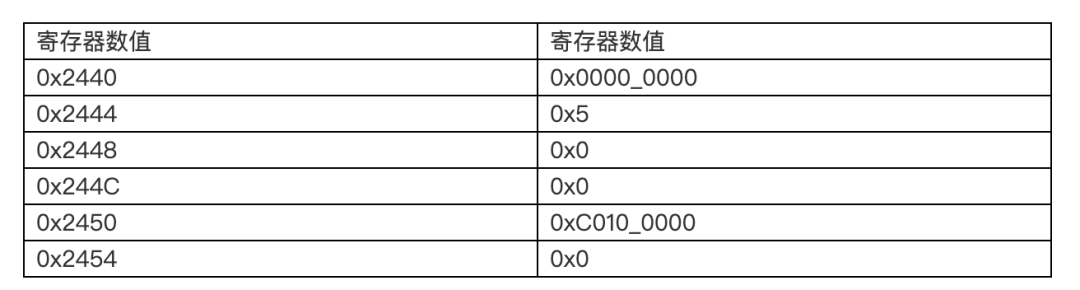

本篇 blog 通过 2个 window 的配置流程对此机制进行说明,Window 0 的大小为 4KB ,Window 1 的大小为 4GB。 Window0 将 AXI 地址的 0x0000_0AB0_0000_0000-0x0000_0AB0_0000_0FFF 转换到 PCIE 的地址 0x0000_0AB7_1234_0000-0x0000_0AB7_1234_0FFF。 Window1 将 AXI 地址的 0x0000_0AB1_0000_0000-0x0000_0AB1_FFFF_FFFF转换到 PCIE 地址的 0x0000_0AB5_0000_0000-0x0000_0AB5_FFFF_FFFF。

Window0 的 BDF table 配置如下:

如果 AXI 包的地址为 0x0000_0 AB 0_0000_0100,经 window0 转换后的 PCIE 包的地址为 0x0000_0AB7_1234_0100。

Window1 的 BDF table 配置如下:

如果 AXI 包的地址为 0x0000_0AB1_0000_0100,经 window1 转换后的 PCIE 包的地址为 0x0000_0AB5_0000_0100。

审核编辑:汤梓红

-

amd

+关注

关注

25文章

5470浏览量

134242 -

Xilinx

+关注

关注

71文章

2167浏览量

121601 -

Bridge

+关注

关注

0文章

15浏览量

11905 -

地址转换

+关注

关注

0文章

2浏览量

5618 -

Versal

+关注

关注

1文章

158浏览量

7674

原文标题:开发者分享|Versal CPM AXI Bridge 模式的地址转换

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx zynq AXI总线全面解读

AXI VIP当作master时如何使用

axi_pcie3_0编译的解决办法?

AXI接口协议详解

AXI 总线和引脚的介绍

何谓 AXI?关于AXI3/AXI4的相关基础知识

在Versal中通过NoC从PS-APU对AXI BRAM执行基本读写操作

用于PCI Express v2.1的Versal ACAP CPM模式产品指南

AMD Versal™ Adaptive SoC CPM PCIE PIO EP设计CED示例

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

Versal CPM AXI Bridge模式的地址转换

Versal CPM AXI Bridge模式的地址转换

评论