科研着实苦闷,像是拳头打在棉花上,也许是我不入流吧

看的东西多了,发现有些并未领会到位。单bit信号的跨时钟域传输,可以使用两级同步,但后果呢?

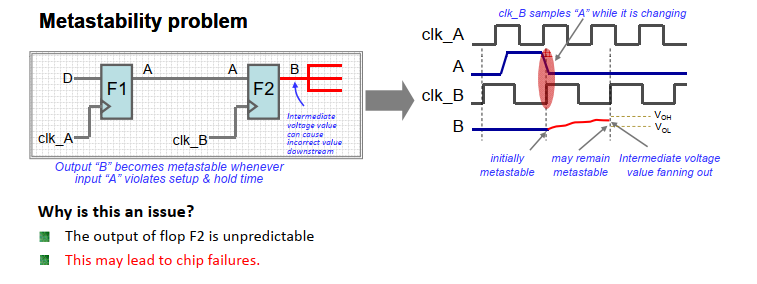

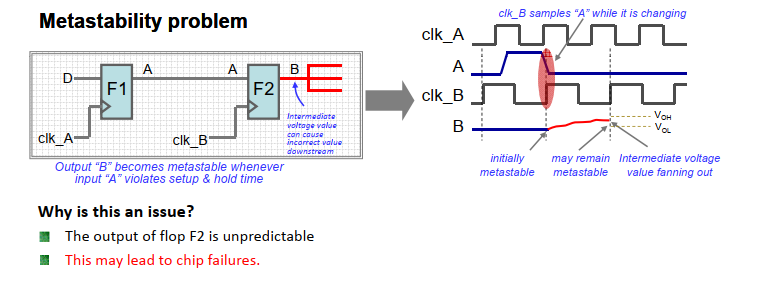

重复一下亚稳态,违反触发器的时序特性,可能导致触发器的输出进入亚稳态,亚稳态不在0和1的电压范围内。数字电路的功能体现在0和1上,亚稳态可能导致功能错误

亚稳态可能继续传播,即保持亚稳态,也可能经过一定时间稳定到0和1。换句话说,亚稳态稳定后,信号可能保持不变,也可以翻转(相比上一个周期)

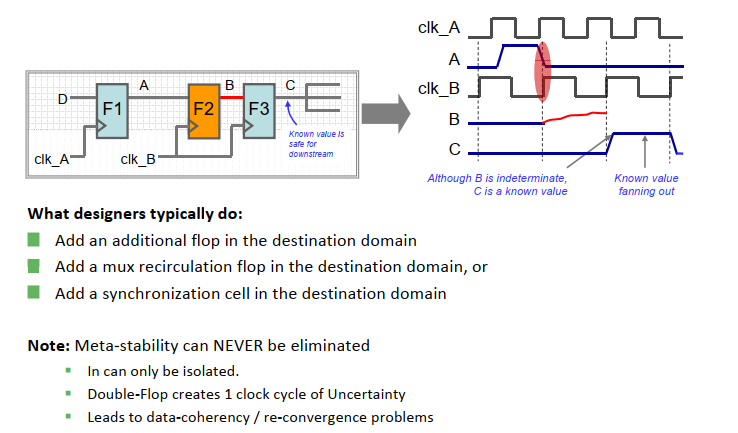

采用两级同步后,亚稳态不能被消除,增加的一级触发器隔离了亚稳态。下图中,尽管F2发生亚稳态,倘若其亚稳态能在一个周期内恢复,C的输出不会传播亚稳态。

但由于亚稳态稳定结果是不确定的,两级同步会让触发器的结果在一个周期内uncertainty

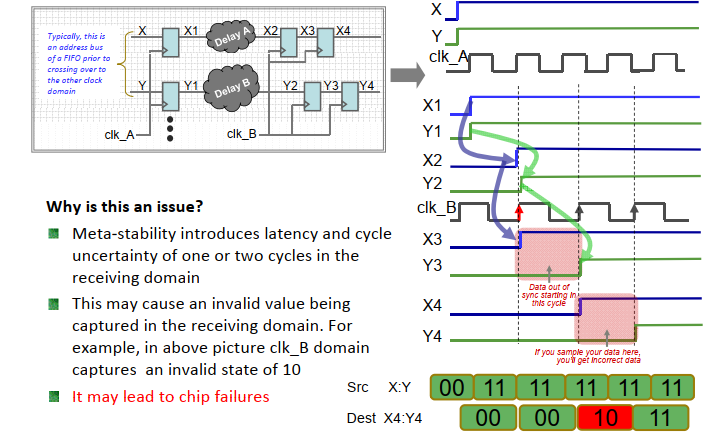

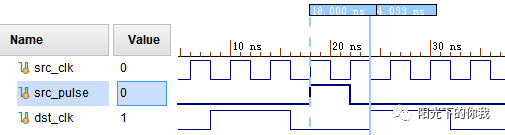

对于多bit信号,如果逐一使用两级同步,会带来一致性问题。如下图所示,x2,y2在clkb的上升沿附近翻转,导致x3和y3产生亚稳态,下一个周期,由于亚稳态稳定后的结果不确定,X4能够采样到1,而Y4采样到0,导致信号在传输过程中错拍。在下一个周期,由于信号不在时钟沿翻转,Y4能够采样到1.

很明显,xy从00变化到11,接收端能够采样到00-10-11

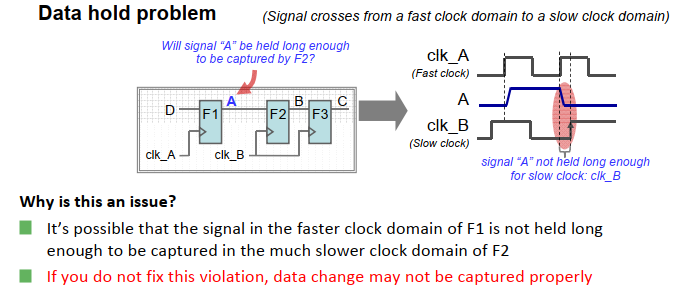

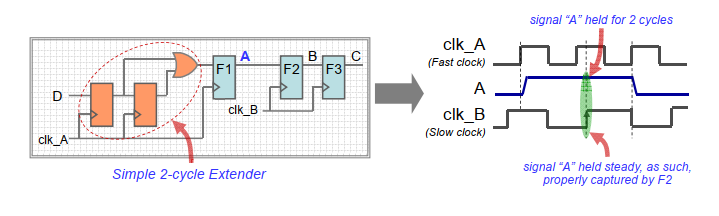

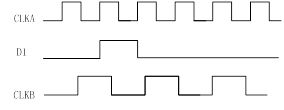

最后,信号的脉冲宽度也有要求。当快时钟域到慢时钟域,会存在漏采的问题。原本想要采样1,却只能收到0

一个简单的脉冲扩展电路如下,当然也可以使用握手协议。原时钟域打拍,取或,再寄存一拍(组合电路计算可能有毛刺)

审核编辑:刘清

-

数字电路

+关注

关注

193文章

1630浏览量

80949 -

触发器

+关注

关注

14文章

2024浏览量

61416 -

脉冲信号

+关注

关注

6文章

400浏览量

37130 -

bit

+关注

关注

0文章

48浏览量

32097

原文标题:两级同步的副作用

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

单bit信号的跨时钟域传输可以使用两级同步但后果呢?

单bit信号的跨时钟域传输可以使用两级同步但后果呢?

评论