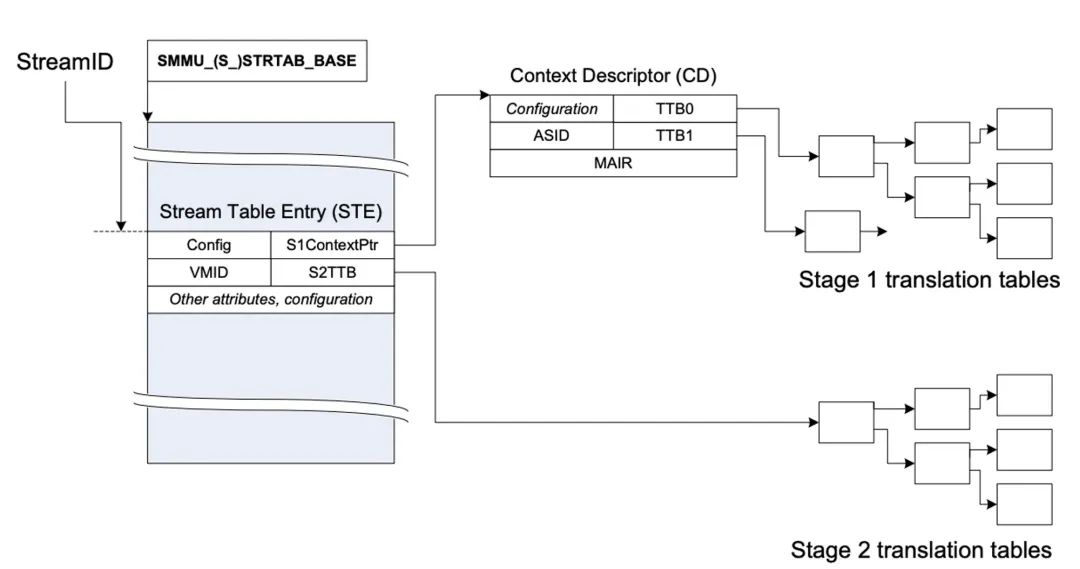

STE 包含每个stream的配置,指示:

• 是否启用来自device的流量。

• 是否进行stage 1 translation,获取stage 1 translation tables的配置。

• 是否进行stage 2 translation以及相关的stage 2 translation tables和VMID。

如果启用了stage 1,则STE中的S1ContextPtr字段包含一个或多个cd的基址。CD将StreamID与stage 1 translation table基指针(将VA转换为IPA)、per-stream配置和ASID关联起来。

如果多个devices与一个特定的虚拟机相关联,这意味着它们共享stage 2 translation tables,也就是说多个ste可能会映射到一个stage 2 translation table。

通常来说,Stream table和stage 2 translation table由hypervisor管理,而与devices相关的cd和stage 1 translation tables由guest OS管理。此外,hypervisor可以使用单独的hypervisor stage 1 translations。

在不使用hypervisor的情况下,裸机操作系统管理Streamtable和CDs。

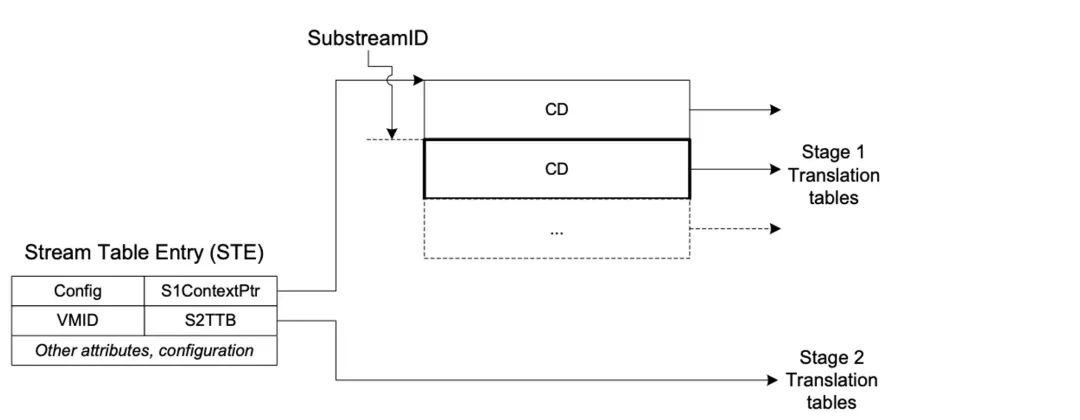

当输入事务启用SubstreamID时,SubstreamID索引CDs以选择 stage 1 translation context。如果没有提供SubstreamID,行为取决于ST.S1DSS:

当STE.S1DSS == 0b00,所有流量都有SubstreamID,不带有SubstreamID的输入事务则被中止并记录一个事件。

当STE.S1DSS == 0b01,没有SubstreamID的事务视为配置stage 1-bypass。

当STE.S1DSS == 0b10,没有SubstreamID的事务使用Substream=0的CD。在此配置下,SubstreamID=0的事务将被中止,并记录一个事件。

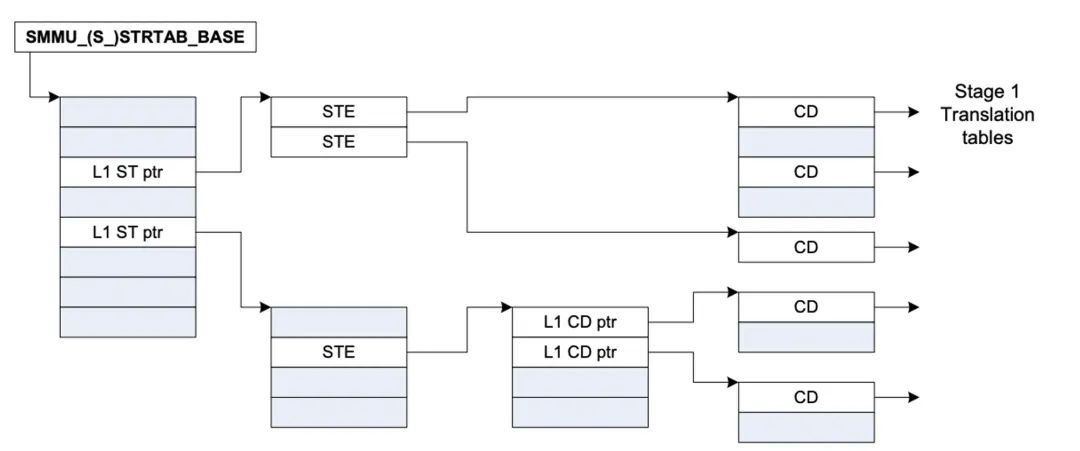

当stage 1被启用时,STE.S1ContextPtr字段给出了以下地址之一(由配置STE.S1Fmt和STE.S1CDMax)确定:

一张CD。

single-level table of CDs的起始地址。

L1CDs的起始地址,L1CD.L2Ptr都指向一个L2CDs的起始地址。L1CDs由SubstreamID的高位索引,L2CDs由SubstreamID的较低位索引。用于L1CDs和L2CDs索引的SubstreamID位由STE.S1Fmt配置。

当同时使用stage 1和stage 2时,S1ContextPtr和L2Ptr地址为IPA,仅使用stage1时为PA。

由CD和STE提供的ASID和VMID值是TLB tag的一部分,用于区分不同之间的地址空间,或者在接收到TLB invalidation操作时匹配无效的TLB。

Configuration structure example

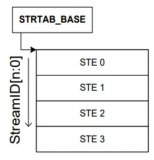

上图显示了一个示例配置,其中StreamID从linear Stream table中选择一个Ste,Ste指向stage2的translation table,并指向单个stage1的CD配置, 然后CD指向stage1的translation tables。

上图显示了一个配置,其中一个STE指向包含多个cd的数组。SubstreamID选择其中一个cd,最终确认要用的stage1页表。

Multi-level Stream and CD tables

上图显示了一个更复杂的布局,其中使用了一个multi-level Stream table。其中两个STE指向一张CD或一个CD数组,而第三个STE指向一个multi-level CD table 。

审核编辑:刘清

-

ARM

+关注

关注

134文章

9189浏览量

369992 -

操作系统

+关注

关注

37文章

6913浏览量

123912 -

虚拟机

+关注

关注

1文章

950浏览量

28527 -

TLB电路

+关注

关注

0文章

9浏览量

5281

原文标题:ARM SMMU Data structure之Context Descriptors

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ARM系列之SMMU总线资料合集

多个设备是否可以共用一个SMMU StreamID?

SMMU学习这一篇就够了

RK3588 ubunutu pcie虚拟化的SMMU配置在哪里修改呢?

ARM系统内存管理单元架构规范SMMU架构2.0版

1线文件结构-1-Wire File Structure

arm smmu的原理

arm smmu的原理与smmu驱动iommu框架

SystemVerilog中的Packed Structure

SMMU数据结构格式之Level 1 Stream Table Descriptor介绍

ARM SMMU Data structures之Stream Table

ARM SMMU Data structure之Context Descriptors

ARM SMMU Data structure之Context Descriptors

评论