摘要

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

高阻断电压、大功率密度、高转化效率是电力电子器件技术持续追求的目标,基于 4H-SiC 优异的材 料特性,在电力电子器件应用方面具有广阔的发展前景。围绕 SiC MOSFET 器件对外延材料的需求,介绍了 国内外主流的 SiC 外延设备及国产 SiC 衬底的发展,并重点介绍了宽禁带半导体电力电子器件国家重点实验 室在国产 150 mm(6 英寸)SiC 衬底上的高速外延技术进展。通过关键技术攻关,实现了 150 mm SiC 外延材料 表面缺陷密度≤0.5 cm-2,BPD 缺陷密度≤0.1 cm-2,片内掺杂浓度不均匀性≤5%,片内厚度不均匀性≤1%。基于自主外延材料,实现了 650~1 200 V SiC MOSFET 产品商业化以及 6.5~15 kV 高压 SiC MOSFET 器件的 产品定型。

引言

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

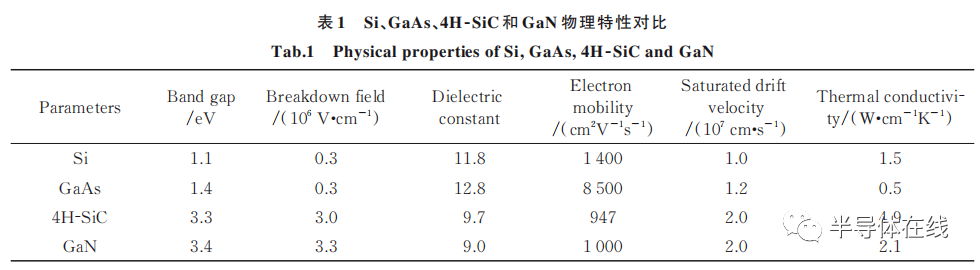

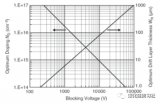

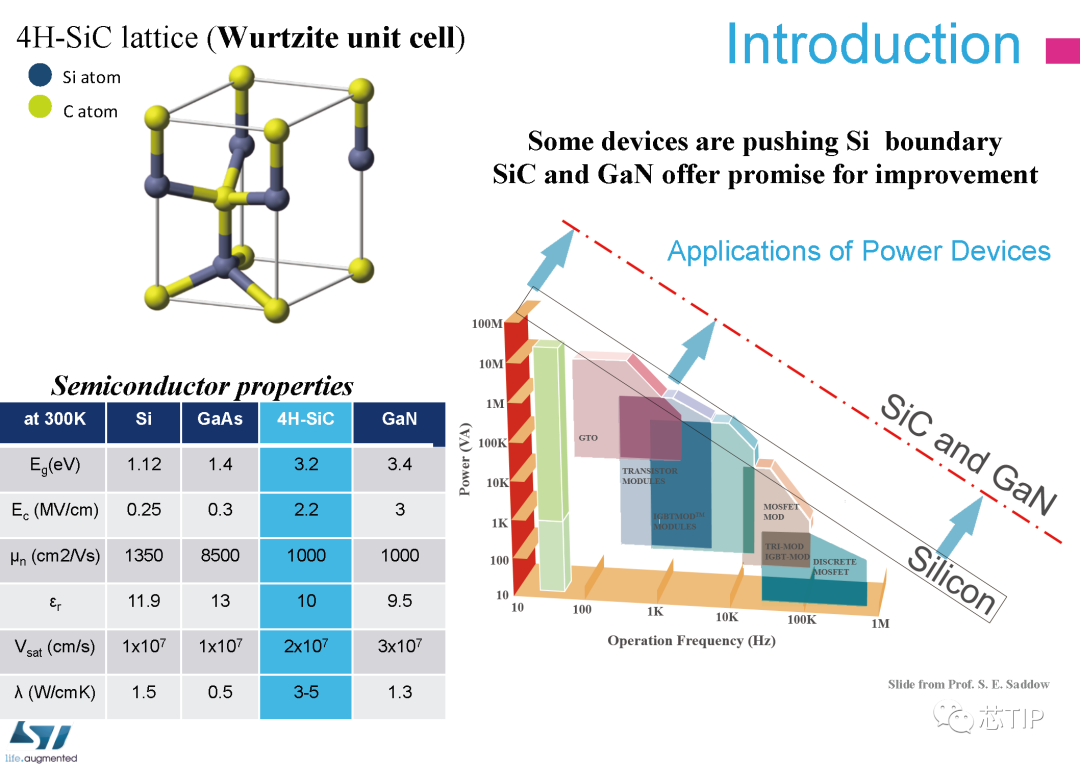

电力电子技术是能源与电能变换领域的核心 技术,能源的高效率转化是实现节能、环保、低碳经 济的关键,高压大容量电力电子器件是关键元件和 基础。长期以来,硅(Si)器件几乎统治了所有电力 电子系统的应用。这主要得益于材料和芯片制备 方面成熟的工艺技术优势。但是,Si 器件的性能已 经接近由其材料特性所决定的理论极限,性能的进 步提升十分受限。材料是芯片、器件性能实现的基 础,若要进一步提高电力电子装置与系统性能,需 诉诸于更优越的半导体材料。表 1 为典型半导体材料特性对比。

4H-SiC 作为第三代宽禁带半导体材料,与传统 的 Si 和 GaAs 材料相比,在热导率、临界击穿场强、 工作温度、饱和电子漂移速度等方面具有非常优异 的材料特性。其中,4H-SiC 的禁带宽度接近 Si 的 3 倍,且本征载流子浓度远低于 Si,使得 SiC 器件可以 工作在更高的温度;4H-SiC 的击穿场强比 Si高一个 数量级,相同器件耐压下的 SiC 器件可以设计较小 厚度和更高掺杂浓度的外延材料,大幅度降低器件 的导通电阻;4H-SiC 的热导率是 Si 的 3 倍以上,SiC 器件可以长时间在温度更高的环境下稳定地工作;4H-SiC 的饱和电子漂移速率是 Si 的 2 倍,使 SiC 器 件具备更高的工作频率。加入三代半交流群,加VX:tuoke08。SiC 具备独特的稳定性、 适用性和突出的性能,切合节能减排、智能制造、信 息安全等国家重大战略需求,被视为支撑新一代新 能源汽车、高速轨道列车、高压电网、光伏等产业创 新发展和转型升级的重点核心材料之一,已成为全 球半导体技术和产业竞争焦点。

几乎所有的 SiC 器件均在外延材料上实现,高 质量的 4H-SiC 同质外延材料是 SiC 器件研制的基 础,外延材料的性能直接决定了 SiC 器件性能的实 现。大电流、高可靠性 SiC 器件对外延材料的表面 形貌、缺陷密度以及掺杂和厚度均匀性等方面提出 了更苛刻的要求。大尺寸、低缺陷密度和高均匀性 的 SiC 外延材料已成为 SiC 电力电子产业发展的关 键。美国 SiC 行业巨头 Wolfspeed 公司已经推出了 150 mm(6 英 寸)和 200 mm(8 英 寸)的 多 层 结 构 4H-SiC 外延片,外延层厚度达到了 200 µm,无缺 陷面积≥95%,且仍在不断进行工艺优化。日本的 Renosac(原昭和电工)6 英寸 30 µm 以内 4H-SiC 外 延片的缺陷密度达到了≤0.5 cm-2,基平面位错密 度≤0.1 cm-2,2022 年 9 月开始批量出货 8 英寸 SiC 外延片。国内商业化的 SiC 外延公司瀚天天成、 广东天域半导体、普兴电子和中电化合物等目前已 实现 100~150 mm 4H-SiC 外延片批量生产,无缺陷面积达到 95% 以上,外延层厚度≤100 µm。另 外 ,厦 门 大 学 于 2023 年 3 月 成 功 实 现 了 200 mm 4H-SiC 外延生长,制备的 12 μm 厚外延片片内外延 厚 度 不 均 匀 性 2.3%,片 内 掺 杂 浓 度 不 均 匀 性 < 7.5%,表面缺陷密度≤0.5 cm-2 ,在国内首次公开报 道了 200 mm 4H-SiC 外延技术 。

1 国内外主流外延设备概况

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

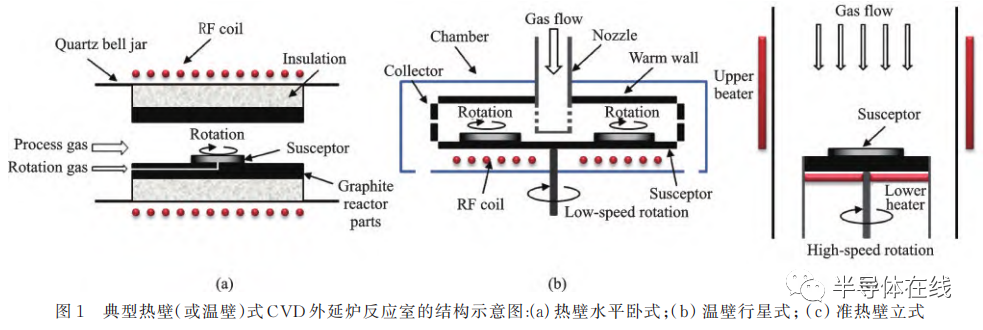

外延是指在单晶衬底上沿原来的晶轴方向生 长 出 新 单 晶 层 的 过 程 ,新 生 长 的 单 晶 层 即 外 延 层。现阶段,化学气相沉积(Chemical vapor deposition,CVD)是最为普及的 4H-SiC 同质外延方法, 已经广泛应用于工业化生产。4H-SiC CVD 外 延一般采用热壁或温壁式 CVD 设备,在较高的生长 温度条件(1 500~1 700℃)下保证了外延层 4H 晶型 SiC 的延续。热壁或温壁式 CVD 经过多年的发展, 按照进气气流方向与衬底表面的关系,反应室可以 分 为 水 平 卧 式 结 构 反 应 炉 和 垂 直 立 式 结 构 反 应 炉。热壁水平卧式 CVD、温壁行星式 CVD 以及 准热壁立式 CVD 是现阶段主流外延设备技术方案, 已实现商业化应用,其主要结构示意图如图 1所示。

热壁水平式 CVD 系统,一般为气浮驱动旋转的 单片大尺寸生长系统,易实现较好的片内指标,代 表性机型为意大利 LPE 公司的 Pe1O6,该机台可以 实现 900℃高温自动装取片,主要特点是生长速率 高、外延周期短、片内及炉次间一致性好等,在国内 市场占有率最高。根据 LPE 官方报道,结合主要用 户的使用情况,Pe1O6 外延炉生产的厚度 30 μm 以 下 100~150 mm(4~6 英寸)4H-SiC 外延片产品可 以 稳 定 达 到 如 下 指 标 :片 内 外 延 厚 度 不 均 匀 性 ≤2%,片内掺杂浓度不均匀性≤5%,表面缺陷密 度 ≤1 cm-2,表 面 无 缺 陷 面 积(2 mm×2 mm 单 元 格)≥90%。基于该设备生长的 SiC 外延材料, 最大外延厚度已达 200 μm 以上。国内晶盛机电、 中国电科 48 所、北方华创、纳设智能均开发了具有 类似功能的单片式 SiC 外延设备。2023 年 2 月,晶 盛机电发布了 6 英寸双片式 SiC 外延设备,该设备 通过对反应室石墨件的改造,采用上下层叠加的 方式,单炉可以生长两片外延片,且上下层工艺气 体可以单独调控,温差≤5℃,有效弥补了单片水平 式外延炉产能不足的劣势。

温壁行星式 CVD 系统,以行星排布基座的方 式,特点是单炉多片生长,产出效率较高。代表性 机 型 为 德 国 Aixtron 公 司 的 AIX G5 WW C(8× 150 mm)和 G10-SiC(9×150 mm 或 6×200 mm)系 列外延设备。据 Aixtron 官方报道,G10 外延炉生产 的厚度 10 μm 的 6 英寸 4H-SiC 外延片产品可以稳 定达到如下指标:片间外延厚度偏差±2.5%,片内 外 延 厚 度 不 均 匀 性 ≤2%,片 间 掺 杂 浓 度 偏 差 ±5%,片 内 掺 杂 浓 度 不 均 匀 性 ≤2%。截 至 目 前,此类机型在国内用户端使用较少,批量生产数 据不足,在一定程度上制约了其工程化应用。由于 多片式外延炉在温场和流场控制等方面技术壁垒 较高,国内同类设备开发仍处于研发阶段,尚无替代机型。

准热壁立式 CVD 系统,主要通过外部机械辅助 基座高速旋转,特点是通过较低的反应室压力有效 降低粘滞层厚度从而提高了外延生长速率,同时其 反应室没有能够沉积 SiC 颗粒的上壁,不易产生掉 落物,在缺陷控制上拥有先天优势,代表性机型为 日 本 Nuflare 公 司 的 单 片 式 外 延 炉 EPIREVO S6。据 Nuflare 报道,EPIREVO S6 设备的生长速率可以 达到 50 μm/h 以上,且外延片表面缺陷密度可控制 在 0.1 cm-2以下。在均匀性控制方面,2019 年 Nuflare 工程师 Yoshiaki Daigo 报道了采用 EPIREVO S6 生长的 10 μm 厚 6 英寸外延片的片内均匀性结 果,片内厚度和掺杂浓度不均匀性分别达到 1% 和 2.6%。目前,芯三代、晶盛机电等国内设备制造 商已经设计并推出了具有类似功能的外延设备,但还没有大规模的使用。

2 国内外单晶衬底进展

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

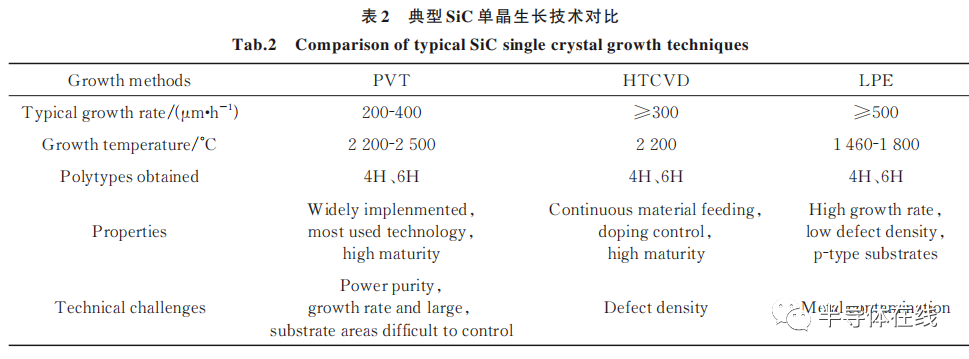

4H-SiC 晶体生长的技术主要有物理气相输运 法(PVT) 、高 温 化 合 气 相 沉 积 法(HTCVD)以及液相法(LPE)。表 2 从晶体尺 寸、生长速率、晶体缺陷与掺杂控制等单晶生长的 关键控制因素角度对比了典型的几种 SiC单晶生长技术的优点和缺点。现 阶 段 ,PVT 法 仍 是 4H-SiC 单晶生长技术中成熟度最高和商业化最广 的方法。

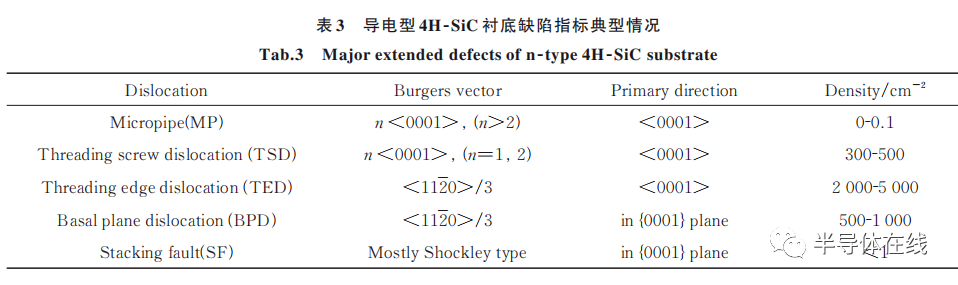

1987 年 , Cree 公 司(现 Wolfspeed)在 美 国 国 防 部 在 资 助 下 ,建 立 了 首 条 SiC 衬 底 生 产 线 ,于 1994 年 推 出 了 商 品 化 的 4H-SiC 单 晶 衬 底 。在 此 以后,随着 SiC单晶产品市场需求的增长,4H-SiC 单 晶 衬 底 的 技 术 发 展 也 进 入 了 高 速 期 。近 10 年 来,4H-SiC 衬底在晶片尺寸和缺陷指标等方面均 取得了极大的发展,如表 3 所示,随着商品化程 度 不 断 提 高 ,国 内 外 已 经 有 多 家 SiC 衬 底 生 产 公 司 推 出 具 有 不 同 导 电 类 型 的 大 尺 寸 4H-SiC 衬底。

以电力电子器件用 n 型 4H-SiC 衬底为例,美国 Wolfspeed 和 Coherent、日 本 Rohm(Sicrystal)以 及 韩国 SK Siltron 等公司均已实现 150 mm 4H-SiC 衬 底的批量供应。在 200 mm 4H-SiC 衬底方面:Wolfspeed 公司计划 2024 年将 4H-SiC 衬底生产能力提 高 10 倍,且主要生产 200 mm SiC 衬底;Coherent 公 司 计 划 5 年 内 将 包 括 200 mm SiC 衬 底 在 内 的 4H-SiC 衬底生产能力提高 5~10 倍;SK Siltron 公司 和 Sicrystal 公司分别计划于 2023 年和 2024 年启动 200 mm SiC 衬底量产。

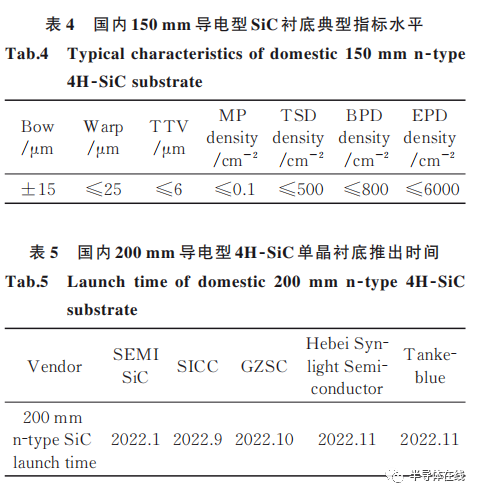

国 内 SiC 单 晶 衬 底 研 发 起 步 较 晚 ,但 近 年 来 发展十分迅速,以烁科晶体(SEMISiC)、天岳先进 (SICC)、南砂晶圆(GZSC)、同光股份(Hebei Syn-light Semiconductor)、天 科 合 达(Tankeblue)等 为 代表的衬底供应商已经实现 150 mm 单晶衬底的 稳定生产,典型指标水平如表 4 所示。同时,2022 年 国 内 衬 底 制 造 商 也 相 继 推 出 了 200 mm SiC 衬 底 样 品 ,如 表 5 所 示 ,预 估 2023 年 将 实 现 小 规 模 量产。

3 基于国产单晶衬底高速外延进展

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

依托中国电子 科 技 集 团 公 司 第 五 十 五 研 究 所 建 立 的 宽 禁 带 半 导 体 电 力 电 子 器 件 国 家 重 点 实 验 室 根 据 电 力 电 子 器 件 发 展 的 需 求 ,在 2018 年 启 动 了 基 于 国 产 150 mm 4H-SiC 单 晶 衬 底 的 外 延 生 长 技 术 开 发 。截 止 目 前 ,基 于 LPE Pe1O6 外 延 机 台 ,已 突 破 大 尺 寸 外 延 几 何 参 数 控 制 、外 延 缺 陷 控 制 、片 内 均 匀 性 提 升 等 关 键 技 术 ,实 现 了 基 于 国 产 单 晶 衬 底 的 150 mm SiC 外 延 材 料 工 程 化 应 用 。

3.1 几何参数控制

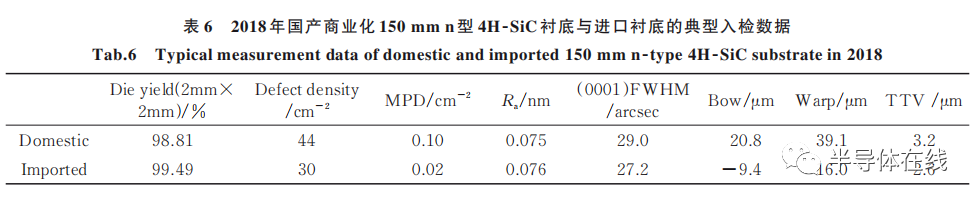

2018年国产商业化 150 mm n型 SiC 衬底与同类 进口衬底的入检数据如表 6 所示。国产衬底(0001) 半高宽(Full width at half maximum, FWHM)和表 面粗糙度(Ra )方面等指标方面与进口衬底水平相 当,但在几何(面型)参数方面存在明显差距,国产 150 mm 导电 SiC 衬底 Bow 和 Warp 值较大且外延后 数值增大更为明显、大多数超出 50 μm。

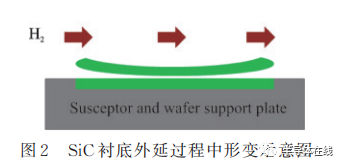

外延生长过程中,SiC 衬底背面直接与石墨基 座接触,被热传导加热。衬底正面有大量的氢气 流过,散热较快,衬底正反面存在温度差异,因此 高温状态下衬底趋向于碗状(正 Bow 值)分布,如 图 2 所示。因而,在国产衬底 Bow 和 Warp 值较大 的 时 候 ,工 艺 过 程 中 倾 向 于 采 用 负 Bow 值 的 SiC 衬 底 。此 外 ,在 外 延 生 长 之 前 对 背 面(C 面)进 行 抛光可极大地消除外延层(Si 面)的残余应力, 进而减小外延片形变。

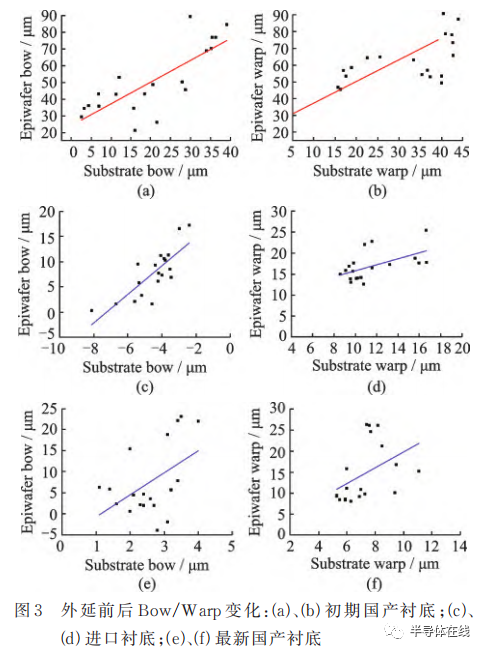

通 过 外 延 材 料 特 性 与 衬 底 参 数 之 间 的 关 联 性研究,明确了衬底晶体及加工质量是导致外延 前 后 几 何 参 数 指 标 退 化 的 关 键 因 素 。通 过 对 单 晶衬底进行高温退火以及背面抛光工艺优化,目 前 国 产 衬 底 外 延 前 后 几 何 参 数 及 工 艺 稳 定 性 均 达 到 了 与 进 口 衬 底 相 当 的 水 平 ,如 图 3 所 示 ,外 延 后 Bow 和 Warp 值 分 别 减 小 到 25 μm 和 30 μm 以内。

3.2 外延缺陷控制

4H-SiC 外延材料生长的核心技术首先是缺陷控制技术,尤其是对易导致器件失效或者引起可靠 性退化的缺陷控制技术。外延生长过程中衬底缺 陷延伸进入外延层的机理、衬底/外延层界面处的 缺陷转移转化规律、缺陷成核机制等方面的研究是 明确衬底缺陷和外延结构缺陷之间相关性的基础, 能够有效指导衬底筛选以及外延工艺优化。

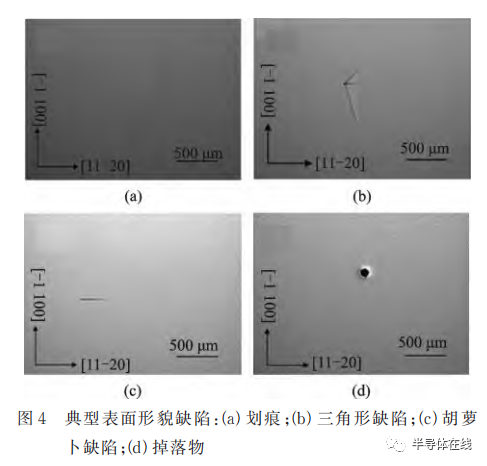

4H-SiC 外延材料中的外延缺陷包括表面形貌 缺陷和晶体结构缺陷。表面形貌缺陷借助显微镜 可通过肉眼直接观察,具有典型的形貌特征。表 面形貌缺陷主要包括:划痕(Scratch)、三角形缺陷 (Triangular defect) 、胡 萝 卜 缺 陷(Carrot defect) 、掉落物(Downfall)以及颗粒(Particle) 等 ,如 图 4 所 示 。在 外 延 过 程 中 ,外 来 颗 粒 异 物 、 衬底缺陷和表面损伤以及外延工艺偏差均可能影 响 局 部 台 阶 流 生 长 模 式 ,从 而 产 生 表 面 形 貌 缺陷。

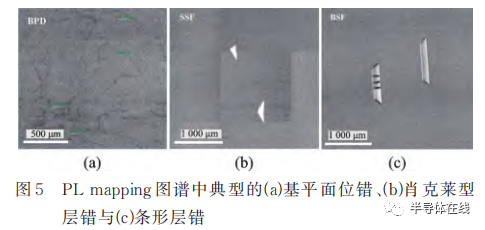

4H-SiC 外 延 层 中 的 晶 体 结 构 缺 陷 主 要 包 括 点、线及面缺陷,其中点缺陷包括杂质原子、空位、 间 隙 原 子 及 其 复 合 体 等 ,线 缺 陷 包 括 微 管 (MP)及 螺 位 错(TSD)、刃 位 错(TED)、 基平面位错(BPD) 等各类位错 ,面缺陷主要为 各类堆垛层错(SF)等。晶体结构缺陷除微管以 外,特征尺寸极小,无法借助显微镜直接观察。光 致发光成像(PL mapping)是检测基平面位错及堆 垛层错的有力手段 。在 PL mapping 图中基平 面 位 错 表 现 为 沿方 向 的 异 色 线 条 ,如 图 5 (a)所示;堆垛层错在 PL mapping 图有两种典型的形貌 :三角形和条形(梯形),如图 5(b)和(c)所 示。大部分三角形层错为肖克莱(Shockley)型层 错(SSF),大 部 分 条 形 层 错(BSF)为 弗 兰 克(Frank)型层错。

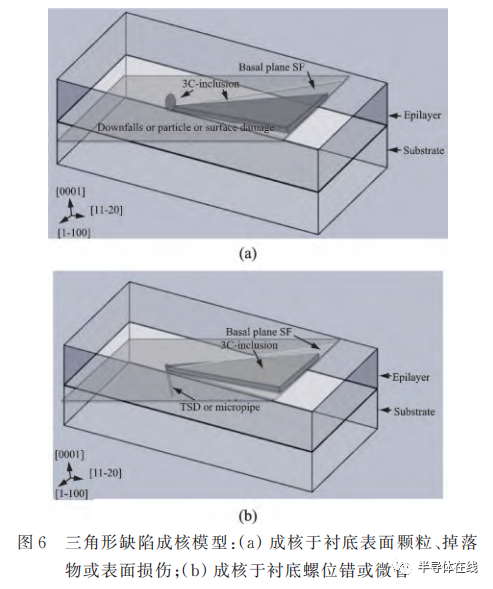

表 面 形 貌 缺 陷 中 掉 落 物 、三 角 形 缺 陷 和 胡 萝 卜型缺陷会导致芯片反向耐压失效,属于“致命” 缺陷。其中掉落物缺陷主要源自生长过程中反应 室上壁及侧壁的颗粒掉落,可以通过优化反应室 石墨耗材周期性维护流程进行优化。三角形缺陷 呈三角形形状,形貌中含有两条及两条以上的边 线 ,具 有 方 向 性 ,第 三 条 边 与方 向 几 近 成 90°。三 角 形 头 部 有 时 有 一 明 显 的 小 三 角 形 凹 痕 或掉落物。胡萝卜缺陷由基平面层错、棱柱面层 错和两者交界处的梯杆状位错组成,和三角形缺 陷一样,一般起始于外延层和衬底交界处,胡萝卜 缺陷具有类似胡萝卜的形貌,呈线型且一端较粗, 一 般 平 行 于方 向 。本 课 题 组 与 北 京 天 科 合达半导体股份有限公司合作,研究了三角形缺 陷以及胡萝卜缺陷的起源 。研究结果发现一 部分三角形缺陷成核于衬底中的螺位错或微管, 而 另 一 部 分 三 角 形 缺 陷 则 是 自 发 成 核 ,如 图 6 所 示 。通 过 降 低 缓 冲 层 C/Si 比 可 以 有 效 降 低 衬 底 中螺位错转化为三角形缺陷的几率且抑制三角形 缺 陷 沿[1-100]方 向 的 缺 陷 扩 展 。通 过 优 化 衬 底 刻蚀时间及温度可以有效消除由衬底表面加工损 伤引入的划伤周边台阶聚并形貌以及三角形缺陷 的成核几率。

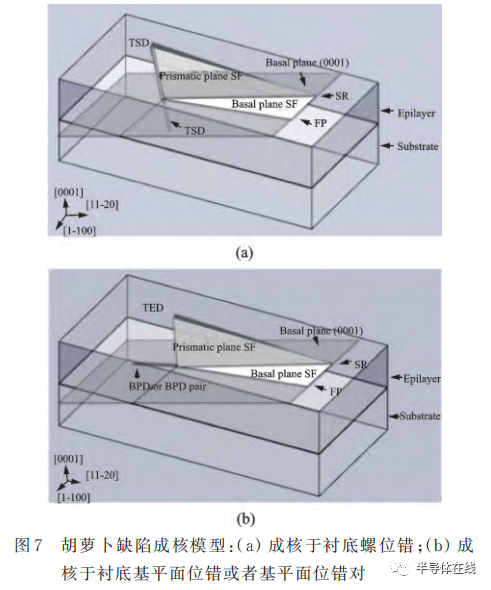

胡萝卜缺陷主要来源于衬底螺位错和基平面 位错等晶体缺陷,如图 7 所示。正常衬底和会产生 大量胡萝卜缺陷的衬底,在表面散射光频道分析图 中存在明显差异。基于上述研究结果,通过对同晶 锭衬底的无损筛选,可以有效剔除会导致胡萝卜缺 陷密度超标的衬底。

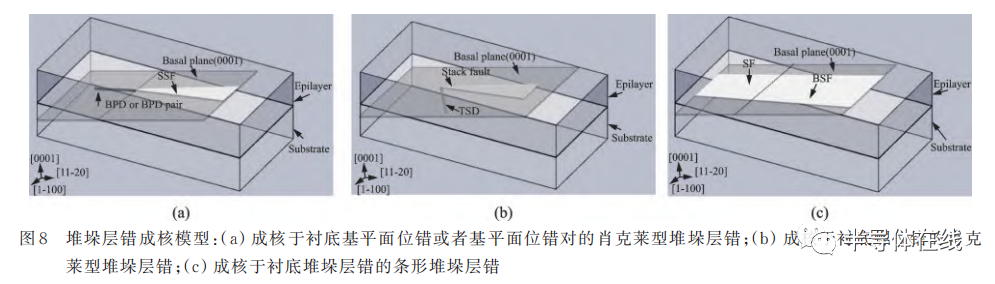

堆垛层错会降低器件击穿电压以及增大反向漏 电,影响器件的性能及可靠性。外延层中堆垛层错,主要源自衬底缺陷,如图 8所示。其中 BSF主要成核 于衬底中的堆垛层错,SSF主要成核于衬底中的 BPD 或 TSD。源自衬底缺陷的堆垛层错在 PL-mapping图 像中,沿[11-20]方向的特征尺寸长度与外延层的厚度 成 正 比 。源 自 外 延 工 艺 偏 差 的 堆 垛 层 错 在 PL-mapping 图像中具有相对较小的特征尺寸长度。通过优化衬底氢气刻蚀工艺、降低初期外延速率、提 高生长温度等工艺优化来降低层错密度。

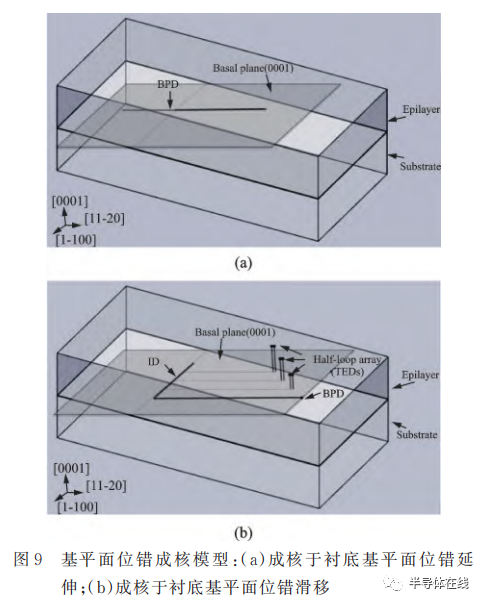

BPD 在电子-空穴复合作用下会发生不全位错 滑移,在双极型器件有源区或者 MOSFET 体二极 管区域内扩展形成新的肖克莱层错,增加器件的导 通电阻,导致器件正向开启电压漂移,严重影响器 件可靠性 。外延层中的 BPD 主要来源自衬底 BPD 位错延伸,如图 9 所示。大部分衬底 BPD 在 外延界面处转化为具有相同伯格斯矢量且弹性势 能更低的 TED。通过中断生长以及复合缓冲层设 计可以进一步提高 BPD-TED 的转化率。生长过 程中温度、掺杂浓度差异引入的剪应力也会诱发界 面位错(ID)滑移并产生基平面位错延伸进入外延 层。通过优化缓冲层 C/Si 比、温度以及外延速率 切 换 方 式 等 工 艺 条 件 可 以 降 低 此 类 基 平 面 位 错 密度。

3.3 均匀性控制

在水平式外延炉中,源沿进气方向在单晶衬底 径向的耗尽造成了外延片片内各点厚度及掺杂浓度 的差异。如果源的耗尽接近线性耗尽,通过基座气 浮旋转便可以有效消除由源分布引起的不均匀性。然而大部分源的耗尽方式更加接近于二次函数或指 数型耗尽,通过基座气浮旋转并不能有效消除由源 分布引入的不均匀性 。在前期的研究工作中,本 课题组通过正交实验,明确了 C/Si比、Cl/Si比、主氢 流量、生长温度、三路气体比等工艺参数对 SiC 外延 厚度和掺杂浓度均匀性指标影响的主次顺序,有效 提高了 100 mm SiC 外延片的厚度及浓度不均匀性。

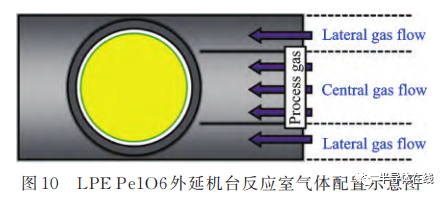

当外延尺寸上升至 150 mm 之后,外延片片内 掺杂浓度和厚度均匀性对比 100 mm 外延片存在明 显退化,主要原因在于外延片中心点和最边缘点厚 度及掺杂浓度差异较大。借助反应室的特殊的气 路设计可以对 150 mm 外延片的片内均匀性进行有 效调控。如图 10 所示,反应室中央气路对应外延片 4 英寸区域,侧边气路对应 150 mm 边缘区域,通过 加大侧边气路氢气流量配比,可以在提高边缘区域 外延厚度的同时降低中心区域外延厚度,进而可实 现优化外延厚度均匀性的目的。同时通过在侧边气路通入额外的掺杂源,补偿边缘掺杂浓度,可实 现优化掺杂浓度均匀性的目的。

3.4 基于自主外延材料的 SiC MOSFET 研制

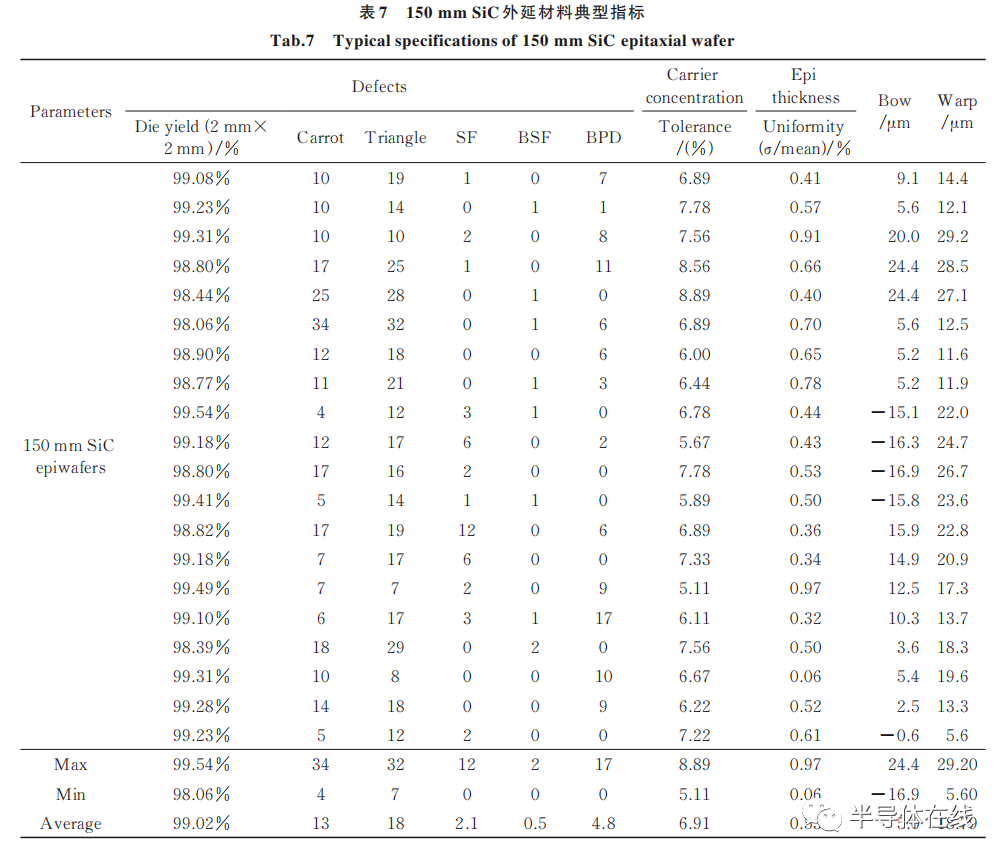

通过上述关键技术攻关,宽禁带半导体电力电 子器件国家重点实验室基于国产单晶衬底的 4HSiC 同质外延材料典型外延指标如表 7 所示,达到了 国际主流产品水平。

采用自主 4H-SiC 同质外延材料,2019 年宽禁 带 半 导 体 电 力 电 子 器 件 国 家 重 点 实 验 室 基 于 150 mm 工 艺 平 台 开 发 了 G1 1 200~1 700 V SiC MOSFET 器 件 ,2022 年 开 发 了 G2 650~1 200 V SiC MOSFET 器件,栅压 18 V 驱动时 1 200 V 器件 比导通电阻较 G1 降低 35%。G2 SiC MOSFET 产 品适用于车载充电器(On board charger,OBC)、主 驱电机控制器和光伏储能等领域。SiC MOSFET 系 列 产 品 中 OBC 装 车 量 超 过 一 百 万 台 。采 用 1 200 V/25 mΩ SiC MOSFET 芯片的 400 A 三相全 桥 SiC 功率模块,完成万公里路实验验证。光伏升 压变换器采用 1 200 V SiC MOSFET 实现了低开关 损耗与高开关频率,储能端使用 SiC MOSFET 提升 了 功 率 转 换 效 率 ,1 200 V/75 mΩ 和 40 mΩ SiC MOSFET 产品出货量近百万只。

采用平面型 MOS 结构,基于自主材料研制了芯 片尺寸为 8.0 mm×8.0 mm 的 6.5 kV SiC MOSFET 器件,通过终端及外延结构优化,实现了击穿电压 7 600 V 和 低 导 通 电 阻 160 mΩ。国 家 电 网 采 用 6.5 kV/400 A SiC MOSFET 功 率 模 块 ,研 制 出 35 kV/5 MW 全 SiC 电力电子变压器,并在柔性变电 站示范应用 。相比 Si 器件装置,SiC 基变压器体 积、重量、损耗减少 90% 以上,有望极大推动我国高 压输变电技术发展。目前基于自主材料研制的 SiC MOSFET芯片样品最高耐压为 15 kV,该芯片尺寸为 9.2 mm×9.2 mm,实现了击穿电压 16 kV和导通电阻 650 mΩ。15 kV SiC MOSFET 的导通电阻 RON,SP可 达 204 mΩ·cm2,已接近单极型 SiC器件的理论极限。

4 结论

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

国产 SiC 外延设备和单晶衬底取得了显著的进 展,国内企业已经能够批量生产 150 mm SiC 外延材 料并已有 200 mm SiC 外延片样品的报道,与国外龙 头企业差距不断缩小。基于国产单晶衬底,宽禁带 半导体电力电子器件国家重点实验室完成了外延 生长关键技术攻关,150 mm SiC 外延材料产品表面形貌缺陷密度≤0.5cm-2,BPD 密度≤0.1cm-2,片 内掺杂浓度不均匀性≤5%,片内厚度不均匀性≤ 1%,达到国际主流产品水平。基于自主外延材料 研制的 650~1 200 V SiC MOSFET 器件已批量应 用于新能源汽车车载充电器,后续将进一步拓展应 用至主驱电机控制器。

对 标 国 际 先 进 水 平 ,国 内 商 业 化 的 150 mm 4H-SiC 单晶衬底还需要进一步提高技术能力,降 低 位 错 密 度 并 提 高 单 晶 生 长 及 加 工 良 率 。针 对 车 规 级 MOSFET 器 件 应 用 ,在 保 证 现 有 致 命 型 (Killer)外 延 缺 陷 控 制 水 平 的 基 础 上 ,需 与 器 件 端联合攻关,深入研究表面微坑、堆垛层错、基平 面位错等非致命型(Nonkiller)外延缺陷导致器件 可 靠 性 退 化 的 机 理 ,提 出 对 应 的 筛 选 和 控 制 方法。

新能源汽车、光伏和储能等中低压应用推动了 SiC 电力电子产业快速增长,在电网和轨道交通等 高压领域,SiC 电力电子的应用优势也初步彰显,亟 待联合攻关实现批量工程应用。高可靠、大电流密 度的 SiC MOSFET 器件是实现持续增长的关键,外 延是链接单晶衬底及器件的核心。全产业链需要 抓住市场爆发和国产化替代的机遇期,持续提升单 晶衬底、外延材料和器件关键技术能力,缩小与国 际龙头企业的技术和产业化水平差距。

来源:固体电子学研究与进展第 43 卷 第 2 期

作者:赵志飞1,2 王 翼1,2 周 平1,2 李士颜1,2 陈谷然1,2 李 赟1,2∗∗

(1 南京电子器件研究所,南京,210016)

(2 宽禁带半导体电力电子器件国家重点实验室,南京,210016)

审核编辑:汤梓红

-

MOSFET

+关注

关注

147文章

7511浏览量

215220 -

半导体

+关注

关注

335文章

27970浏览量

225146 -

天线

+关注

关注

68文章

3233浏览量

141399 -

SiC

+关注

关注

30文章

2975浏览量

63334 -

5G

+关注

关注

1357文章

48571浏览量

567270

原文标题:【半导光电】基于国产单晶衬底的150 mm 4H-SiC 同质外延技术进展

文章出处:【微信号:今日光电,微信公众号:今日光电】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

科锐开发出直径150mm的n型4H-SiC外延晶圆

改善4H-SiC晶圆表面缺陷的高压碳化硅解决方案

150mm晶圆是过去式了吗?

尖嘴钳150mm是指什么

4H-SiC离子注入层的欧姆接触的制备

基于简单的支架多片4H-SiC化学气相沉积同质外延生长

简述碳化硅衬底的国产化进程

8英寸导电型4H-SiC单晶衬底制备与表征

国产CVD设备在4H-SiC衬底上的同质外延实验

半导体衬底和外延有什么区别?

基于国产单晶衬底的150mm 4H-SiC同质外延技术进展

基于国产单晶衬底的150mm 4H-SiC同质外延技术进展

评论