电源管理是电子系统中的的一个基本模块。智能手机、电脑和我们所熟知的绝大多数电子产品都需要这个模块去实现本身的功能。随着人们对电子产品便携性的追求,计算能力的增长,以及传感器的多样化,电源管理设计有了更高的要求。

为了满足新的电源设计上的更高的要求,我们不能以为只要有了一个性能良好的电压轨,就不需要考虑其他部分的电源设计。我们在电源设计中最应该考虑哪些问题?为一个已知的负载供电时,电源的哪个参数至关重要?如何通过已知信息推断电源在各种不同条件下的性能?

本电子书将帮您解决上述问题。使用低压降稳压器(LDO)是在维持小的输出输入电压差的情况下,把一个较高电压输入,转换为一个略低的稳定输出电压的常见方法。在大多数情况下,LDO都易于设计和使用。然而,目前的主流应用通常包括多个模拟和数字系统,我们将根据这些系统的本身特性以及工作条件来选择最适合这个应用的LDO。

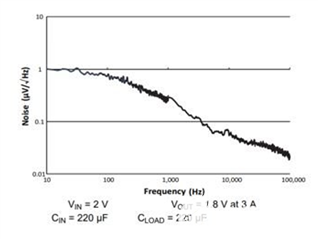

压降

低压降稳压器(LDO)的典型特性必然是压降。毕竟,其名称及其缩写由此而来。从根本上讲,压降描述的是正常稳压所需的VIN和VOUT之间的最小差值。但是考虑到各种因素之后,它会迅速发生细微的变化。压降对于实现高效运行及生成余量有限的电压轨至关重要。

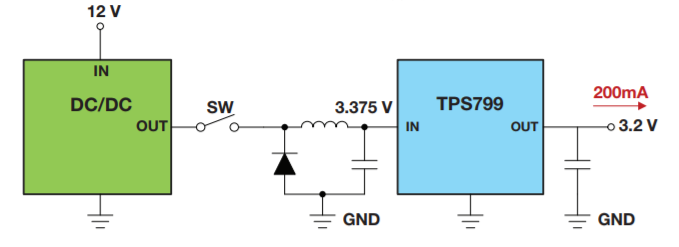

图 1:在压降状态下工作的 TPS799

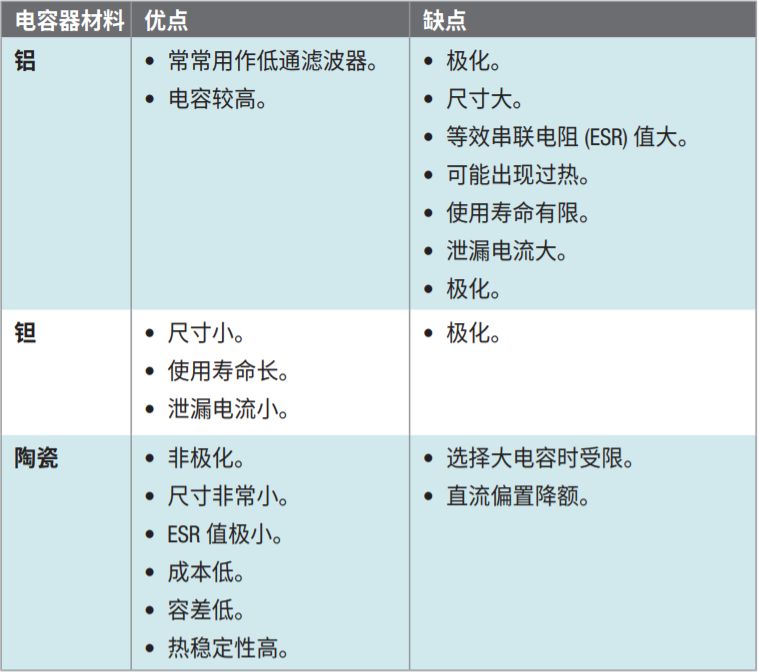

电容器是用于储存电荷的器件,其中包含一对或多对由绝缘体分隔的导体。电容器通常由铝、钽或陶瓷等材料制成。各种材料的电容器在系统中使用时具有各自的优缺点,如表1所示。陶瓷电容器通常是理想的选择,因为其电容变化最小,而且成本较低。

表 1:不同材料电容器的优缺点

电容器是用于储存电荷的器件,而电容是指储存电荷的能力。在理想情况下,电容器上标注的值应与其提供的电容量完全相同。但我们并未处于理想情况下,不能只看电容器上标注的值。电容器的电容可能只有其额定值的10%。这可能是由于直流电压偏置降额、温度变化降额或制造商容差造成的。

热性能

若将热性能纳入考量,可以进一步提高应用的性能。低压降稳压器(LDO)的特性是通过将多余的功率转化为热量来实现稳压,因此,该集成电路非常适合低功耗或VIN与VOUT之差较小的应用。考虑到这一点,选择采用适当封装的适当LDO对于最大程度地提高应用性能至关重要。这一点正是令设计人员感到棘手之处,因为最小的可用封装并不总能符合所需应用的要求。

静态电流

当您拿起几乎没用过的电子设备,却发现电池电量几乎或完全耗尽时,该令人多么恼火!如果您的设备只是处于待机或休眠状态,出现这种情况可能是因为存在很小但很重要的一种参数:静态电流。

静态的定义为“非活动或休眠的状态或阶段”。因此,静态电流 IQ 是系统处于待机模式且在轻载或空载条件下所消耗的电流。静态电流通常会与关断电流相混淆,关断电流是指设备处于关闭状态但系统仍与电池相连的情况下所消耗的电流。不过,这两种参数在任何电池电流消耗低的设计中都很重要。静态电流适用于大多数集成电路 (IC) 设计,其中放大器、升降压转换器和低压降稳压器 (LDO) 都会影响消耗的静态电流量。

电流限制

在一些外部条件和情况下,LDO 可能会出现意外的高流耗。如果此高电流传输到其他正被供电的电子系统,会对大多数电子系统以及主机电源管理电路造成损害。选择具有电流限制和内部短路保护的 LDO,将有助于防止产生这种不良影响,并在设计整体电源管理模块时提供额外保护。

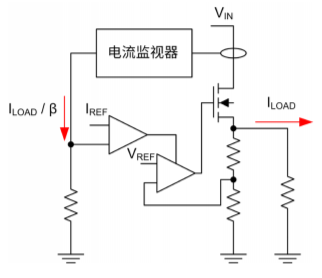

LDO 中的电流限制定义为,建立所施加电流的上限。与恒流源不同,LDO 按需输出电流,同时还会控制调节的总功率。电流限制通过用于控制 LDO 内输出级晶体管的内部电路实现;见图2。这是一种典型的 LDO 限流电路,由于达到限值后该电路会突然停止输出电流,通常被称为“砖墙”电流限制。此内部电路中,LDO 测量反馈的输出电压,同时测量输出电流相对于内部基准 (IREF) 的缩放镜像。

图2:LDO 内部限流结构

防止出现反向电流

在大多数低压降稳压器(LDO)中,电流沿特定方向流动,电流方向错误会产生重大问题!反向电流是指从VOUT流向VIN而不是从VIN流向VOUT的电流。这种电流通常会穿过LDO的体二极管,而不会流过正常的导电通道,有可能引发长期可靠性问题甚至会损坏器件。

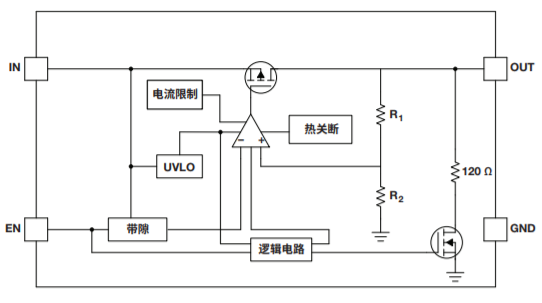

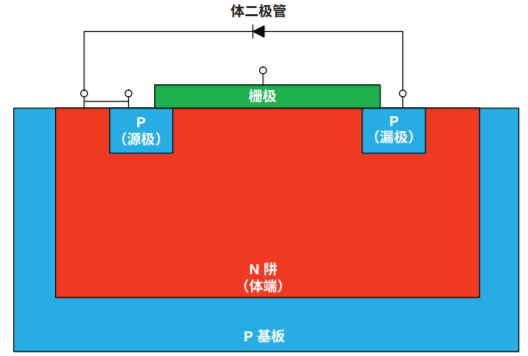

LDO主要包括三个组成部分(见图3):带隙基准、误差放大器和导通场效应晶体管(FET)。在典型应用中,导通FET与任何标准FET一样,在源极和漏极之间传导电流。用于产生FET体的掺杂区(称为块体)与源极相连;这会减小阈值电压变化量。

图3:LDO 功能方框图

将块体与源极相连有一个缺点,即会在FET中形成寄生体二极管,如图4所示。此寄生二极管被称为体二极管。在这种配置中,当输出超过输入电压与寄生二极管的VFB之和时,体二极管将导通。流经该二极管的反向电流可能会使器件温度升高、出现电迁移或闩锁效应,从而导致器件损坏。在设计LDO时,务必要将反向电流以及如何防止出现反向电流纳入考量。有四种方法可以防止反向电流:其中两种在应用层实施,另外两种在集成电路(IC)设计过程中实施。

图 4:P 沟道金属氧化物半导体 (PMOS) FET 的截面图

电源抑制比

低压降稳压器 (LDO) 最受欢迎的优势之一是,能够衰减开关模式电源生成的电压纹波。这对于数据转换器、锁相环 (PLL) 和时钟等信号调节器件而言尤为重要,因为含有噪声的电源电压会影响这类器件的性能。电源抑制比 (PSRR) 仍然常被误认为是单个静态值。PSRR 是一个常见技术参数,在许多 LDO 数据表中都会列出。它规定了特定频率的交流元件从 LDO 输入衰减到输出的程度。

噪声

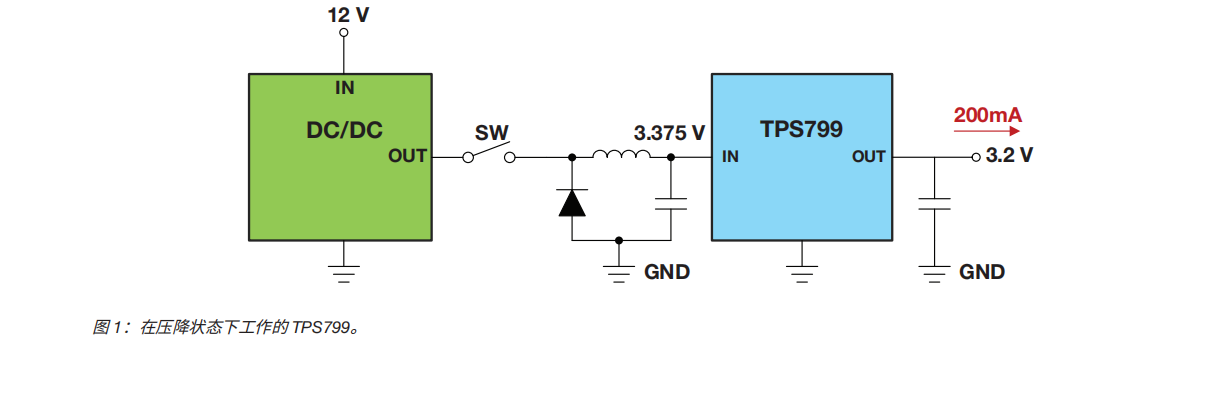

要获得干净的直流电源,使用低压降稳压器 (LDO) 过滤由开关模式电源生成的纹波电压并不是需要考量的唯一事项。由于LDO 为电子器件,它们本身会产生一定量的噪声。要生成不会影响系统性能的干净电源轨,选择低噪声 LDO 并采取措施降低内部噪声是不可缺少的环节。

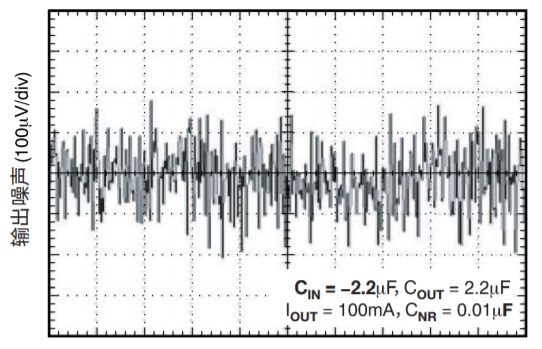

理想的LDO 将生成没有交流元件的电压轨。可惜的是,LDO 本身也会向其他电子器件一样产生噪声。图 5 所示为这种噪声在时域中的表现。

图 5:含噪声电源的示波器截图

在时域中执行分析十分困难。因此,可通过两种主要方法来查看噪声:跨频率查看噪声和查看积分值形式的噪声。

添加前馈电容器可以改善噪声性能、稳定性、负载响应和 PSRR。当然,必须慎重选择电容器以保持稳定性。当与降噪电容器配合使用时,可以大大改善交流性能。本文仅仅介绍了需要牢记的一些方法,可以帮助用户优化电源。

审核编辑:刘清

-

电容器

+关注

关注

64文章

6971浏览量

108613 -

电源管理

+关注

关注

117文章

8664浏览量

148263 -

ldo

+关注

关注

35文章

2468浏览量

160586 -

场效应晶体管

+关注

关注

6文章

425浏览量

20722 -

低压降稳压器

+关注

关注

1文章

111浏览量

9825

原文标题:看懂低压降稳压器(LDO),一篇就够了!

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

看懂低压降稳压器(LDO)一篇就够了

看懂低压降稳压器(LDO)一篇就够了

评论