摘要

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

随着物联网时代的来临,传统的传感器芯片与存算芯片相分离的架构已难以满足实际场景的 需求。3D集成技术能够缩短传感器芯片与存算芯片间的物理距离,实现功能扩展,提升系统能效。晶圆级集成由于对准精度高和互连密度大,一直是学界和产业界的研究热点。文章对晶圆级集成 技术中的两种主流工艺,包括硅通孔和混合键合工艺,进行了系统性介绍;并结合国内外多个研究 机构的最新进展,对其发展方向进行了展望,以实现适用于感存算一体化芯片的晶圆级集成工艺。

0 引言

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

进入物联网时代,各种传感器终端的数量呈几 何倍数增长,需要对海量的数据进行处理,来获取有 用的信息。现有传感器一般将采集到的信号进行压 缩编码后,传输到云端计算机,在云端解压后,基于 部署在云端的模型实现信号的进一步处理,如目标 识别、目标检测等。这种模式需要经过压缩、传输、解压缩、模型计算等多个步骤,会带来延时、隐私安 全、功耗、成本等一系列问题,难以满足实际需求。将传感器芯片与存算一体化芯片进行三维集成,可 以大大简化系统设计和信息处理过程,节省系统功 耗,实现高性能感存算一体化芯片。

三维集成工艺的好坏会对整个集成单元的电学 性能、热学性能和力学性能产生影响,直接关系到最 终产品的成功与否。三维集成主要有晶圆级集成和 芯片间互连两种技术路线,晶圆级集成由于其对准 精度高且互连密度大,成为产业界和学界的研究热 点。目前晶圆级三维集成的主流工艺主要有硅通孔(through-silicon via,TSV)和混合键合( hybrid bond⁃ ing,HB)两种。

1硅通孔工艺

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

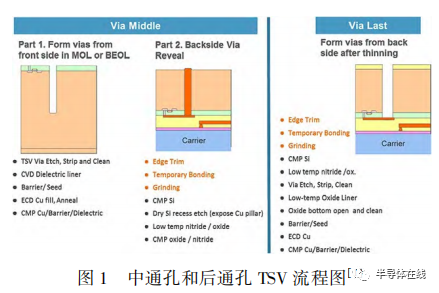

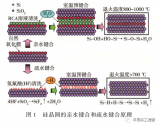

TSV是一种穿透硅基板或芯片的垂直互连结 构,用来完成上下晶圆或芯片间的电学连接。TSV技术依据通孔形成的顺序可以分为先通孔( via first)、中通孔(via middle)和后通孔(via last)三种工 艺类型。图1为中通孔和后通孔的流程示意图,主要包含以下几个步骤:通孔的形成、通孔的填充以 及填充后的表面处理。TSV作为一种3D集成技 术,已广泛应用在图像传感器等领域中。

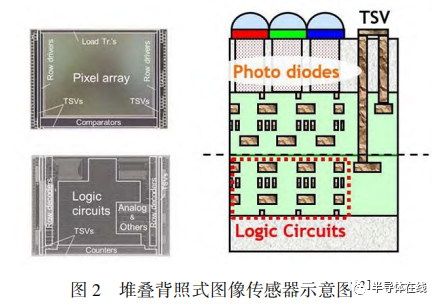

Sukegawa等人开发了一种堆叠背照式图像 传感器( backside illumination - CMOS image sensor, BI-CIS),包括传统的背照式图像传感器技术和65 nm的标准逻辑技术。新型的堆叠工艺将传统的 支撑基板替换为逻辑基板,能够采用独立于CIS工 艺的技术制作先进的逻辑电路。如图2所示,整个 芯片由两部分组成,芯片的上半部分由传统的90 nm的1P4M BI-CIS工艺形成;芯片的下半部分由65 nm的1P7M逻辑工艺形成。上部CIS芯片和 下部逻辑芯片完成堆叠之后,在芯片的顶部制作彩 色滤光片和微透镜,顶部和底部之间通过TSV实现电学连接。

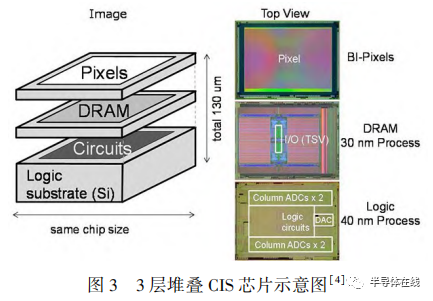

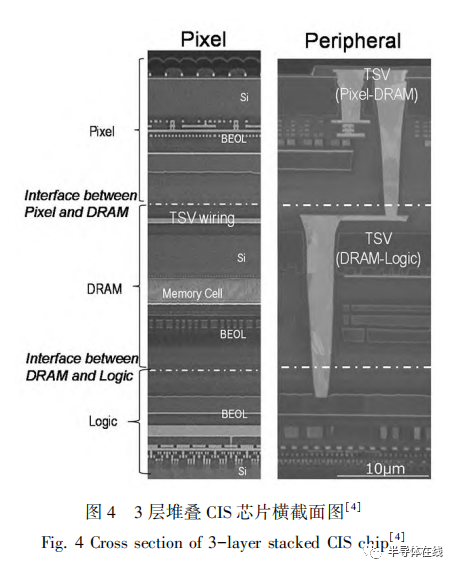

Tsugawa等人在像素-逻辑两层堆叠背照式 图像传感器的基础上,在中间层加入DRAM作为缓 存,开发了一种集成像素晶圆、DRAM晶圆和逻辑晶 圆的晶圆级集成工艺,如图3和图4所示。在单独 制作像素、DRAM、逻辑晶圆后,首先将DRAM晶圆 倒置与逻辑晶圆面对面键合。接下来,将DRAM晶 圆的Si基板减薄,并形成用于连接DRAM晶圆和逻 辑晶圆的TSV布线。最后,将像素晶圆倒置并将其 键合到DRAM/逻辑堆叠晶圆上,将像素晶圆的背面 减薄,形成TSV。通过在像素晶圆逻辑晶圆之间堆 叠DRAM晶圆,有助于减少I/ O口数目,降低功耗,并且实现对高速镜头的捕捉。

2混合键合工艺

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

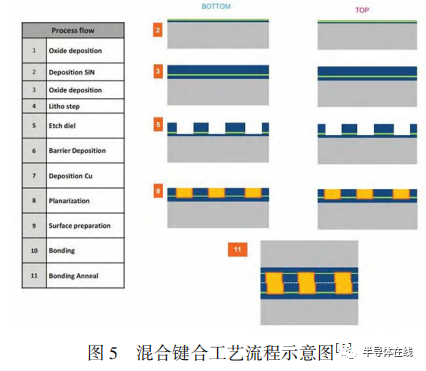

相较于硅通孔工艺,混合键合工艺更为简单,混 合键合可以同时实现两个基板间的物理连接和电气 连接,并且能够以密度更高的垂直互连实现更小的 尺寸。图5为混合键合工艺的流程示意图,其关键 步骤包括铜通孔的制作、表面平坦化、表面激活、对 准以及键合后退火。首先,通过深反应离子刻蚀来 形成通孔,利用电镀方式填充铜。再通过化学机械 研磨进行表面平坦化,表面平整度和铜通孔的凹陷 度会对最终键合界面质量产生重要影响。接下来利用等离子体对表面进行激活,为预键合做准备。上 下晶圆对准,完成预键合,经过退火操作,来进一步 促进铜通孔键合面的扩散,完成良好的电学连接。铜-铜混合键合被认为是用于20 μm间距以下最有 前途的3D集成解决方案之一,已成为3D集成的 主流技术之一。

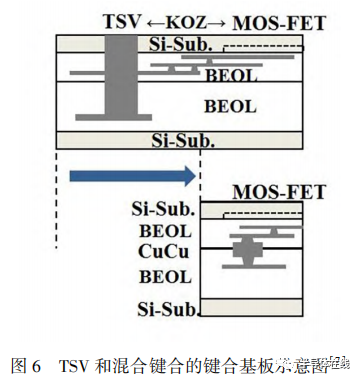

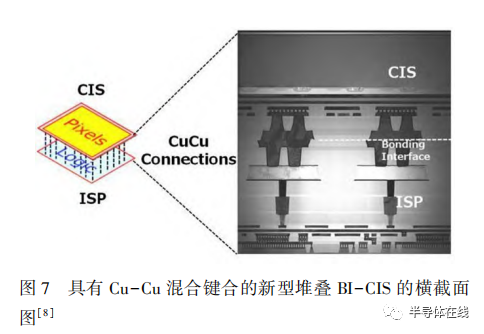

Kagawa等人利用混合键合工艺成功制造了2250万像素、1 / 2.6尺寸的背照式图像传感器,其中 混合键合间距为4 μm。如图6所示,与传统采用硅 通孔(TSV)工艺进行层间连接的堆叠背照式传感器 不同,铜-铜混合键合能够实现细间距和大规模连 接,可以提高电路设计灵活性,并进一步减小芯片尺 寸。由图7可以观察到,退火后的上下侧铜通孔连 接牢固,键合界面无空洞,表现出良好的电学互连和 可靠性。

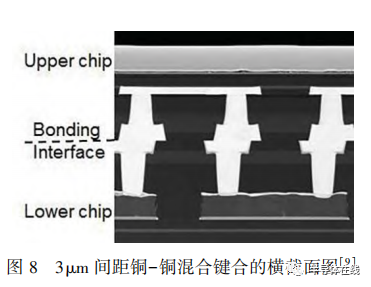

之后,Kagawa等人通过进一步优化工艺,提 高晶圆对准精度,成功在300 mm晶圆上将混合键 合间距缩小至3 μm,并且使键合对达到300万。其 中,铜通孔的尺寸为1.5 μm,通孔间空白区域尺寸 为1.5 μm,新的键合工艺成功将对准误差控制在0. 5 μm以内,保证了键合连接的稳定性。如图8所 示,每对Cu-Cu键合牢固地连接上芯片和下芯片,键合界面没有任何缺陷或空隙。

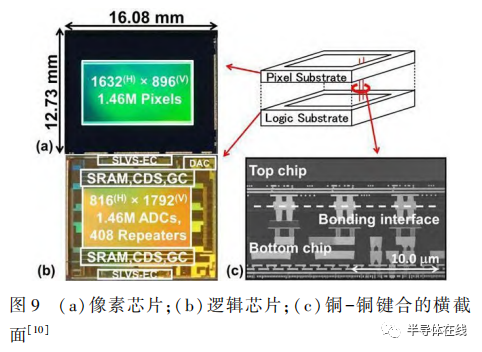

Sakakibara等人通过铜-铜混合键合工艺,实现CIS芯片与逻辑芯片的像素级连接,如图9所 示。CIS芯片采用90 nm的1P4M工艺制造,像素间 距为6.9 μm;逻辑芯片采用相对先进的65 nm的1P7M工艺制造。通过Cu-Cu连接直接将ADC单元集成在像素下方,能够将所有像素值同时读出,进 行数据的并行处理,使得最大拍摄帧率能够达到660fps。

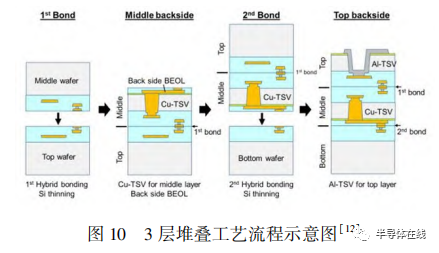

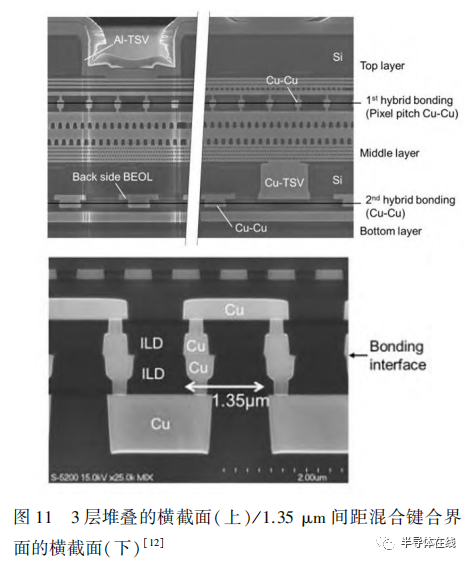

Tanida等人成功展示了采用全混合Cu-Cu直接键合工艺制造的三层堆叠背照式图像传感器(BSI),与只采用硅通孔(TSV)连接的三层堆叠背照 式图像传感器相比,混合键合连接能够实现更高性 能和更多功能。图10为其3层堆叠工艺流程示意 图。首先,利用混合键合将中间层键合到顶层。在 中间层Si减薄之后,制作Cu-TSV和背面BEOL,作 为中间层正面和背面之间的电学通路。再进行第二 次混合键合,利用Cu-Cu键合将中间层的背面与底 层连接。最后,减薄顶层Si并形成贯穿顶层Si的Al-TSV。研究团队还发现键合晶圆表面上的等离 子体活化条件是提高较小间距的Cu-Cu键合成品 率的关键因素,通过优化等离子体活化气体比例,成 功实现了间距为1.35 μm的混合键合,图11为键合 横截面的TEM图。

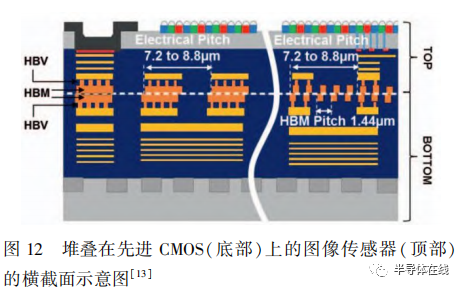

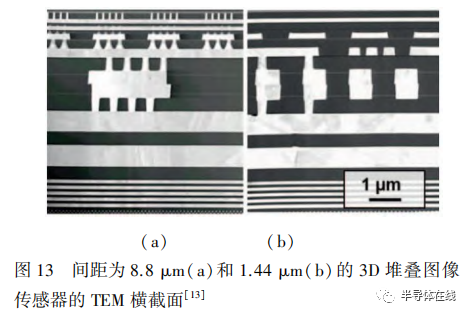

STMicroelectronics和CEA-LETI机构的研究人 员合作开发了用于3D堆叠CMOS图像传感器的200 mm和300 mm 晶圆级混合键合工艺。在200 mm晶圆级混合键合工艺中,研究人员通过优 化晶圆键合对准系统、偏移补偿程序、测量系统、优 对准键,以及使用反馈回路来提升晶圆对准精度。通过进一步优化工艺和设备,成功将晶圆级混合键 合扩展到300 mm晶圆上,并且键合通孔间距达 到6 μm,可完全符合BSI进行3D堆叠的要求。更 小键合通孔间距能够实现更高密度互连,但是较小 间距互连可能会危及电气和可靠性性能。研究团队 研究了键合通孔间距收缩对互连稳健性的影响,从工艺、器件性能和鲁棒性的角度出发,分别研究了8.8 μm到1. 44 μm键合间距,对3D堆叠背照式CMOS图像传感器性能的影响,如图12和图13所 示。

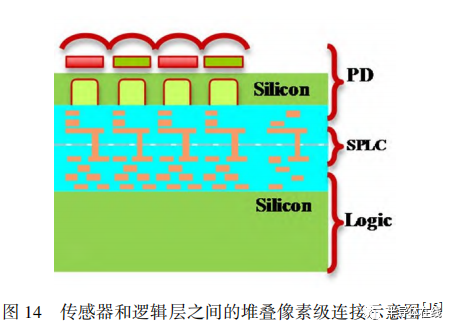

国内图像传感器厂商豪威科技也在进行堆 叠式图像传感器研究。图14是一款双通道转换增 益的堆叠式图像传感器示意图,其中像素单元的部 分器件被布置到逻辑层,以提高传感器填充系数,增 加功能。传感器晶圆和逻辑晶圆单独制造,并通过 间距为1.5 μm的混合键合通孔进行像素级连接,像 素级连接使得数据能够从传感器层上的像素阵列快 速传输到逻辑层上的器件阵列。

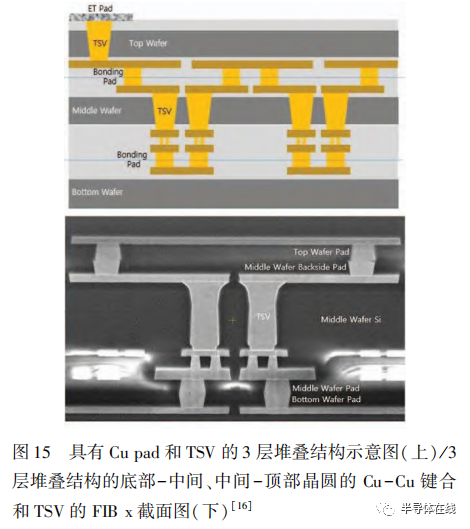

可以看到,目前采用混合键合工艺的主流产品 是堆叠式图像传感器,各大研究机构也在推动混合 键合技术不断完善,以使其成为一项通用的三维集 成技术,能够应用在其他领域及产品。三星Sam⁃sung通过将TSV工艺和混合键合工艺结合,推出X- Cube [16]工艺,应用于多枚芯片堆叠封装中。与采用 多个芯片平面封装的方式相比,X-Cube 3D封装使 整个芯片结构更加紧凑,能够进行更高效和简单的I/ O设计,并且由于更短的互连会带来更低的电阻。Samsung研究人员通过优化工艺参数,利用面对面(F2F)和背对面(B2F)两种方式,实现了多个晶圆 的堆叠集成。以图15中3片晶圆堆叠为例,每片晶 圆首先通过大马士革铜线后端工艺来制作混合键合 所需的铜通孔,为了构造用于混合键合的铜通孔,每 片晶圆应该至少包含两层金属层。中部和底部晶圆 采用面对面的方式键合在一起,紧接着对中部晶圆 的背部进行减薄,加工形成TSV以及用于与顶部晶 圆进行混合键合的铜通孔。顶部晶圆以背对面的方 式与中部/底部堆叠晶圆进行混合键合,对顶部晶圆 背部进行减薄并制作TSV用于进行电学测试。

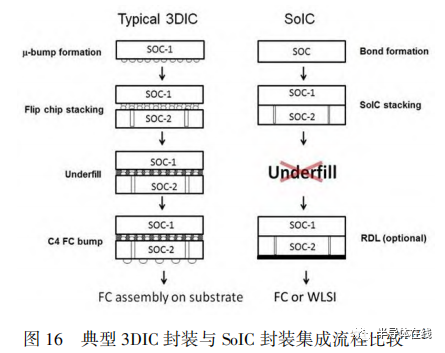

台积电TSMC发布名为SoIC的三维集成 工艺,是业界第一款逻辑-逻辑、存储器-逻辑的3D集成工艺。SoIC技术能够将不同工艺节点、材料、功能和尺寸的芯片进行堆叠,设计和集成更加灵活,使系统能够以更低的成本和更好的性能进行扩展。

如图16所示,SoIC不再使用凸点(bump)进行芯片 间的连接,转为表面更为平整的混合键合进行连接,因此 无 须 再 进 行 层 间 缝 隙 填 充。与 传 统 采 用μ-bump的3D集成方式相比,SoIC能够提供更高的I/ O键合密度,键合间距至少小4倍,键合密度至少 高16倍。并且实现了更低的功耗、更低的RC延 迟、IR压降和更低的热阻。

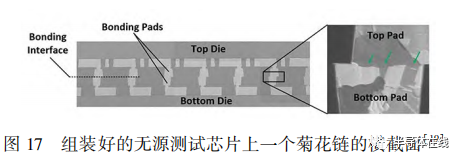

Intel公司也在基于混合键合工艺开发自 家的3D集成技术。Intel研究了混合键合工艺对顶 部金属层无源器件和功率传输的影响,提出最小化 影响的具体设计。并且通过优化相关工艺参数,来 满足混合键合要求。例如,在制作键合金属层时,避 免引起过度的晶片翘曲;在进行化学机械抛光时,实 现光滑平坦的表面电介质和凹陷受控的键合通孔;在键合时,保持极其干净的键合表面、高精度对准和 最大化测试覆盖率。图17是测试芯片上的一个键 合菊花链的横截面,显示出良好的对准精度和键合 界面,可以看到键合界面金属颗粒相互扩散,实现金 属到金属的键合。

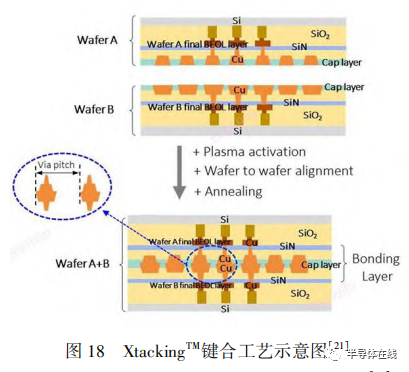

长江存储YMTC最先在3D NAND Flash制造中 引入混合键合工艺,并将其命名为Xtacking。3D NAND Flash由存储单元和外围电路组成,在传 统工艺中,外围电路和存储单元并排放置,共享有限 的芯片面积。但是随着3D NAND存储单元层数的 增加,外围电路占整个芯片尺寸的百分比将增加,外 围电路占据的面积难以忽视。Xtacking工艺通过存 储单元和外围电路分别制造在两片晶圆上,利用混 合键合工艺进行层间连接。分离开的存储单元和外 围电路可以独立设计生产,极大提升了工艺灵活性,并缩短了研究周期。图18是Xtacking键合工艺的 简要描述,两片晶圆在准备结束之后进行对准,退 火,形成数百万对具有小间距的金属通孔,完成电学 连接和物理支撑。研究团队从测试结构和产品两个 层面研究了Xtacking工艺键合界面的可靠性。在测 试结构级可靠性测试中,Xtacking键合层在超长时 间热或湿度应力后表现出非常稳定的金属电阻、介 电泄漏、键合强度和介电击穿电压。在产品级可靠 性测试中,封装的3D NAND产品表现出类似的优 异可靠性,充分证明了混合键合工艺的可行性。YMTC不断对Xtacking工艺进行改进,到目前为止,已推出Xtacking 2.0和Xtacking 3.0版本,并已有相 关产品面世。

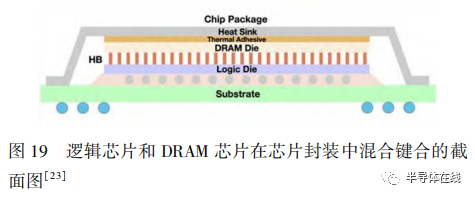

阿里巴巴达摩院提出针对于人工智能应用 的高密度和高能效的近内存计算解决方案,其中利 用混合键合工艺来连接逻辑芯片和DRAM芯片,如 图19所示。晶圆级混合键合技术能够实现高带宽 集成,实 验 数 据 表 明,其 能 效 比HBM或DDR SDRAM等片外存储器解决方案高出200倍,比最先 进的近内存计算解决方案高出至少2倍。DRAM芯 片和逻辑芯片分别基于25 nm和55 nm工艺制造,通过间距为3 μm的铜通孔连接在一起,铜通孔为 两者间的电学通道。

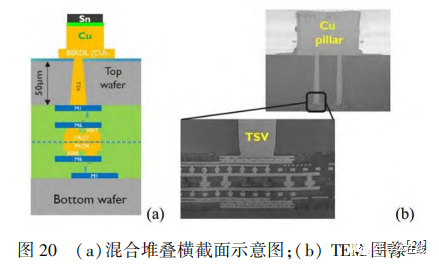

比利时微电子研究中心IMEC基于标准的65 nm工艺技术制造了键合通孔间距为2.5 μm的300 mm混合键合晶圆片,并且对键合晶圆的电学、热学、力学和可靠性性能进行评估,如图20所示。研究团队通过晶圆片上的回环结构来评估混合键合 通孔的电学性能,并证明了当测试样品在4点弯曲 设置中经受1000次机械循环时,混合键合界面的质 量不受影响。以及通过在测试芯片的一个单元中产 生热源,并利用集成温度传感器测量两个晶圆片的 热响应来评估堆叠晶圆的热性能,结果表明,温度传 感器和热源相对于外部热边界条件的位置在分析实 验结果时起着重要作用。

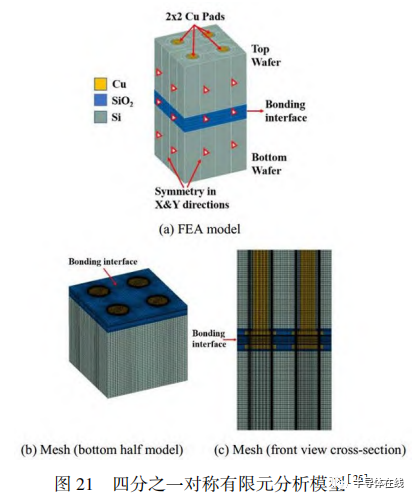

新加坡IME机构基于有限元分析方法对混合 键合机制进行了一系列仿真研究,图21为键 合面有限元分析模型。通过对晶圆级混合键合工艺 的多个流程进行三维建模,针对各种设计和工艺条件,例如晶圆片翘曲度、铜通孔凹陷值、退火温度和 退火时间、硅通孔( TSV)深度和铜通孔间距等,从 热-力-电的角度模拟混合键合技术的键合过程,详 细研究影响键合完整性的关键因素,并提供可能的 改进方法。对混合键合工艺进行数值研究可以为实 际设计和工艺提供指南和参考,有助于优化设计和 工艺参数,缩短工艺开发周期和降低研发成本。

海力士半导体SK Semiconductor 、格罗方德GlobalFoundries、富 士 通Fujitsu以 及 三 菱Mitsubishi也对混合键合工艺进行了深入研究。

3 结论

本文研究了一种用于5G通信的射频微系统与天线一体化三维扇出型集成封装技术. 通过在玻璃晶圆 上使用双面布线工艺,实现毫米波天线阵列的制作. 将TSV转接芯片与射频芯片倒装焊在玻璃晶圆上,再用树脂材料 进行注塑,将玻璃晶圆与异构芯片重构成玻璃与树脂永久键合的晶圆. 减薄树脂晶圆面漏出TSV转接芯片的铜柱,在 树脂表面上完成再布线. 把控制、电源管理等芯片倒装焊在再布线形成的焊盘处,植上BGA焊球形成最终封装体. 利 用毫米波探针台对射频传输线的损耗进行测量,结果表明,1 mm长的CPW传输线射频传输损耗在60 GHz仅为0.6 dB. 在玻璃晶圆上设计了一种缝隙耦合天线,天线在59.8 GHz的工作频率最大增益达到6 dB. 这为5G通信的射频微系统 与天线一体化三维扇出型集成提供了一个切实可行解决方案.

本文对晶圆级集成技术的两种主流工艺——— TSV工艺和混合键合工艺进行了系统性的介绍,综 合多个研究机构的最新技术成果,对其进行了进一 步详细说明。

混合键合由于其工艺较为简单,集成密度更高,能够同时实现电学连接和物理支撑,是接下来研究 和发展的重点。在将混合键合工艺应用于感存算一 体化芯片之前,仍有大量研究工作需要进行,包括优 化设计和工艺参数,提高晶圆对准精度,实现低温退 火以及降低成本等。面向感存算一体化芯片的晶圆级集成工艺的成功开发,将有力推动感存算一体化 技术的进步和实际应用,为我国先进半导体工艺技 术的自主自强做出贡献。

来源:功能材料与器件学报第 29 卷第 1 期

作者:赵国强1,2 ,赵 毅2,3(1.中国电子科技南湖研究院,;2. 浙江大学信息与电子工程学院;3. 华东师范大学集成电路科学与工程学院)

审核编辑:汤梓红

-

射频

+关注

关注

106文章

6174浏览量

174001 -

晶圆

+关注

关注

53文章

5476浏览量

132887 -

通信

+关注

关注

18文章

6486浏览量

140340 -

物联网

+关注

关注

2951文章

48242浏览量

419476 -

5G

+关注

关注

1368文章

49246浏览量

643318

原文标题:【半导光电】晶圆级集成技术研究进展

文章出处:【微信号:今日光电,微信公众号:今日光电】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)

新型铜互连方法—电化学机械抛光技术研究进展

薄膜锂电池的研究进展

传感器EMC的重要性与研究进展

太赫兹量子级联激光器等THz源的工作原理及其研究进展

废旧镍氢电池回收处理技术研究进展

量子计算关键技术研究进展

晶圆级集成技术研究进展

晶圆级集成技术研究进展

评论