从一堆沙子,到一个精密的芯片,这中间究竟经历了什么环节,各个环节又需要什么样的技术呢?跟着小编一起来学习一下!

1.从砂子到硅片

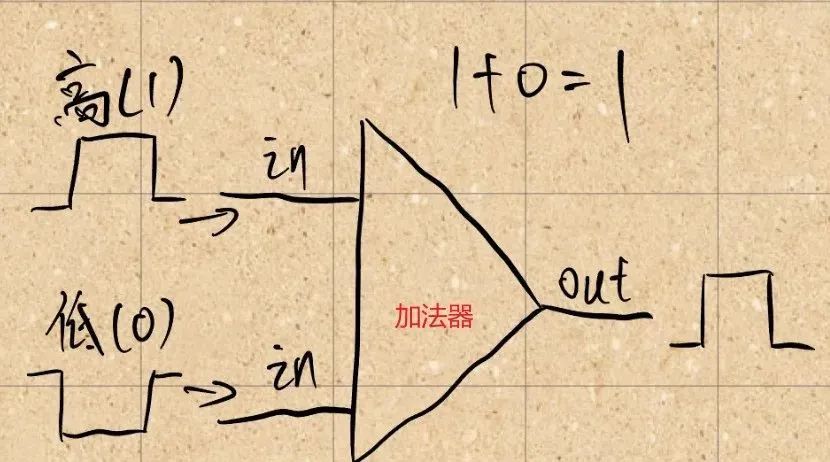

所谓“半导体”,是一种导电性能介于“导体”和“绝缘体”之间的物质总称。导体能导电,比如铁铜银等金属,绝缘体不导电,比如橡胶。芯片的制作为什么要用半导体?因为半导体的导电与所加电场方向有关,即它的导电是可以有方向性的。比如,给半导体两端加上正电压,它可能就导电;反之,将它两端所加的电压极性反过来,就不导电。而这种性能,可以做成“电子开关”。我们都听说过“计算机做的都是二进制的0-1运算”,这种运算体现在物理层面就是指“高低电位的变化”,高电位代表1,低电位代表0。高低电位在复杂的电路设计下面可以实现复杂的转化,这样表现出来就好像是计算机在做01运算。半导体的这种电学特性可以设计成电子开关,可以很好实现高低电位的转化。

在自然界中,获取成本最低的半导体就是硅。而硅料的提取是熔炼砂子。提到这里可能有朋友想到“光伏电池片用的也是硅片”。没错,生产芯片和生产光伏电池片在硅片制作环节是非常相似的,都是需要先熔炼取硅,然后做切割、研磨等工艺。因此,你可能会看到一些光伏产业链的股票也伴有半导体概念,比如高测股份。

芯片用硅和光伏用硅最大的区别就在于纯度不同。在纯度方面,光伏用单晶硅片的纯度要求硅含量为4N-6N之间(99.99%-99.9999%),但是半导体用单晶硅片在9N(99.9999999%)-11N(99.999999999%)左右,纯度要求最低是光伏单晶硅片的1000 倍。在外观方面,半导体用硅片在表面的平整度,光滑度和洁净程度要比光伏用硅片的要求高。

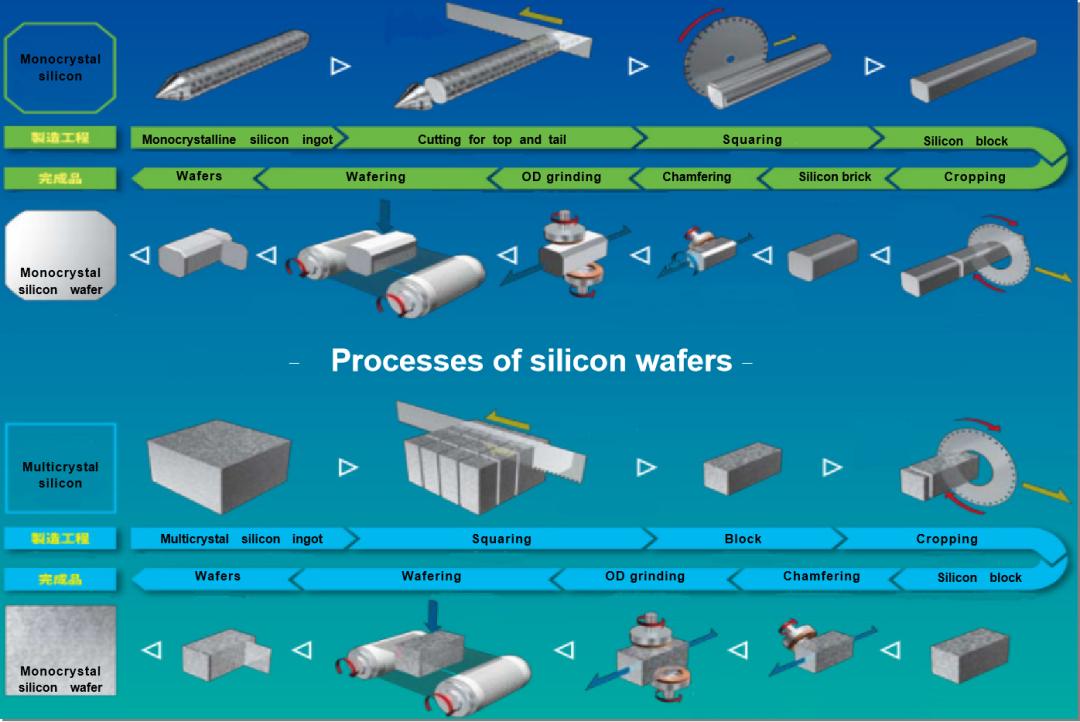

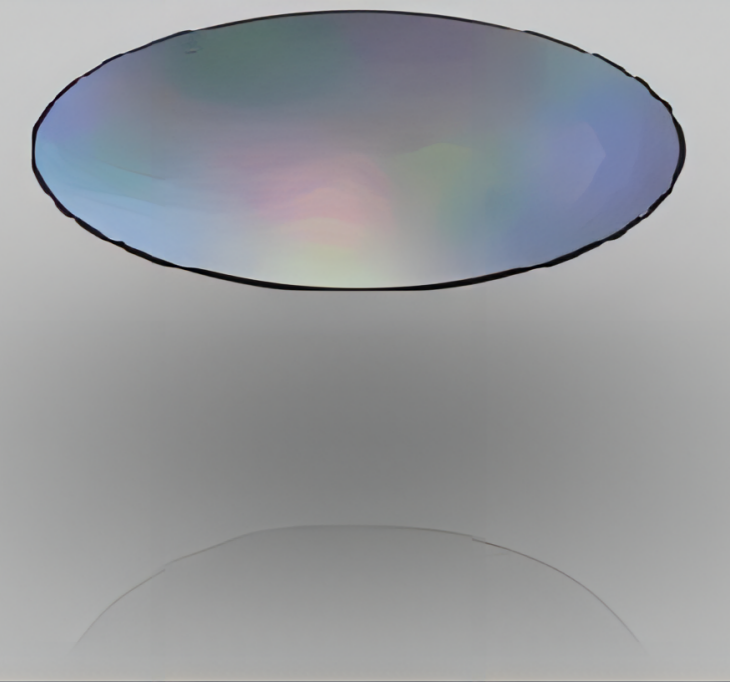

总结来说,砂子到硅片需要经过熔炼、切片、研磨、蚀刻、抛光等过程,最终形成一片片的晶圆(所谓晶圆,就是圆形的高纯度硅片)。

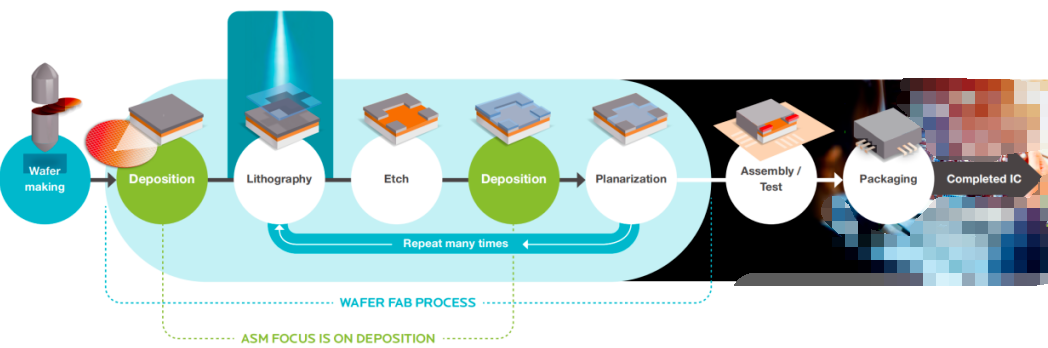

好了,此时你得到了一片片处理好的高纯度硅片,接下来我们就需要我们需要在晶圆上雕刻电路,形成能用的芯片。在下面的工艺流程中,大致可以分为前端工艺、后端工艺和测封。

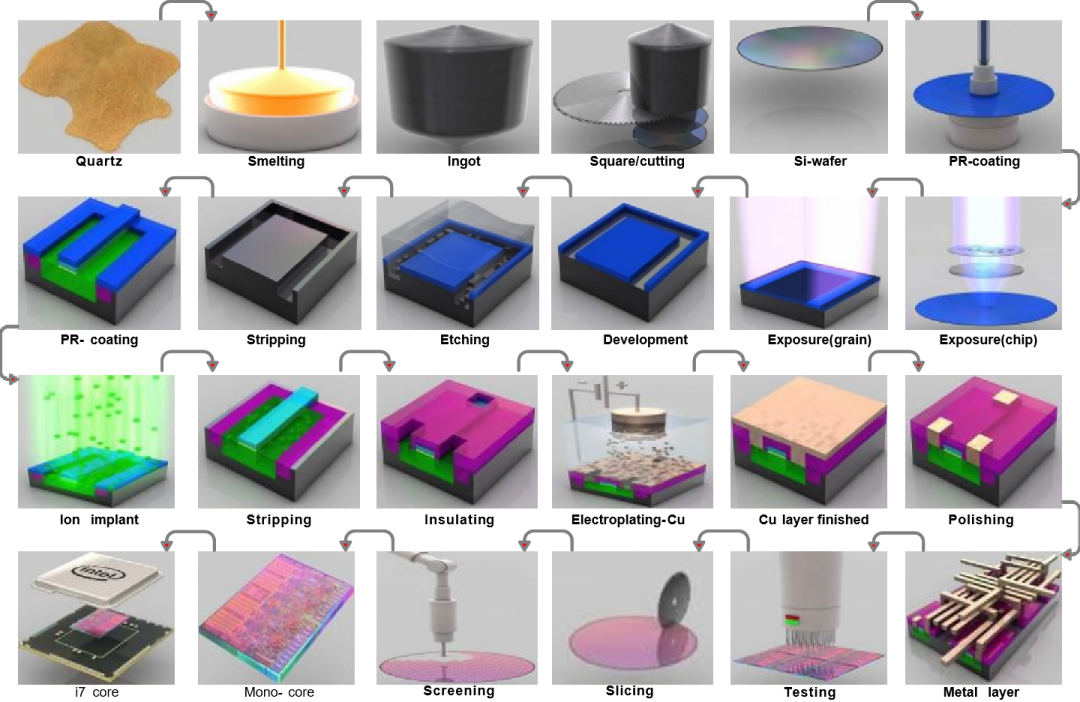

制造第一阶段:提炼硅锭

沙子:硅是地壳内第二丰富的元素,而脱氧后的沙子(尤其是石英)最多包含25%的硅元素,以二氧化硅(SiO2)的形式存在,这也是半导体制造产业的基础。

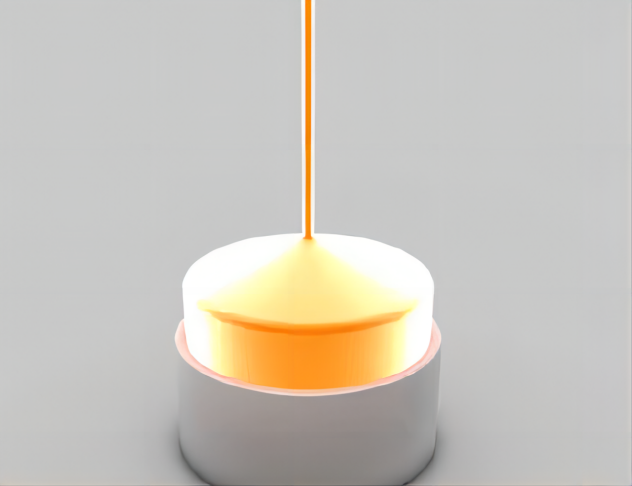

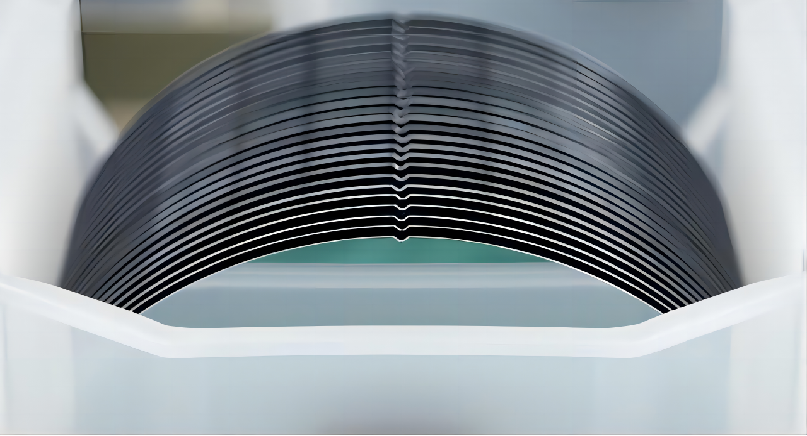

硅熔炼:12英寸/300毫米晶圆级,下同。通过多步净化得到可用于半导体制造质量的硅,学名电子级硅(EGS),平均每一百万个硅原子中最多只有一个杂质原子。此图展示了是如何通过硅净化熔炼得到大晶体的,最后得到的就是硅锭(Ingot)。

100千克,硅纯度99.9999%。

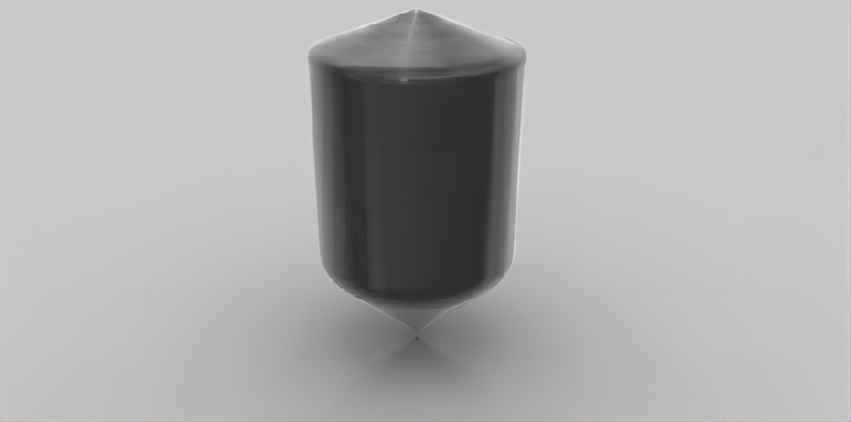

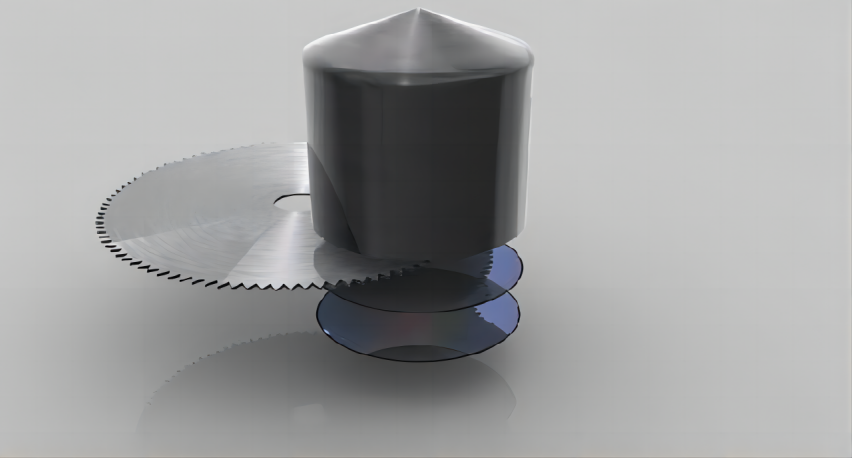

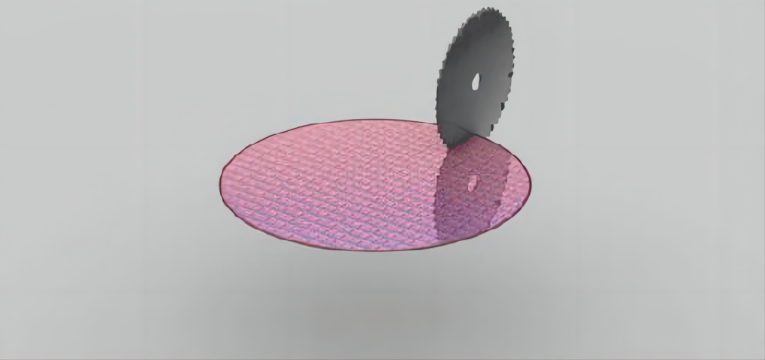

制造第二阶段:硅锭切割

硅锭切割:横向切割成圆形的单个硅片,也就是我们常说的晶圆(Wafer)。

45nm HKMG(高K金属栅极)。

制造第三阶段:光刻

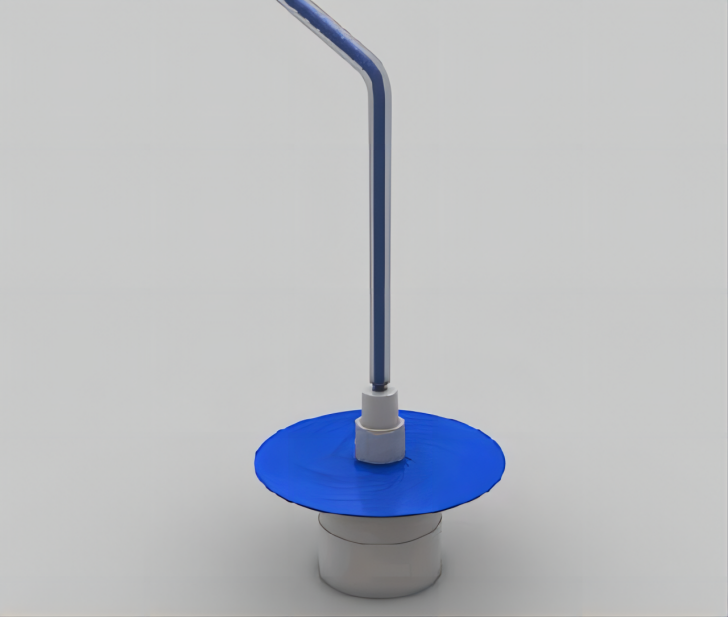

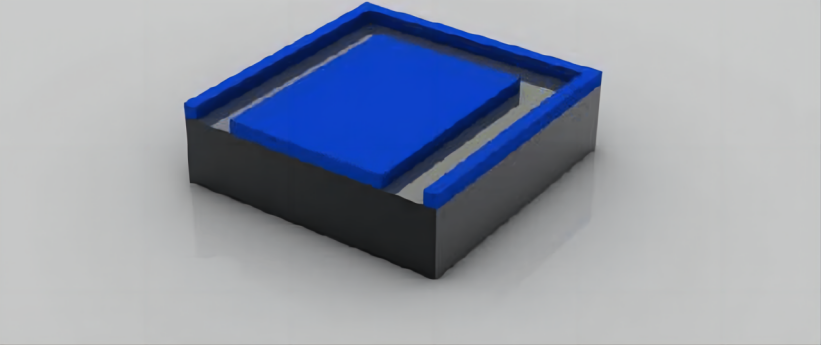

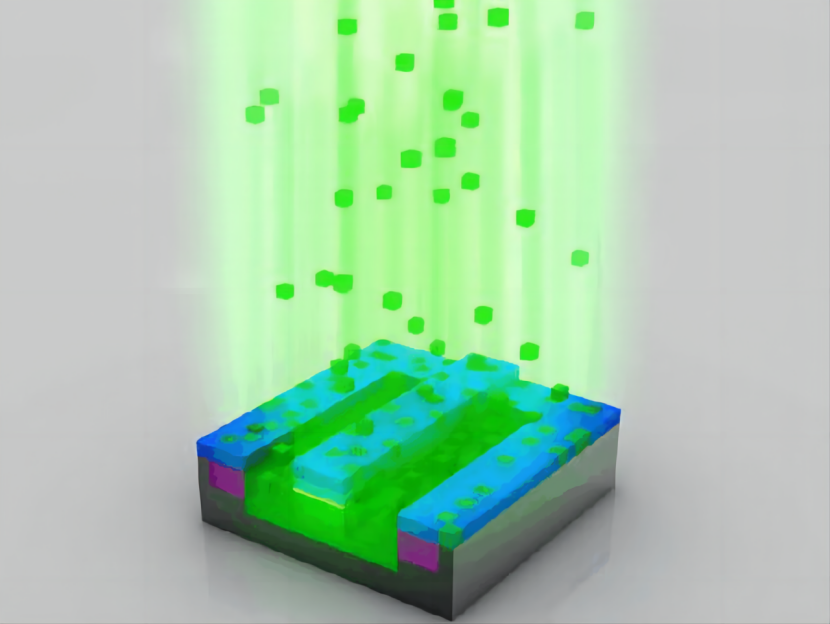

光刻胶(Photo Resist):图中蓝色部分就是在晶圆旋转过程中浇上去的光刻胶液体,类似制作传统胶片的那种。晶圆旋转可以让光刻胶铺的非常薄、非常平。

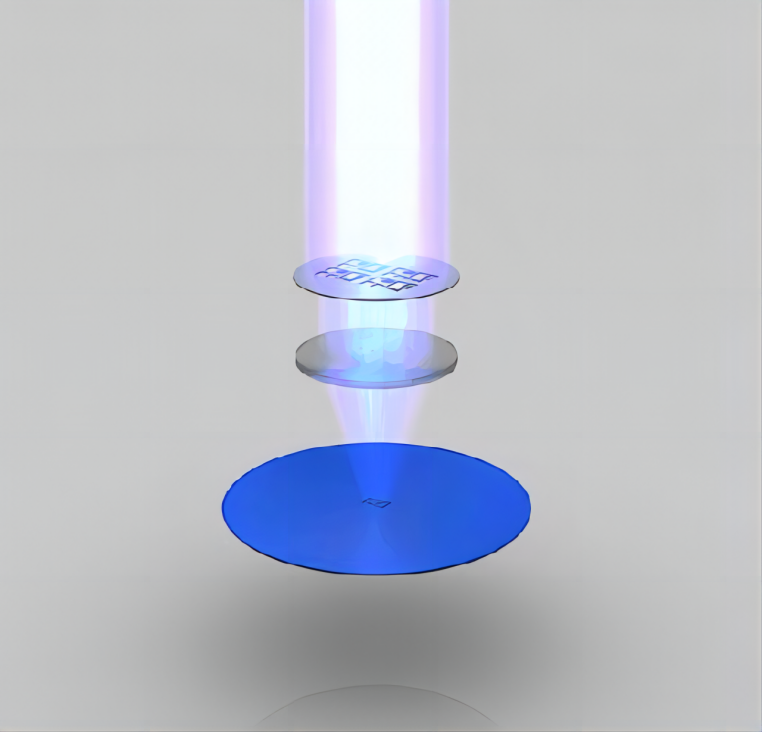

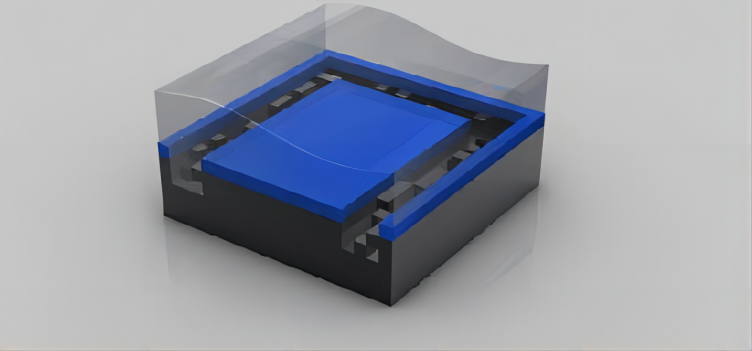

光刻:光刻胶层随后透过掩模(Mask)被曝光在紫外线(UV)之下,变得可溶,期间发生的化学反应类似按下机械相机快门那一刻胶片的变化。掩模上印着预先设计好的电路图案,紫外线透过它照在光刻胶层上,就会形成微处理器的每一层电路图案。一般来说,在晶圆上得到的电路图案是掩模上图案的四分之一。

光刻:由此进入50-200纳米尺寸的晶体管级别。一块晶圆上可以切割出数百个处理器,不过从这里开始把视野缩小到其中一个上,展示如何制作晶体管等部件。晶体管相当于开关,控制着电流的方向。现在的晶体管已经如此之小,一个针头上就能放下大约3000万个。

制造第四阶段:光刻胶的使命

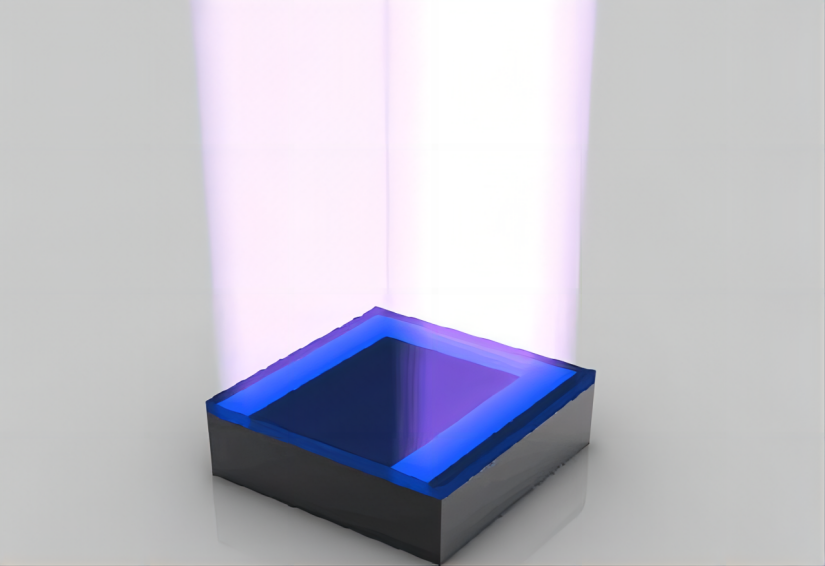

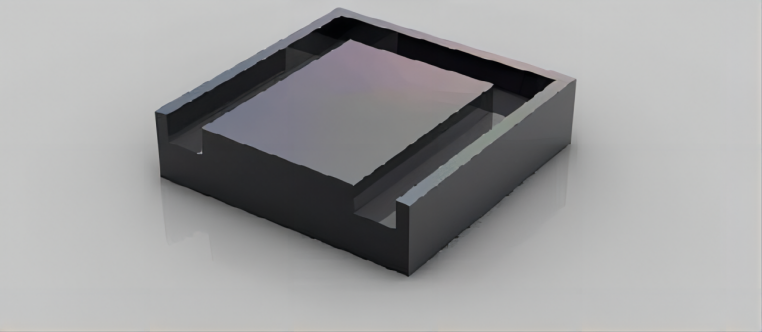

溶解光刻胶:光刻过程中曝光在紫外线下的光刻胶被溶解掉,清除后留下的图案和掩模上的一致。

蚀刻:使用化学物质溶解掉暴露出来的晶圆部分,而剩下的光刻胶保护着不应该蚀刻的部分。

清除光刻胶:蚀刻完成后,光刻胶的使命宣告完成,全部清除后就可以看到设计好的电路图案。

制造第五阶段:离子注入

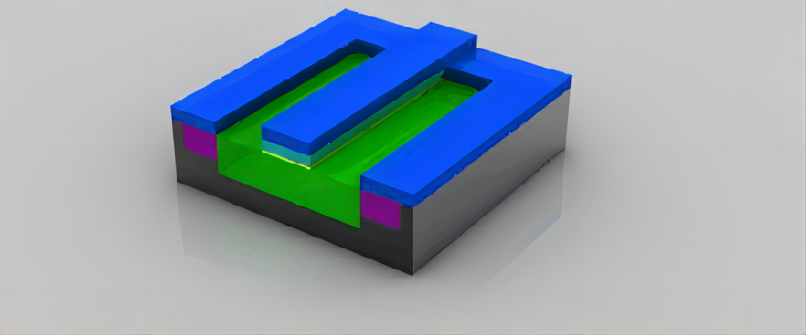

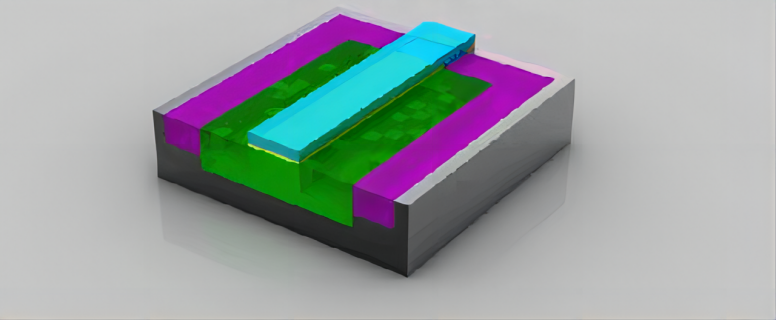

光刻胶:再次浇上光刻胶(蓝色部分),然后光刻,并洗掉曝光的部分,剩下的光刻胶还是用来保护不会离子注入的那部分材料。

离子注入(Ion Implantation):在真空系统中,用经过加速的、要掺杂的原子的离子照射(注入)固体材料,从而在被注入的区域形成特殊的注入层,并改变这些区域的硅的导电性。经过电场加速后,注入的离子流的速度可以超过30万千米每小时。

清除光刻胶:离子注入完成后,光刻胶也被清除,而注入区域(绿色部分)也已掺杂,注入了不同的原子。注意这时候的绿色和之前已经有所不同。

制造第六阶段:电镀晶圆

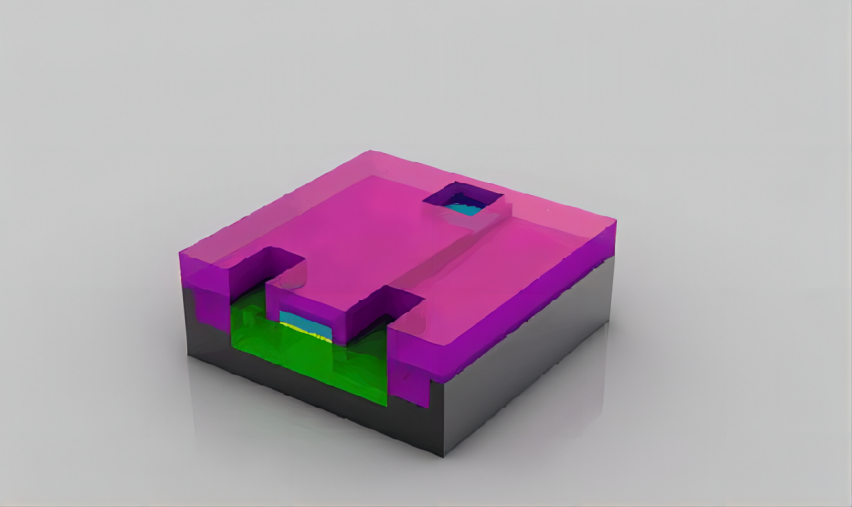

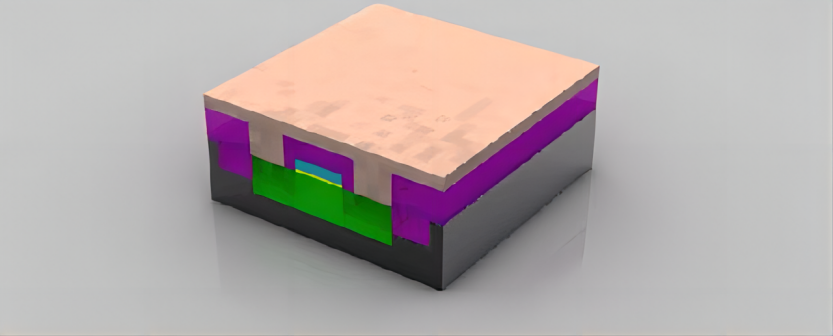

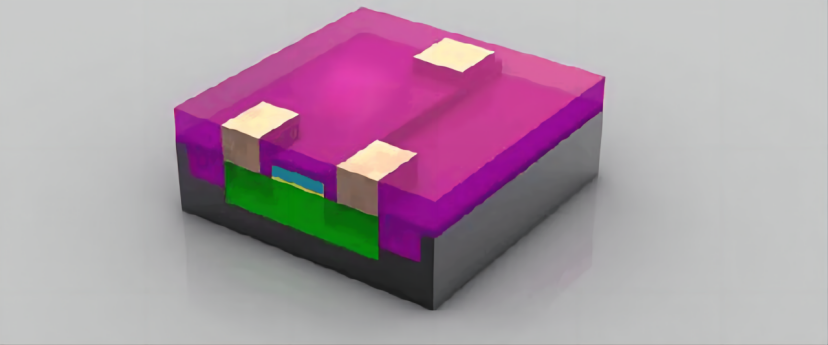

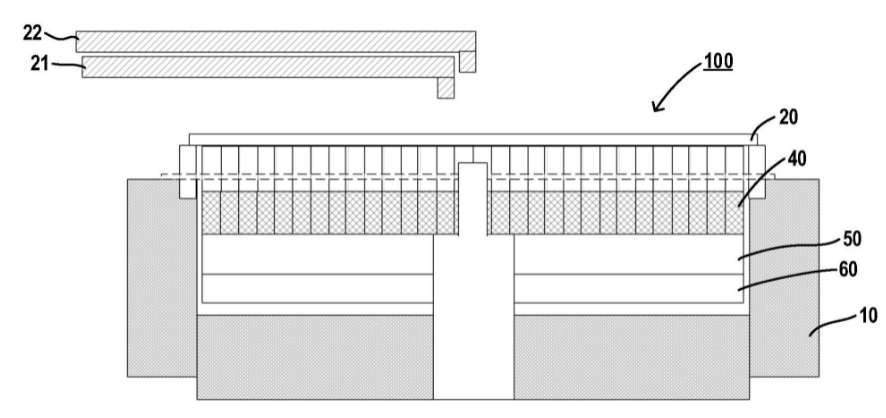

晶体管就绪:至此,晶体管已经基本完成。在绝缘材(品红色)上蚀刻出三个孔洞,并填充铜,以便和其它晶体管互连。

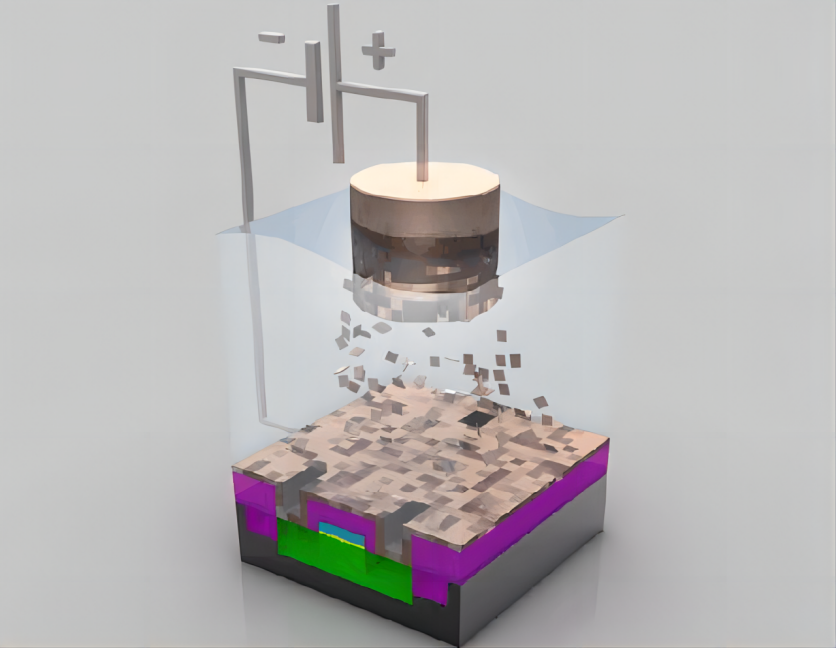

电镀:在晶圆上电镀一层硫酸铜,将铜离子沉淀到晶体管上。铜离子会从正极(阳极)走向负极(阴极)。

铜层:电镀完成后,铜离子沉积在晶圆表面,形成一个薄薄的铜层。

抛光:将多余的铜抛光掉,也就是磨光晶圆表面。

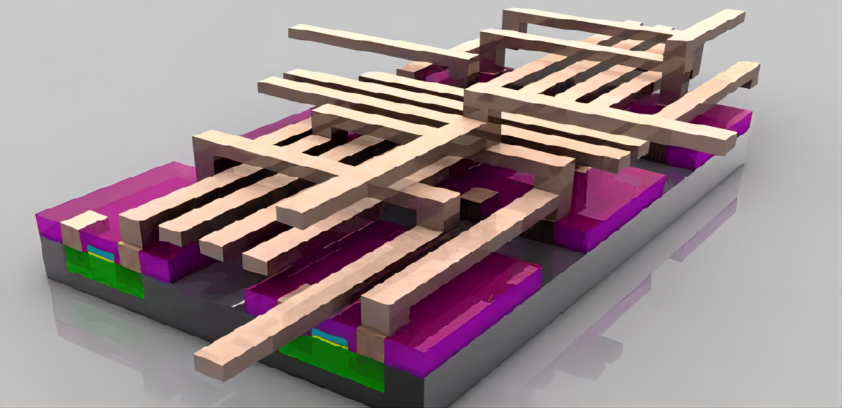

金属层:晶体管级别,六个晶体管的组合,大约500纳米。在不同晶体管之间形成复合互连金属层,具体布局取决于相应处理器所需要的不同功能性。芯片表面看起来异常平滑,但事实上可能包含20多层复杂的电路,放大之后可以看到极其复杂的电路网络,形如未来派的多层高速公路系统。

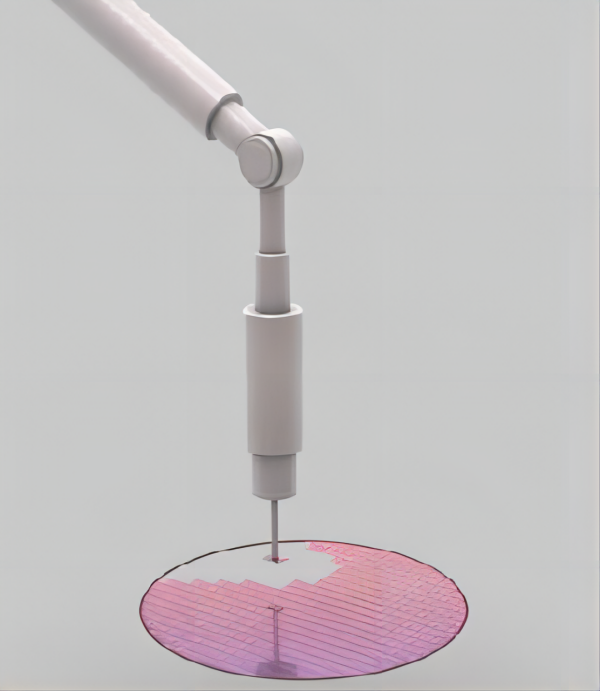

制造第七阶段:晶圆测试

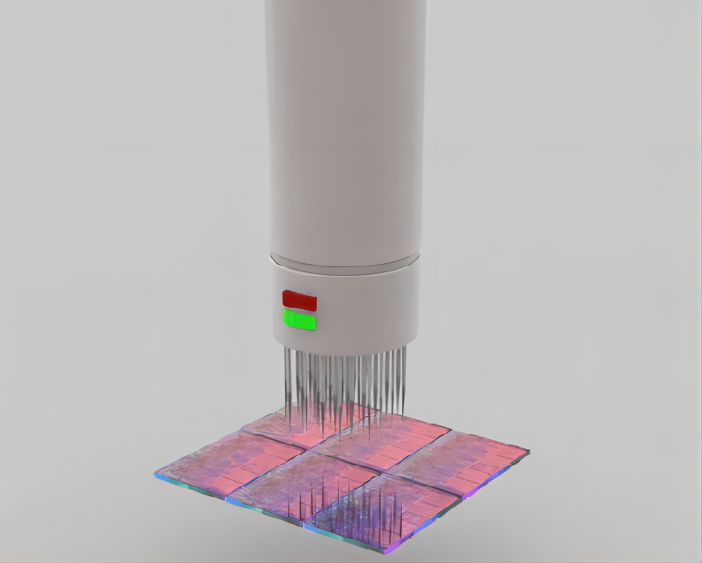

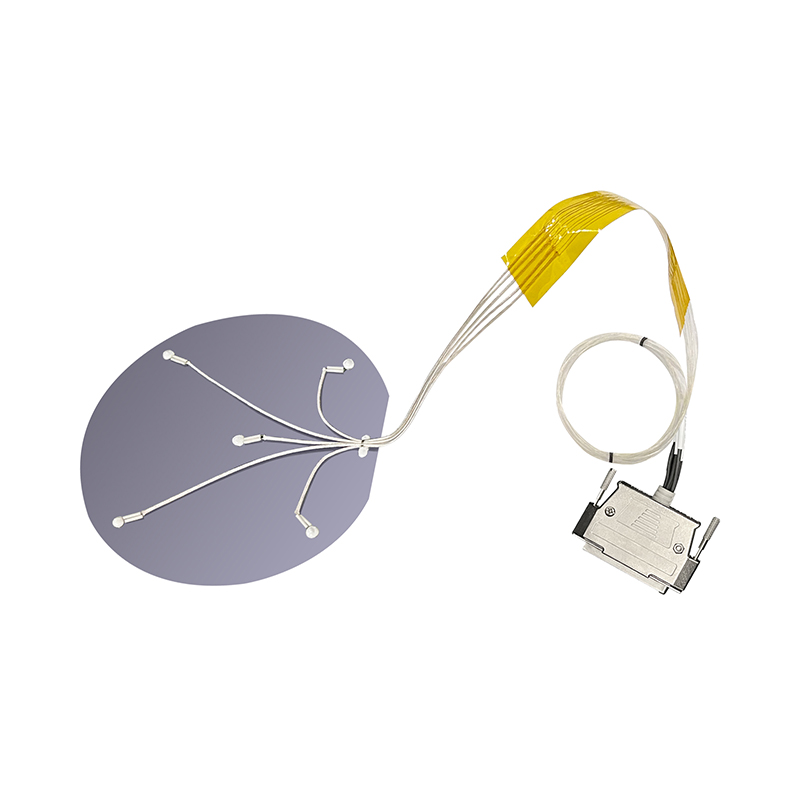

晶圆测试:内核级别,大约10毫米/0.5英寸。图中是晶圆的局部,正在接受第一次功能性测试,使用参考电路图案和每一块芯片进行对比。

晶圆切片(Slicing):晶圆级别,300毫米/12英寸。将晶圆切割成块,每一块就是一个芯片的内核(Die)。

制造第八阶段:晶圆检测

丢弃瑕疵内核:晶圆级别。测试过程中发现的有瑕疵的内核被抛弃,留下完好的。

审核编辑 :李倩

-

晶圆

+关注

关注

52文章

4895浏览量

127939 -

半导体制造

+关注

关注

8文章

399浏览量

24067 -

Wafer

+关注

关注

0文章

19浏览量

5767

原文标题:干货丨Wafer晶圆半导体制造流程图解

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

长期收购蓝膜片.蓝膜晶圆.光刻片.silicon pattern wafer. 蓝膜片.白膜片.晶圆.ink die.downgrade wafer.

半导体制程

晶圆制造工艺的流程是什么样的?

半导体制造的难点汇总

半导体制造工艺流程及其需要的设备和材料

ALD是什么?半导体制造的基本流程

智测电子 ——晶圆测温系统,tc wafer半导体晶圆测温热电偶

RFID读写头JY-V640在半导体wafer晶圆盒的使用流程

半导体制造三要素:晶圆、晶粒、芯片的传奇故事

Wafer晶圆半导体制造流程图解

Wafer晶圆半导体制造流程图解

评论