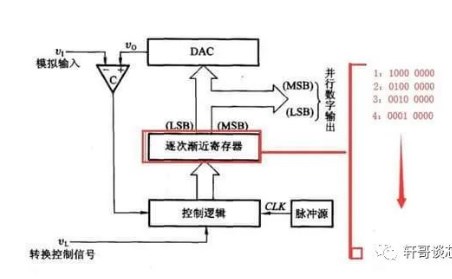

STM32中的ADC是逐次逼近型ADC(Successive Approximation ADC),是逐个产生比较电压Vref,并逐次与输入电压分别比较,以逐渐逼近的方式进行A/D转换的。而其中的用来产生Vref的电路就是DAC电路。因此一般DAC电路比较容易设计,而DAC在采样速度和精度的权衡上会比较复杂。

SAR ADC的转换原理是把输入的模拟信号按规定的时间间隔采样(采样),并与一系列标准的数字信号相比较,数字信号逐次收敛,直至两种信号相等为止(量化完成),最后输出代表此信号的二进制数(编码)。

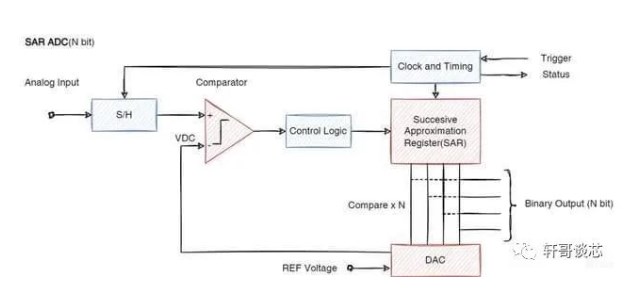

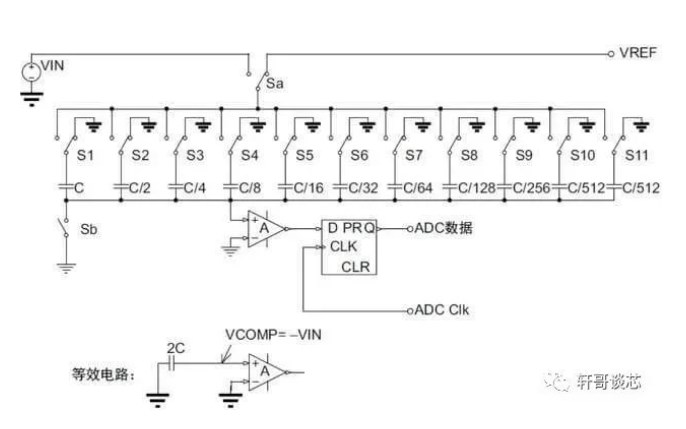

SAR ADC结构

结构上主要包括采样保持电路(S/H),比较器(COMPARATOR,COMP),SAR逻辑控制电路、时钟(CLOCK)和时序(TIMING)控制电路及DAC电路。

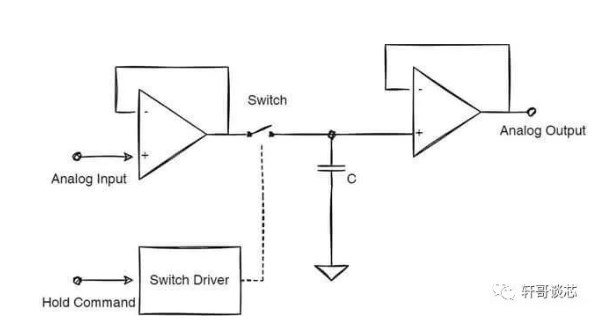

S/H电路

为了达到快速的采样,被采样的脉冲宽度一般是很短的,在下一个采样脉冲到来之前,要暂时保持所采得的样值脉冲幅度,以便进行后续转换。所以,在采样电路之后和比较电路之间要加保持电路。它的原理是通过一个开关连接一个电容,通过给电容进行充电来保持模拟信号的幅值信息。

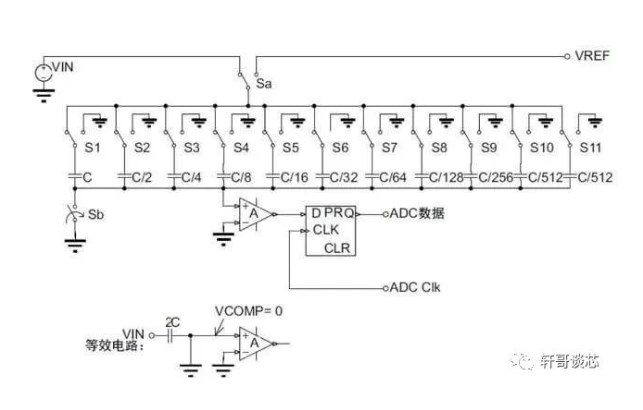

DAC电路

大多SAR ADC的DAC都使用电容式DAC来提供内在的跟踪/保持功能。电容式DAC是采用电荷再分配原理来产生模拟输出电压的。电容式DAC由N个具有二进制权重值的电容器阵列再加上一个“虚拟LSB”电容器组成。

首先通过Sa开关连接VIN,并将所有S1-S11的开关连接到VIN,给所有并联的电容进行充电,这样就将所有电容充满,并且充电电压为VIN。

然后通过将Sa开关连接到Vref,并且通过数字信号对应到S1-S11的开关上,也就是关闭一些电容的开关连接到GND上,断开电容,对地放电。

此时对于Vref上的电压就会根据断开电容的容量使得输出电压降低,从而将数字信号转换成一个模拟信号。

电容器阵列容量总量要等于2C。

转换步骤

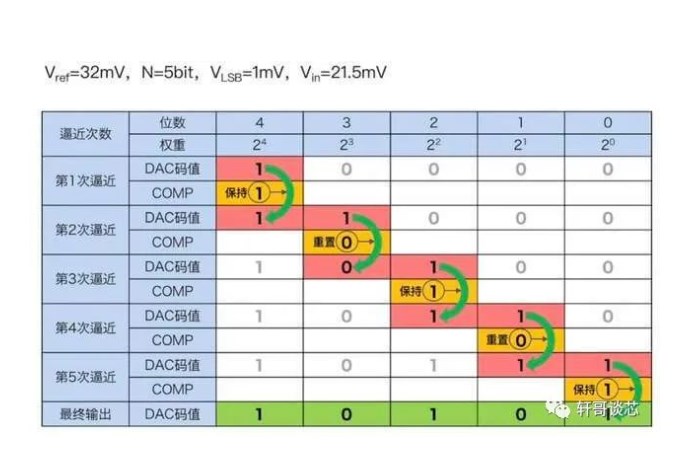

转换步骤数等于 ADC的分辨率,比如12bits ADC就有12个转换步骤,每个 ADC 时钟产生一个数据位。

采样状态

该状态下,电容充电至电压VIN。Sa切换至VIN,采样期间Sb开关闭合。

保持状态

该状态下,输入断开,电容保持输入电压。Sb开关打开,然后S1-S11切换至接地,且Sa切换至VREF。

转换(量化和编码)状态

该状态下,每个 ADCCLK 执行一个步骤,每一步完成后 ADC 输出一位数。采用二分法进行逐次逼近到 ADC 的精度(位数)。整个转换过程如下图所示。

-

电容器

+关注

关注

64文章

6348浏览量

100691 -

比较器

+关注

关注

14文章

1670浏览量

107721 -

STM32

+关注

关注

2276文章

10949浏览量

359187 -

充电电压

+关注

关注

0文章

28浏览量

6875 -

adc信号

+关注

关注

0文章

5浏览量

2262

发布评论请先 登录

相关推荐

蓝牙中的拓扑结构有散射网,MESH网是同一回事吗?

MOV中的8位图立即数是怎么一回事

MOV中的8位图立即数是怎么一回事呢?

请问芯片中ISP Flash和LDROM是不是一回事?

PCB设计中自动布线和手动布线是怎么一回事?资料下载

STM32中的SAR ADC是怎么一回事?

STM32中的SAR ADC是怎么一回事?

评论