CDM(Charge Device Model),与MM与HBM一起作为ESD的三种类型之一。随着IC工艺进程的发展与自动化生产流程的普及,CDM已经取代MM与HBM成为芯片失效的主要静电类型,目前CDM造成的失效占比远高于HBM与MM。而现阶段的流程管理与高自动化生产流程,能大幅度降低HBM与MM的发生概率,但是却无法降低CDM的发生概率。随着目前工艺结点的降低,CDM所造成的损害也日益严重。因为CDM的自发特性,CDM防护已经成为芯片设计中不得不考虑的指标。除此之外随着芯片在工业,车规,医疗等领域的大规模推广,CDM防护能力业已成为很多领域的硬性指标。目前CDM的防护也是业界所聚焦的设计难点。

一.CDM机理

笔者一直比较赞同陈东旸博士的观点:ESD作为一种普遍的自然现象,其背后是复杂的物理作用,需要从更深层次的角度去理解ESD的机理。而CDM作为一种自发性的放电行为,其背后机理也是需要从更微观的角度进行探讨。

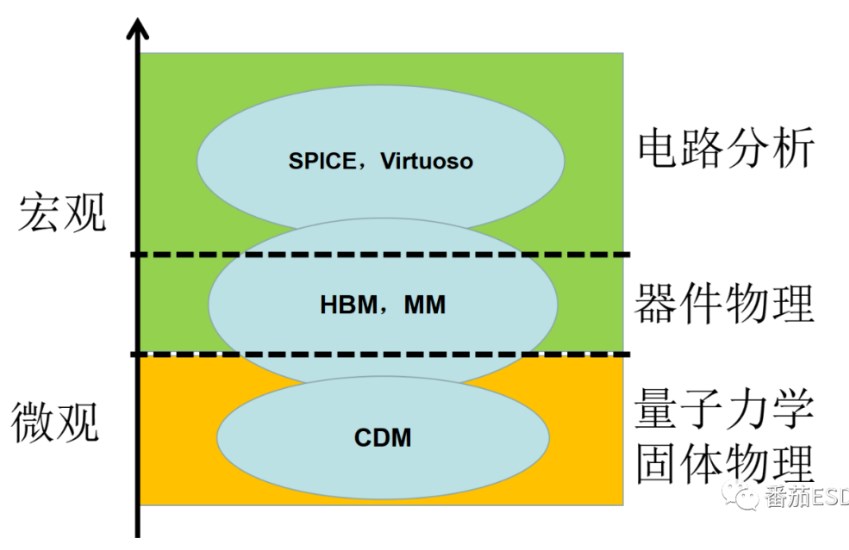

图一.HBM,MM,CDM三种ESD的关系。

目前主流的SPICE等电路仿真软件都是基于电路原理进行仿真建模,最多将拟合后二级效应代入修正。而HBM与MM等ESD事件需要对电场分布,能量分布等参数进行建模分析,传统电路仿真软件已经无能为力,此时需要Sentaurus和Silvaco等TCAD软件进行仿真建模。一方面为了仿真收敛会大幅度简化模型复杂度,另一方面,核心参数fab会模糊处理,从而造成仿真结果较为粗糙。而CDM的建模更加困难,因为CDM的自发特性,其聚焦于材料内部载流子的变化,所以针对CDM的建模仿真已经进入极其复杂的微观领域。

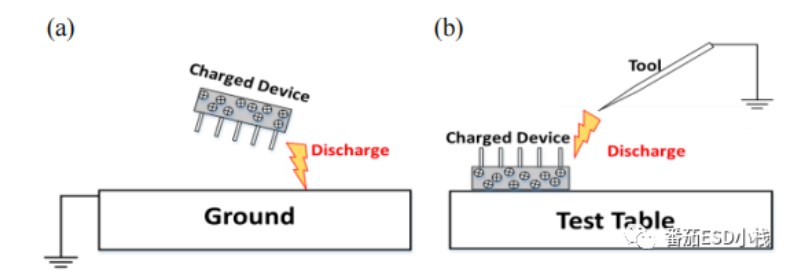

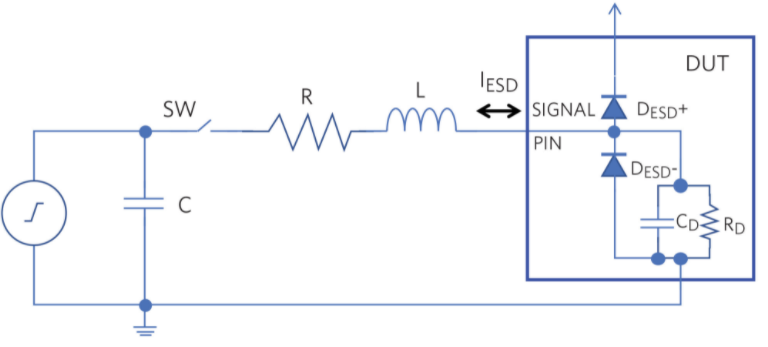

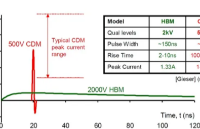

CDM是指芯片/裸片因为外电场,摩擦生电等因素其自身内部积聚了大量电荷,当与接地导体接触后(这里的接地是相对概率,只要电势相对够低便可认为是接地,比如接地电位或者金属机壳,工具等),大量电荷从体系逸出,此时会在极短的时间内产生静电脉冲,这个脉冲就是CDM放电。CDM的放电特点就是时间短,电流脉冲高,波形不确定。

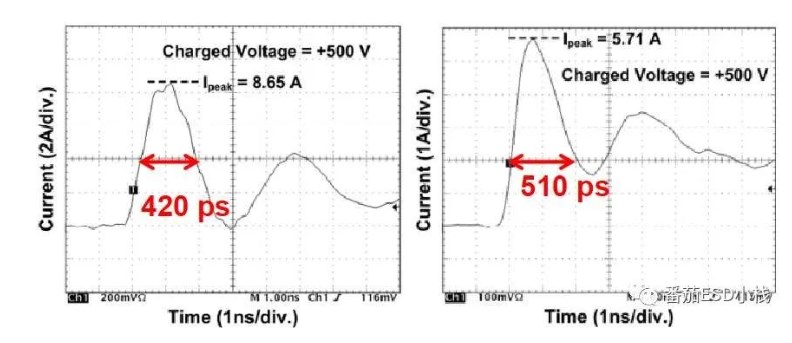

图二.不同芯片的CDM波形图。

从图中可以看出,CDM的脉冲持续时间很短,电流峰值很大。而且不同的芯片/裸片因为结构,电容等参数的差异,相同条件下不同芯片的CDM波形也会有较大差异。由原理得知CDM的特点:

自发性。CDM放电是器件在外界因素的扰动下本身储存了大量带电载流子,而芯片/裸片本身的结构和电容决定了储存在器件电荷的电量和放电持续时间,所以CDM波形是由芯片自身决定,其不像HBM和MM一样有固定的波形。

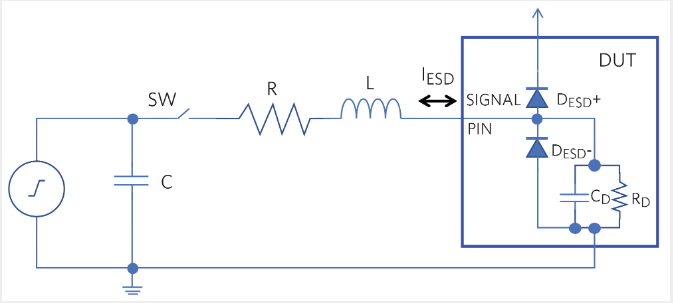

由内到外。HBM和MM都是由外而内的ESD事件,静电流是由芯片外部灌入内部,所以针对HBM和MM的防护主要集中在IO。而CDM反之,CDM是器件内部向外部放电,所以针对CDM的防护相较于其他类型的ESD防护设计难度更高。因为脉冲时间短,所以CDM防护的重点是建立低寄生电容的泄放通道,CDM幅值虽然很高,但是其防护电路不需要很大的面积,只需要能及时将积聚在半导体衬底材料内的载流子泄放出去。

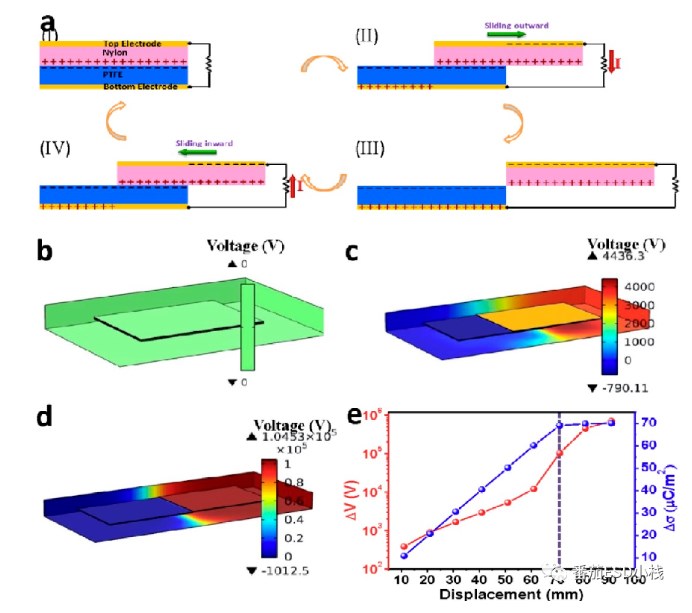

CDM主要诱因之一是外部电场作用,整个芯片或者裸片都处在外界电场作用下,此时半导体内部载流子在外界电场下会重新分布,为了维持电中性条件,半导体内部会产生自发极化电场。在极化电场与外电场的相互作用下,整个体系还维持电中性平衡,此时如果相对接地的金属与芯片或者裸片接触,大量载流子流入/出导体,形成自发的CDM放电。

图三.CDM原理示意图。

从微观上说,无论是否存在外电场诱发,半导体材料自身时刻处在一个动态平衡的过程中。无时无刻都有电子逸出和复合。摩擦生电与受热不均也会破坏体系的电中性条件,形成静电。其中当芯片/裸片之间相互碰撞或者接触,在接触面会产生异质结或者金半接触,载流子会重新分布,从而形成极化电场,此时载流子分布产生梯度,如果与电位较低的导体接触,大量的载流子从芯片内部转移,从而造成CDM静电。而温度分布的不均,也会造成CDM静电,不同温度会造成费米能级不同,从而造成极化电场。

图四.摩擦生电示意图。

简而言之便是因为各种外部环境的变化,改变了半导体材料的电中性条件,使得载流子分布不均,空穴与电子各自积聚在不同区域,通过内建电场维持体系平衡。当与相对接地的金属接触后,这部分聚集的载流子逸出体系,造成CDM放电。因此CDM在生产制造、封装、测试、运输过程中是极难被避免的。而随着工艺结点的降低,芯片对CDM的耐受程度也随之降低,CDM的失效基本都集中在栅氧化层。

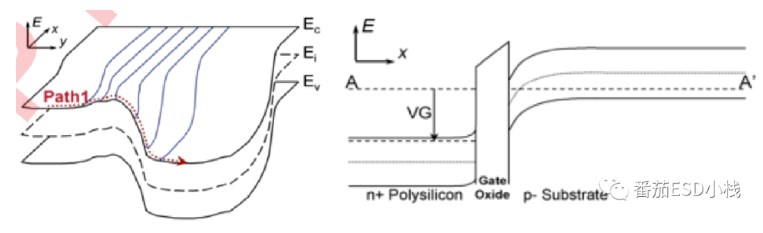

图五.MOS管中电荷积聚的能带示意图。

由图中可以看出,载流子的积聚会改变半导体材料的费米能级分布(电子越多,费米能级越低,空穴越多,费米能级越高。)而当接地的金属一旦与栅极接触,金属功函数与费米能级的电势差会产生极化电场,如果该电场过强,就会造成栅氧化层的损坏。所以CDM的失效主要集中在栅极,CDM造成的栅极失效位置也受很多因素影响。(下期会专门讲解)

二.CDM的差异

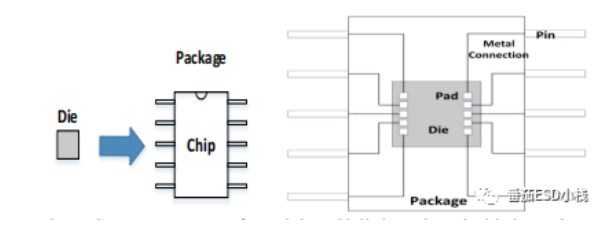

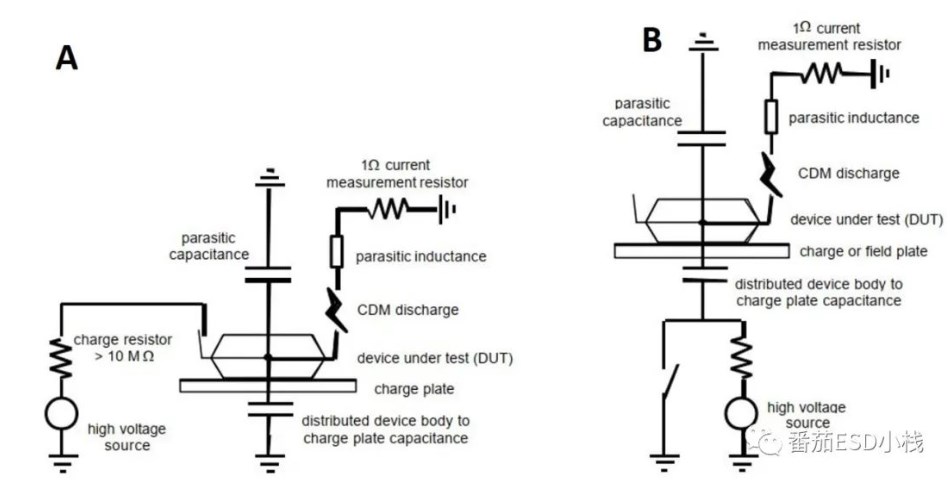

目前CDM测试有两种:一种是封装后的Chip-Level,另一种是未进行封装的Silicon-Die。

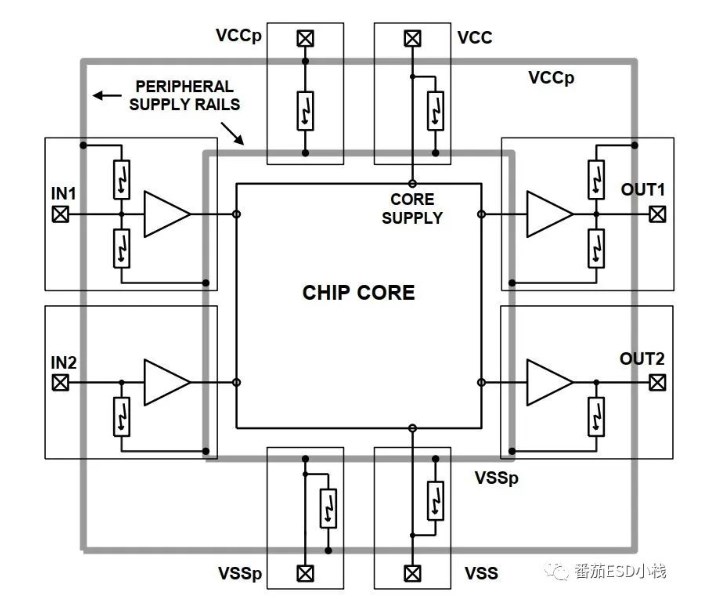

图六.芯片封装示意图。

封装后芯片与未封装的裸片其CDM机理存在一定差异。封装后的芯片因为框架与金属互连的存在,摩擦生电或者外界电场产生的电荷会被存储在框架中。而未封装的裸片,这部分电荷会被存储在衬底半导体材料中。如图所示,当接地金属与封装后的芯片接触,大量电荷或者直接通过金属互连从体系转移出去,或者通过内部芯片的PAD进行泄放。

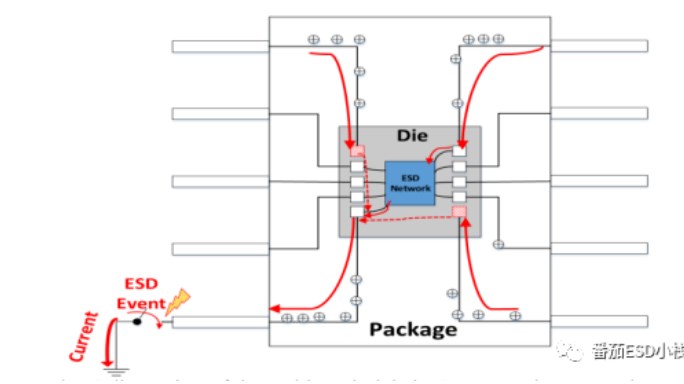

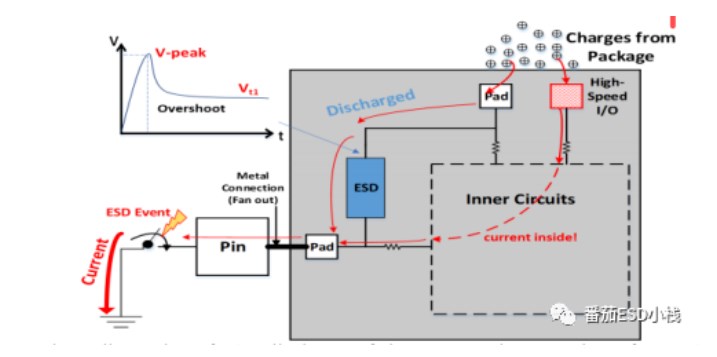

图七.封装芯片CDM示意图。

而存储在框架内的电荷也不一定会老老实实呆在一个地方,其也有可能通过金属互连在无接地金属触发的情况下在芯片内部乱窜。如图所示,针对由封装流入内部的电荷,可以看成是一种“由外到内”的ESD事件,这种由外到内的ESD电流便类似于HBM和MM,传统的ESD防护措施能发挥一定作用。而未封装的裸片,其CDM电荷储存在衬底,其放电路径是由内到外,传统的HBM防护措施可能会失效。

图八.封装电荷流入内部芯片。

所以封装也是影响CDM能力的一大因素,选择合适的封装与bonding方案也能提高芯片的CDM能力。

-

ESD

+关注

关注

50文章

2424浏览量

180419 -

CDM

+关注

关注

0文章

34浏览量

12604 -

寄生电容

+关注

关注

1文章

303浏览量

20370 -

esd防护

+关注

关注

1文章

44浏览量

12824

发布评论请先 登录

绕组磁势谐波产生的原因和机理

电容的失效模式和失效机理

浅谈Silabs 的Flash 单片机丢失程序的原因及对策

什么是小尺寸集成电路CDM测试?

硬件高手提升技能,解决运算放大器CDM难以测量问题

CDM6系列断路器操作指南

日本CDM 8.0正式版已经发布下载

PCB失效或不良的准确原因和机理资料下载

HBM、MM和CDM测试的基础知识

CDM防护措施以及设计思路

什么是AEC-Q-CDM测试?

浅谈CDM的原因与机理

浅谈CDM的原因与机理

评论