三.CDM测试

目前针对CDM的测试规模主要有:ANSI/ESDA/JEDEC JS-002-2018 /IEC 60749-28/AEC-Q100-11。这三个详规都是针对封装后的芯片。

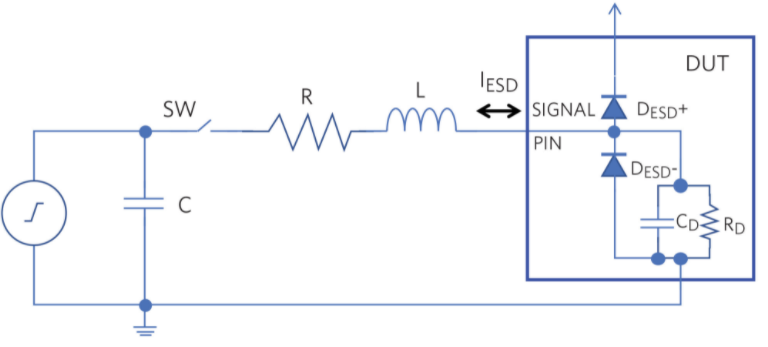

与HBM类似,CDM的测试仪器也只能提供一个静态结果,并不能得到芯片在ESD电流下的动态结果。所以采用VF-TLP对CDM波形进行近似,但是目前VF-TLP的近似程度较差,只能起到参考作用。

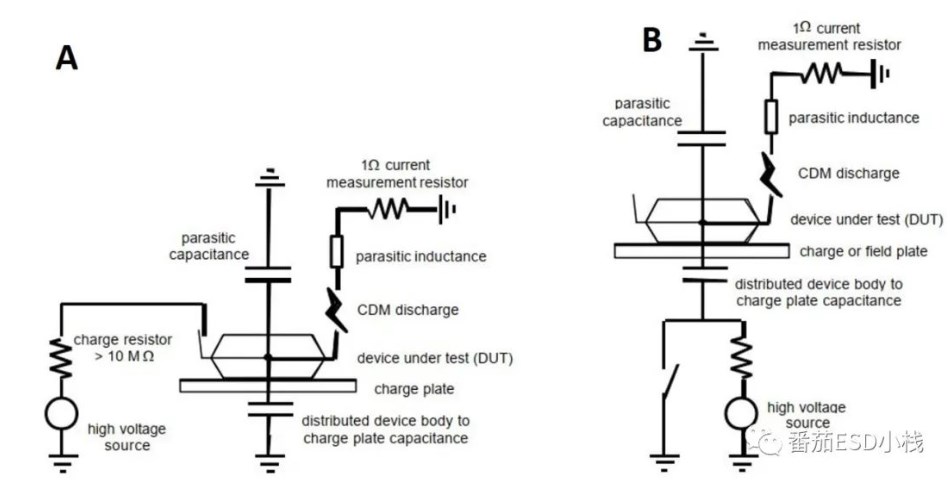

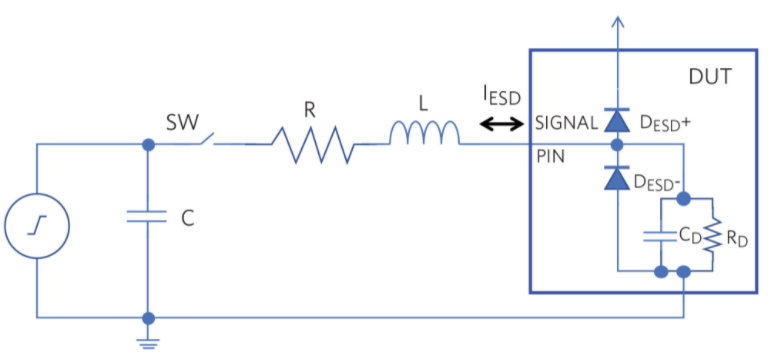

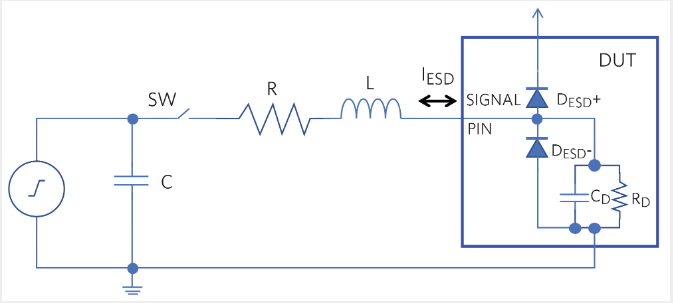

目前主流CDM的测试方法有两种:一种是直接接触测试。一种是电场测试。

图二.不同CDM测试方法,A.直接接触测试,B.电场充放电测试。

直接接触测试就是将探针直接与芯片引脚或者衬底接触,提高探针的电势从而对待测芯片进行充电,然后待测引脚连接另一根探针进行放电,实现CDM防护能力验证。电场充放电检测是将待测芯片放置到充电平板上,抬升充电平板的电势能,从而对待测芯片进行充电。笔者所经手项目多以FI-CDM(电场放电测试)为主。

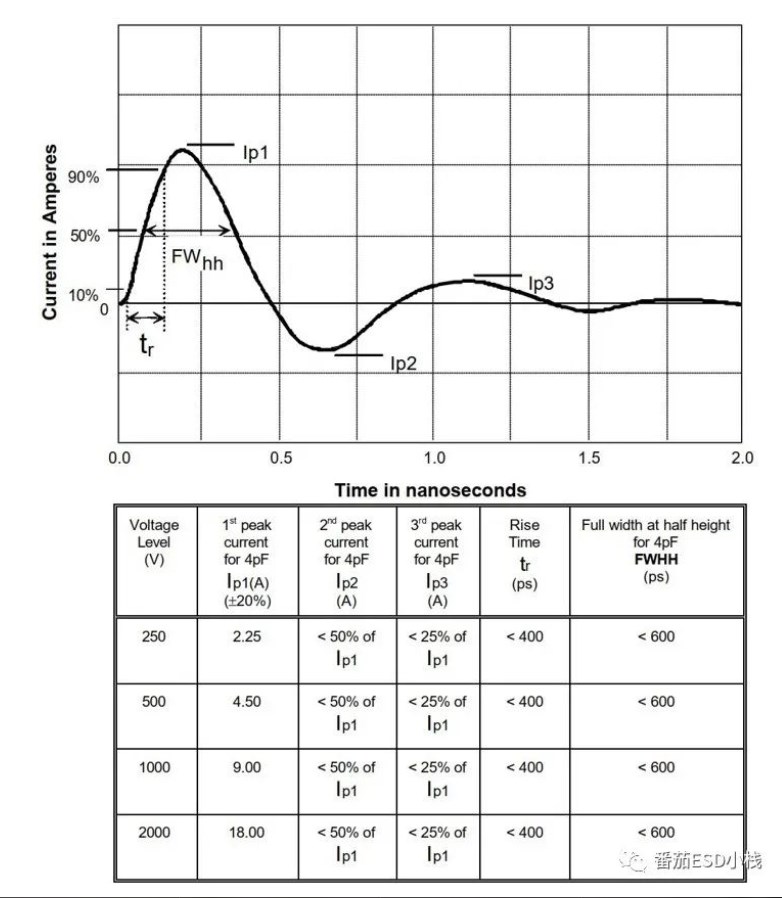

图三.CDM脉冲校验参数与波形。

测试前需要对脉冲波形进行检测,满足要求后才能对待测芯片进行测试。而针对待测芯片在测试前和测试后都需要进行ATE测试,从而校验芯片是否失效。笔者也曾遇到在ESD测试后多次ATE结果不一的情况,ESD测试后即刻ATE结果表明芯片已经失效,而一段时间后的ATE又与之前的ATE结果相左,芯片似乎恢复正常了。这种情况笔者也是较为头疼,从System ESD的角度来看,这种情况类似于Class C失效,其内部元器件肯定发生了损伤。

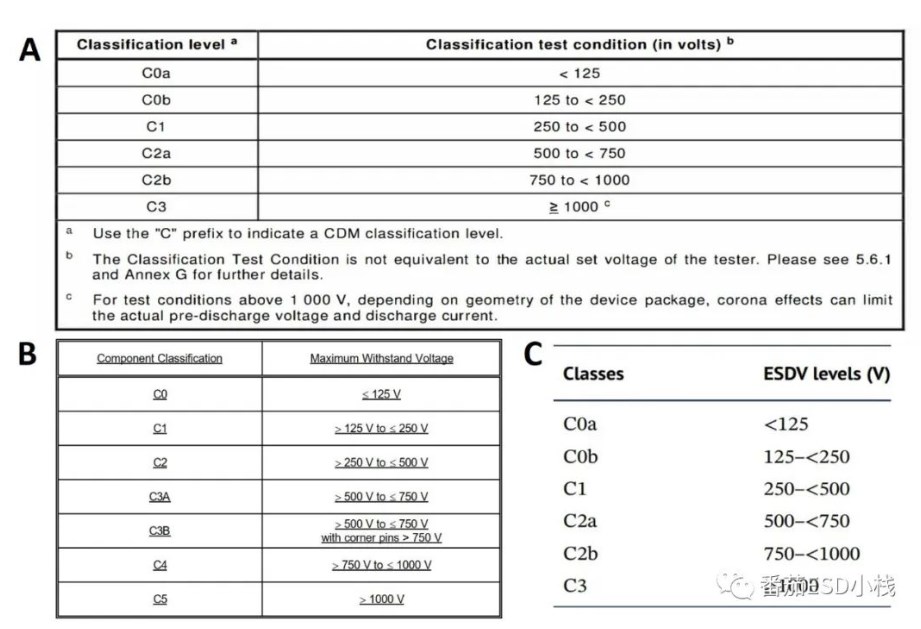

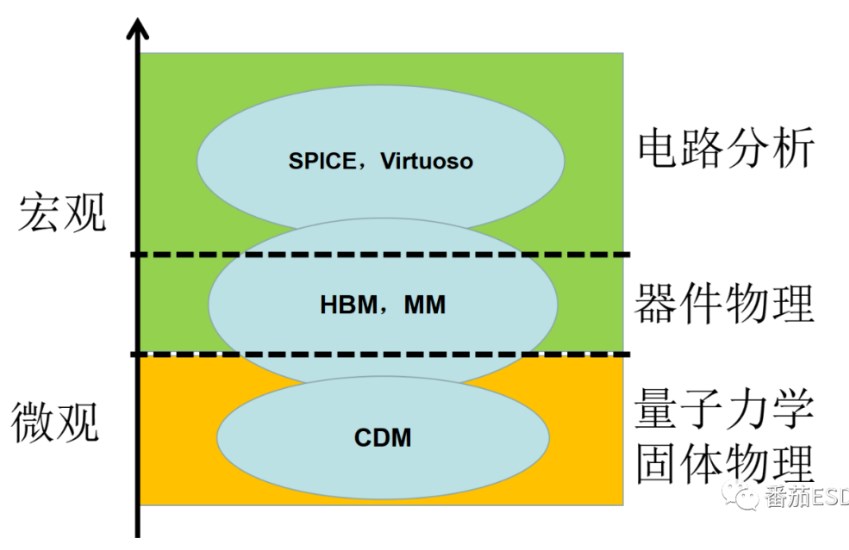

图四.IEC 60749-28/AEC-Q100-11ANSI/ESDA/JEDEC JS-002-2018 对CDM防护等级。

不同标准针对CDM防护等级的分类大同小异,都是以125V,250V,500V,750V,1000V进行划定。但是车规级AEC-Q100中单独提到了Corner Pin的问题。Corner Pin是指位于封装角落处的引脚,在DIP,SOIC,QFP,PLCC等封装方式中较为常见,其它的封装形式则需要工程师根据封装方案进行判断,这类引脚与GND的接触概率较大,所面对的风险较高,所以需要格外关注其CDM防护能力。

四.CDM失效分析

CDM的失效基本都集中在栅级,尤其是随着工艺线宽的缩减,栅氧化层的厚度越来越薄,其失效风险也显著增加。像.35这种大线宽工艺,笔者在电路设计中未考虑CDM防护,其CDM测试结果反倒出人意料的好。所以越先进的工艺越需要重视CDM风险。

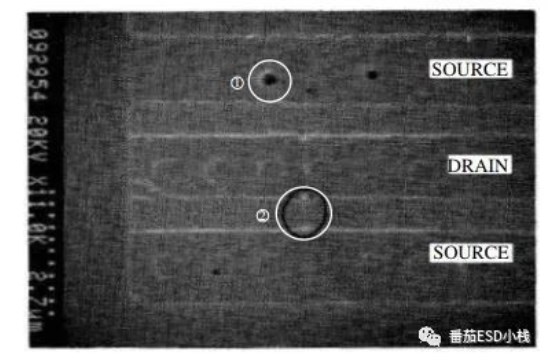

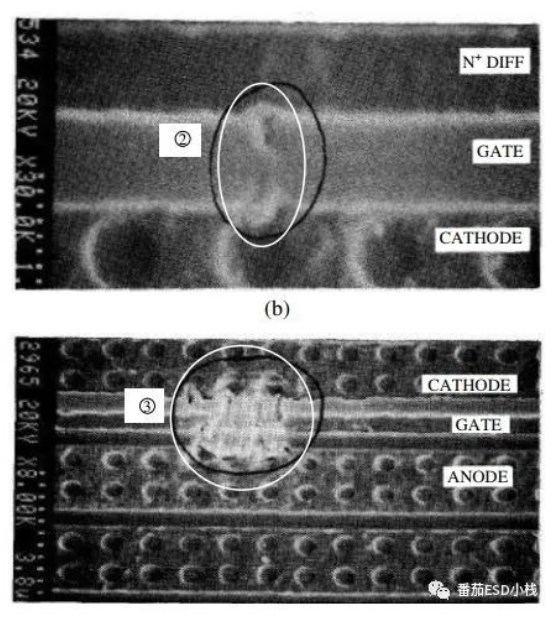

图五.GCNMOS的ESD失效分析SEM图像,②处为CDM损伤。

图六.GGNMOS和SCR的ESD失效分析SEM图像。

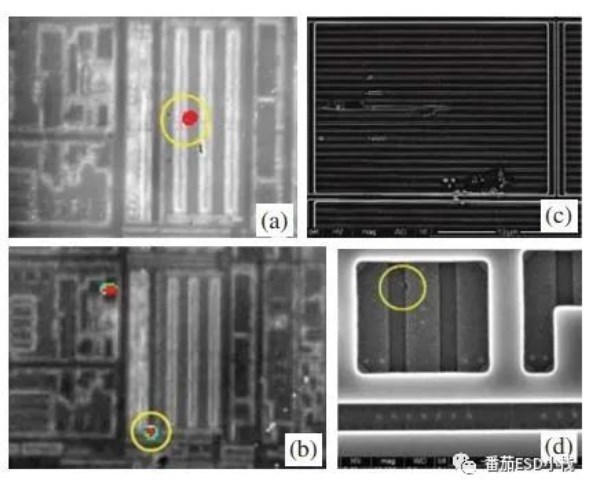

图七.45nm工艺下不同类型ESD失效SEM图像,a,c)HBM失效,b,d)CDM失效。

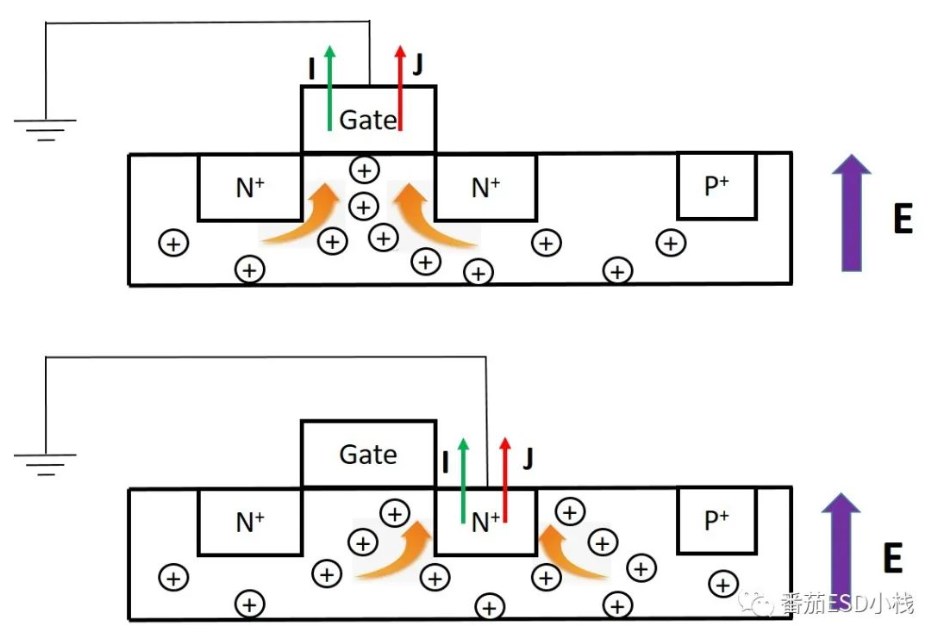

大量的实例都能看出CDM的失效全部集中在栅极。针对NMOS,正向电场下大量非平衡载流子(空穴)集中于衬底中,而当栅极接地后,栅电容两侧就会集聚大量正电荷,这部分载流子会抬高两边的电势差,当电势差过高时栅电容就会被击穿。

图八.NMOS-CDM示意图。

而如果NMOS的源端或者漏端接地,因为衬底与有源区构成寄生二极管。衬底(P-WeLL)在CDM测试中为高电位,N+有源区为低电位,载流子就会从寄生二极管流出。

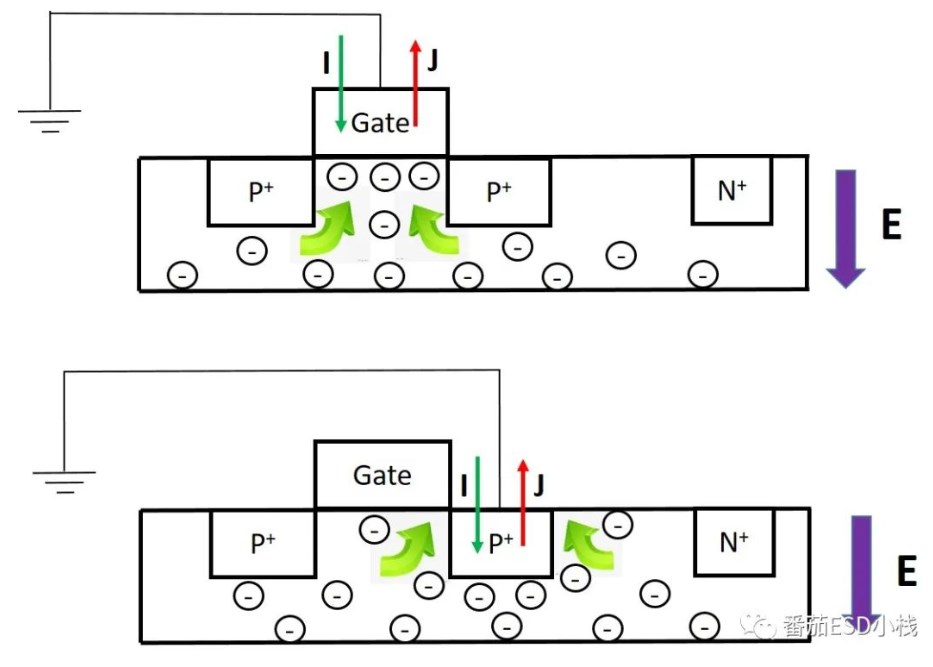

图九.PMOS-CDM示意图。

PMOS与NMOS类似,不过就是PMOS是在负场下发生CDM,其衬底内会集聚大量电子。

从电路的角度分析,CDM对栅极造成了损伤,使得电路功能发生异常。从器件物理的角度分析,CDM电荷积聚会对栅氧化层会造成物理上的破坏,图中可以看出CDM脉冲造成了栅氧化层出现了空洞。

图十.AFM下CDM失效图像。

所以CDM防护需要重点关注对于栅极的保护,但是并不一定所有的栅极损伤都是由CDM造成,尤其是输入端口的ESD事件,HBM和MM也会对栅极造成损伤。

-

ESD

+关注

关注

49文章

2129浏览量

173674 -

DIP封装

+关注

关注

1文章

41浏览量

13692 -

CDM

+关注

关注

0文章

30浏览量

12296 -

GND

+关注

关注

2文章

540浏览量

38996

发布评论请先 登录

相关推荐

什么是失效分析?失效分析原理是什么?

什么是小尺寸集成电路CDM测试?

失效分析方法---PCB失效分析

芯片IC可靠性测试、静电测试、失效分析

芯片IC可靠性测试、ESD测试、FA失效分析

HBM、MM和CDM测试的基础知识

HBM、MM和CDM测试的基础知识

常用的芯片失效分析方法

浅谈CDM的原因与机理

季丰电子CDM测试机已全部配备高带宽的6G示波器

CDM的测试与失效分析

CDM的测试与失效分析

评论