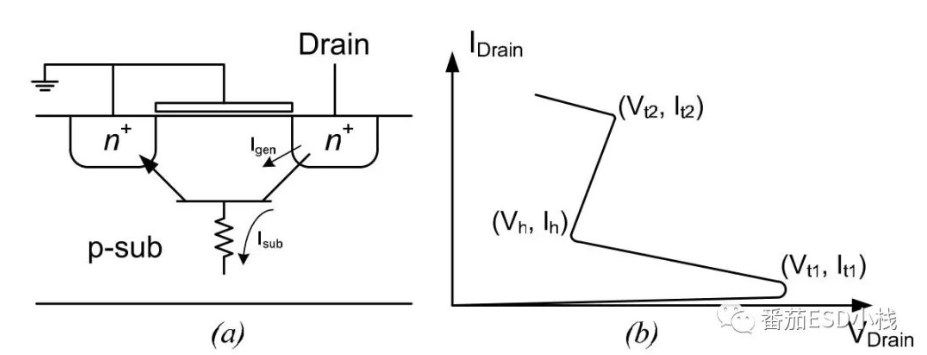

这期继续分享NMOS在ESD防护中的妙用。上期讲到改变GGNMOS中反偏结的击穿电压可以实现对Trigger Voltage的改变。而众多改变反偏结击穿电压的方法无论是改变掺杂浓度还是改变拓扑结构,其本质都是通过改变反偏结空间电荷区的电场分布来改变Trigger Voltage。

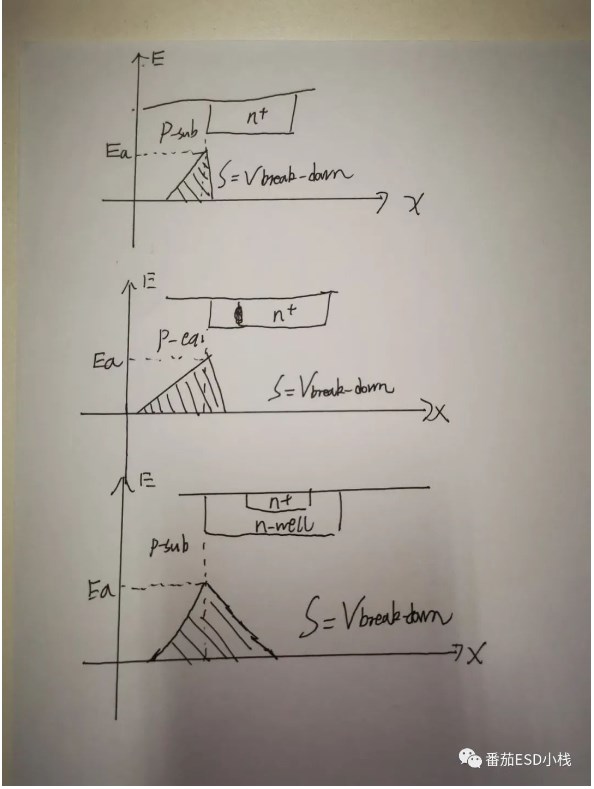

图一。掺杂浓度对电场分布与击穿电压影响示意图。

掺杂浓度越低,空间电荷区越大,电场分布越广,击穿电压也就越大。同时通过调整器件的拓扑结构也能实现对Trigger Voltage的调控。

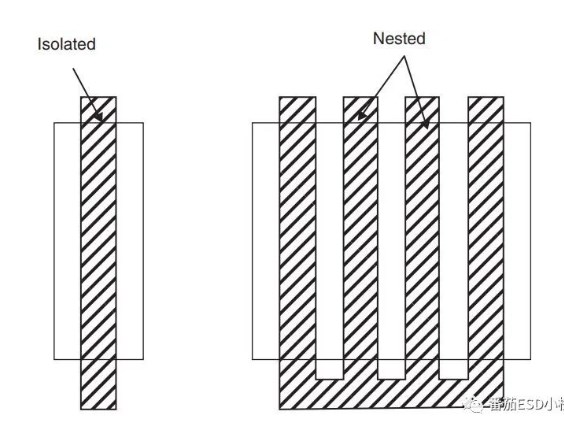

同样线宽下多指结构能分散电场分布,提高击穿电压。

图二。多指结构与单指示意图。(图片源于《ESD circuits and Device》.Voldman)

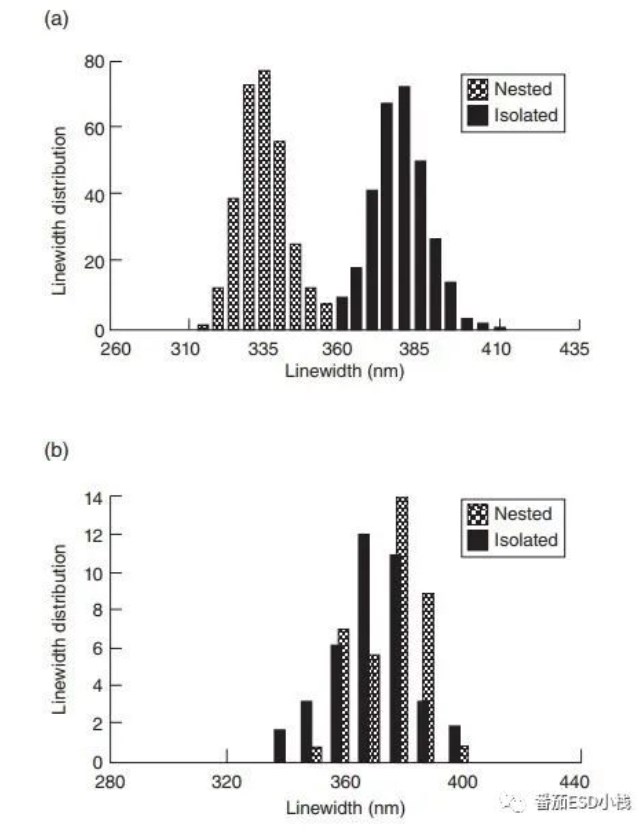

图三。叉指电流分布。(图片源于《ESD circuits and Device》.Voldman)

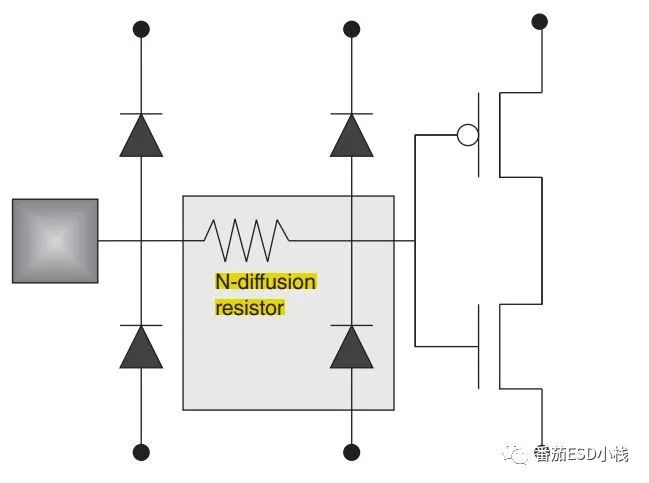

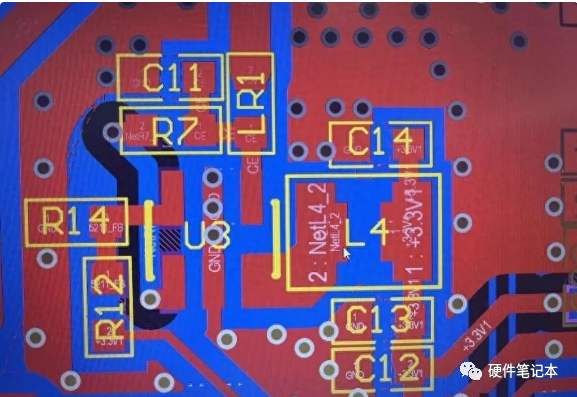

目前主流的ESD设计都采用叉指结构。无论是GGNMOS还是GCNMOS。

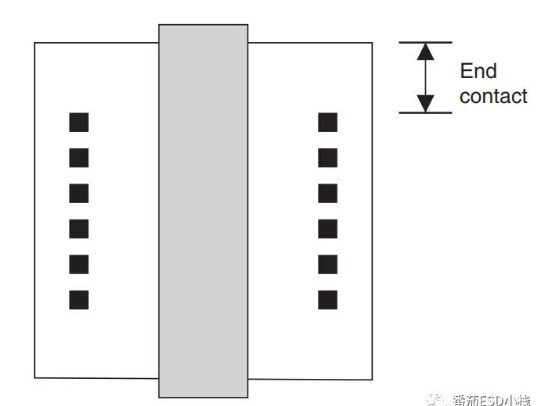

图四。尾端接触孔。(图片源于《ESD circuits and Device》.Voldman)

Voldman指出不同接触孔的电流分布是有区别的,两端的接触孔电流密度更大,调整两端接触孔的距离也能改变击穿电压。

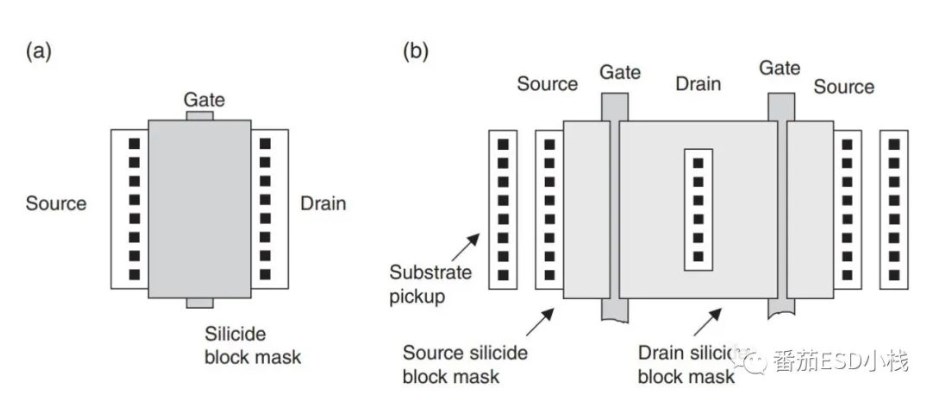

图五.Silicide示意图。(图片源于《ESD circuits and Device》.Voldman)

Silicide在保护器件的同时,也能提高器件的击穿电压。

Holding Voltage调制

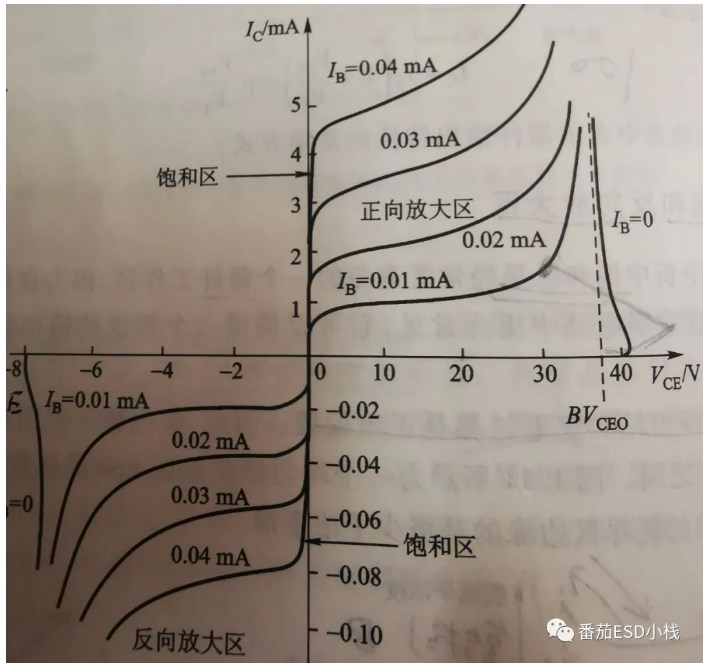

GGNMOS作为Snap-back型器件,针对其Holding Voltage的调制也是业界焦点。根据上一篇对GGNMOS机理的分析,可以得出若想改变Holding Voltage便需要改变寄生三极管中雪崩击穿载流子与漂移载流子的比例。漂移载流子累积越慢,其Holding Voltage越低。常规三极管在击穿后也存在极其微弱的Snap-Back,如图所示,因为常规BJT的基区很薄,掺杂浓度也不高,所以击穿后,漂移载流子很快能占据上风。

图六。常规BJT的I-V特性曲线。(图片源于《模拟集成电路的分析与设计》.GRAY)

已知原理后可以通过调整源漏间距,改变寄生BJT基区浓度等手段改变Holding Voltage。

业界一般很少对结构参数进行微调,因为微调带来的改变叠加工艺偏差会带来很多意想不到的结果,所以更多的需要设计人员对结构与机理进行理解。而Trigger Voltage和Holding Voltage的选取也有很多的讲究,这会单独做一期Design Window的分享。

GGNMOS最关键的参数就是Trigger Voltage和Holding Voltage,至于第二次热击穿, 更多的受制于工艺。工艺线宽越大,二次击穿越大。

-

三极管

+关注

关注

143文章

3616浏览量

122063 -

ESD

+关注

关注

49文章

2040浏览量

173101 -

BJT

+关注

关注

0文章

236浏览量

18204 -

NMOS管

+关注

关注

2文章

121浏览量

5483

发布评论请先 登录

相关推荐

浅谈ESD防护设计—NMOS的妙用(二)

浅谈ESD防护设计—NMOS的妙用(二)

评论