问题描述

客户在调试QSPI模块过程中,将TC397的QSPI模块的CPOL位设置为1,但是示波器显示时钟引脚输出信号的空闲状态并不是高电平,在debug模式下,可观察到CPOL位已设置为1,这是怎么回事呢?

图1

设置TC397的QSPI模块工作在CPOL=1, CPH =1协议模式

解决过程

SpiIf_initChannelConfig()函数在初始化QSPI channel时,提供了很多配置参数项,其中就有clockPolarity,但是单单设置clockPolarity= SpiIf_ClockPolarity_idleHigh,虽然会将CPOL位设置为1,但是捕获的波形显示空闲状态电平并未变成高电平。

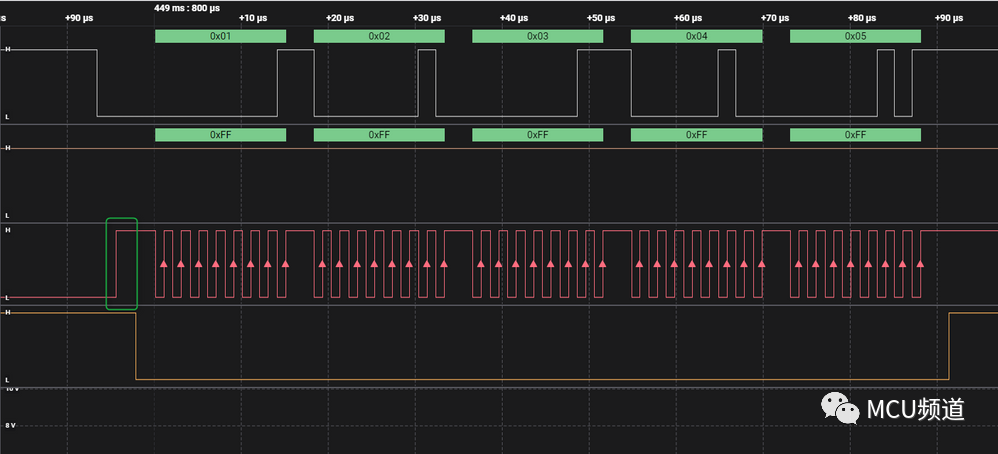

这是由于SpiIf_initChannelConfig()函数的默认参数项设置IDLE时序阶段时长为0,使得帧传输间隙缺少IDLE时序阶段,所以需要设置csInactiveDelay > 0(如下所示)来插入IDLE时序阶段,如下图所示。

voidSpiIf_initChannelConfig(SpiIf_ChConfig*config,SpiIf*driver)

{

config->driver=driver;

config->baudrate=0;

config->mode.enabled=1;

config->mode.autoCS=1;

config->mode.loopback=0;

config->mode.clockPolarity=SpiIf_ClockPolarity_idleHigh;

config->mode.shiftClock=SpiIf_ShiftClock_shiftTransmitDataOnLeadingEdge;

config->mode.dataHeading=SpiIf_DataHeading_msbFirst;

config->mode.dataWidth=8;

config->mode.csActiveLevel=Ifx_ActiveState_low;

config->mode.csLeadDelay=SpiIf_SlsoTiming_0;

config->mode.csTrailDelay=SpiIf_SlsoTiming_0;

config->mode.csInactiveDelay=SpiIf_SlsoTiming_2;

config->mode.parityCheck=0;

config->mode.parityMode=Ifx_ParityMode_even;

config->errorChecks.baudrate=0;

config->errorChecks.phase=0;

config->errorChecks.receive=0;

config->errorChecks.transmit=0;

}

图2

审核编辑:刘清

-

示波器

+关注

关注

113文章

6244浏览量

184887 -

QSPI

+关注

关注

0文章

41浏览量

12200 -

CPOL

+关注

关注

0文章

9浏览量

10048

原文标题:如何设置TC397的QSPI模块工作在CPOL=1, CPH =1协议模式

文章出处:【微信号:MCU频道,微信公众号:MCU频道】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何设置TC397的QSPI模块工作在CPH =1协议模式?

如何设置TC397的QSPI模块工作在CPH =1协议模式?

评论