作者:付汉杰 hankf@amd.com

文章来源:博客园

测试环境

参考文档

xtp226-ac701-multiboot-c-2015-1.pdf

ug470_7Series_Config.pdf

xapp1247-multiboot-spi.pdf

ug952-ac701-a7-eval-bd.pdf

ug1579-microblaze-embedded-design.pdf

Vitis Embedded Software Debugging Guide (UG1515)

测试单板

ac701

测试工具

Vivado 2022.2

Vitis 2022.2

Mutliboot

UG470 Reconfiguration and MultiBoot Overview

UG470中的介绍如下

The 7 series FPGAs MultiBoot and fallback features support updating systems in the field. Bitstream images can be upgraded dynamically in the field. The FPGA MultiBoot feature enables switching between images on the fly. When an error is detected during the MultiBoot configuration process, the FPGA can trigger a fallback feature that ensures a known good design can be loaded into the device.

AMD FPGA支持的MultiBoot特性,可以使FPGA先尝试启动最新的配置(bit)文件,后续称为Update Bit。如果最新的配置文件出错,再回退到安全的出厂版本的配置(bit)文件,后续称为Golden Bit。

MultiBoot特性有两种方式使能。第一种方式是在配置(bit)文件里嵌入IPROG命令,触发MultiBoot特性。第二种方式是通过AXI HWICAP写入IPROG命令,触发MultiBoot特性。

配置(bit)文件嵌入IPROG命令

建议阅读XAPP1247 的 “Table 1: MultiBoot Bitstream Properties”。

MultiBoot Bitstream Properties

在工程的约束文件中,加入下列设置,会自动在配置(bit)文件中插入IPROG命令。

set_property BITSTREAM.CONFIG.CONFIGFALLBACK Enable [current_design] set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x600000 [current_design] set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

上述约束的NEXT_CONFIG_ADDR,根据实际的Flash分配情况设置。

对于AC701单板,也建议添加下列约束。

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design] set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design] set_property BITSTREAM.CONFIG.EXTMASTERCCLK_EN div-1 [current_design] set_property BITSTREAM.CONFIG.SPI_FALL_EDGE YES [current_design] set_property CONFIG_MODE SPIx4 [current_design] set_property CONFIG_VOLTAGE 3.3 [current_design] set_property CFGBVS VCCO [current_design]

通过AXI HWICAP写入IPROG命令

AMD提供IP,支持通过AXI总线,访问ICAPE。

xtp226 也提供了硬件、软件设计,它支持通过AXI HWICAP写入IPROG命令,触发FPGA重新加载。

golden_iprog_spi中的golden.c, 通过读取AXI GPIO 0的状态,决定FPGA重新加载时使用的bit文件。AXI GPIO 0对应到AC701上的SW2。AXI GPIO 0的bit-0,也就是SW2的靠角落(DS23、SW4)的开关1在1的状态(靠液晶屏、7A200T芯片侧),则加载0x400000的bit文件。AXI GPIO 0的bit-0为0, bit-3为1(SW2的开关4)在1的状态,则加载0x800000的bit文件。

status = GpioInputExample(XPAR_AXI_GPIO_0_DEVICE_ID, &DataRead);

if (status == 0) {

xil_printf("GpioInput Read data:0x%X

", DataRead);

if ( (DataRead & 0x00000001) == 0x00000001 )

{

fpga_iprog(0x00400000); // IPROG to GOOD BITSTREAM ,must match address in .prm

}

if ( (DataRead & 0x00000008) == 0x00000008 )

{

fpga_iprog(0x00800000); // IPROG to cause configuration error

}

}

else {

print("GpioInput FAILED.

");

}

对比

第一种方式,通过配置(bit)文件嵌入IPROG命令,实现最简单,占用资源也最少。但是只能支持一个Update Bit文件。

第二种方式,通过AXI HWICAP写入IPROG命令,在下发IPROG命令前,可以任意指定Flash地址,非常灵活。但是需要嵌入MicroBlaze和AXI HWICAP,需要占用部分FPGA资源,也需要一点软件开发。

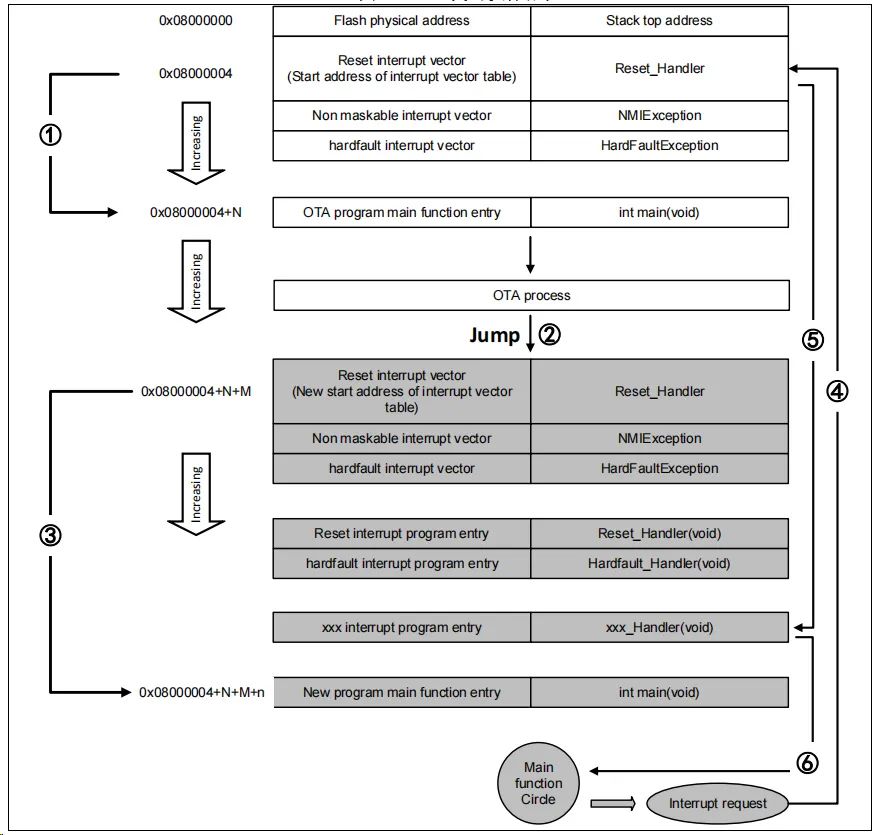

Artix FPGA OTA 在线升级的流程

首先分配Flash的存储空间。Flash里 0x0 地址存放Golden Bit;Flash里 0x400000 地址存放 Update Bit;其中0x400000需要根据压缩后的bit文件大小修改。

因为生成Golden Bit时,使用了属性“BITSTREAM.CONFIG.NEXT_CONFIG_ADDR”, Golden Bit启动后会自动加载Update Bit。

因为生成Golden/Update Bit时,使用了属性“BITSTREAM.CONFIG.CONFIGFALLBACK”, 任何Bit失败后,都会自动加载Golden Bit。

Golden bit和 Update bit内部都集成MicroBlaze、hwicap和Quad SPI Controller,都有在线升级bit的能力。

a. MicroBlaze通过Ethernet、PCIe、UART等,从外部获得新的Update Bit。

b. MicroBlaze将新的Update Bit写入Quad SPI的0x400000并校验

c. MicroBlaze写IProg命令到HWICAP,重启动FPGA

d. FPGA使用新的Update Bit配置,之后Update Bit开始工作。

如果后来芯片断电之后再上电,Update Bit能直接加载Update Bit。

审核编辑:汤梓红

-

FPGA

+关注

关注

1634文章

21832浏览量

608112 -

amd

+关注

关注

25文章

5516浏览量

134985 -

OTA

+关注

关注

7文章

592浏览量

35556 -

bit

+关注

关注

0文章

48浏览量

32147 -

Vivado

+关注

关注

19文章

819浏览量

67210

原文标题:【干货分享】AMD Artix 7 FPGA OTA 在线升级的实现

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【Artix-7 50T FPGA试用体验】xilxin Artix-7 系列FPGA相关特性

STM32 OTA升级如何实现呢

分享一项可在线OTA升级的嵌入式系统设计

Xilinx Artix-7系列FPGA教程资料及设计实例_Artix 7开发板电路图和例程

如何使用Artix-7 FPGA减少功耗

digilent Nexys 4:Artix-7 FPGA训练板介绍

在线升级 | 物联网中的OTA升级原理

在Artix 7 FPGA上使用Vivado的组合逻辑与顺序逻辑

AMD Artix 7 FPGA OTA在线升级的实现

AMD Artix 7 FPGA OTA在线升级的实现

评论