在前文《片内封装级互联—奎芯Chiplet D2D 接口技术》中有提及Chiplet其实不是新技术了,FPGA很早的时候就采用Chiplet技术,甚至用了3D的封装,但是这些产品的出货量比较小,也不具备典型性,直到15,16年AMD ZEN系列处理器出来后,这个技术才被广泛的传播开来。所以小编今天想从AMD 霄龙处理器对外发布的一些公开信息中,通过分析AMD霄龙处理器内部Chiplet结构的演变,来看看能有什么新发现。

Zen是AMD开发的全新x86处理器核心,是一种微处理器架构,采用Zen微架构的处理器名气最大当属霄龙(针对服务器的平台)和锐龙(针对桌面的平台),而从霄龙二代和锐龙三代开始,AMD采用就采用CPU die + IO die 的Chiplet组合方式来扩展CPU算力,其中CPU die简称CCD(Zen架构将以四个核心为一个群组,AMD将其称为“CPU Complex”(CCX),也就是“CPU复合体”的意思,每两个CCX组合成一个CCD),IO die简称IOD。

可以看到霄龙3代和2代的核心参数改变不大,3代CCD和2代的CCD都是采用台积电7nm的工艺,但是从Zen2架构到Zen3架构的改变还是蛮大的,比如AMD将原来Zen2 CCX中三级缓存16MB+16MB拆分设计改成1个32MB+,以降低内核对三级缓存的访问延迟。3代霄龙的IOD从2代采用的GF14nm工艺升级到12nm工艺,GF12/14nm应该是一个节点,12nm是14nm的改良版,能够获得更紧凑的面积和更低的功耗,IOD的结构和功能并没有明显的改变。

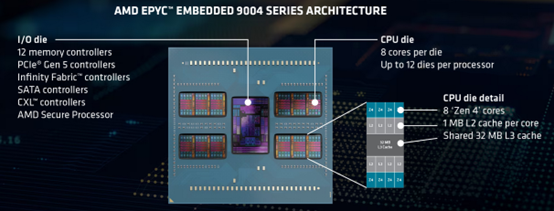

霄龙4代相比3代提升还是很明显的,首先支持最大核心数从64核提升到96核,也就是单IOD最多可支持12个CCD的组合,一共有13个Chiplet小芯片构成。CCD也从台积电的7nm升级到5nm,IOD的升级尤为明显,由于GF不再涉足7nm Finfet及更先进的工艺,IOD也采用了台积电的6nm工艺,片上内存,PCIe等接口都获得了极大提升。

图3:霄龙二代IOD的内部照

图4:霄龙二代IOD的功能框图

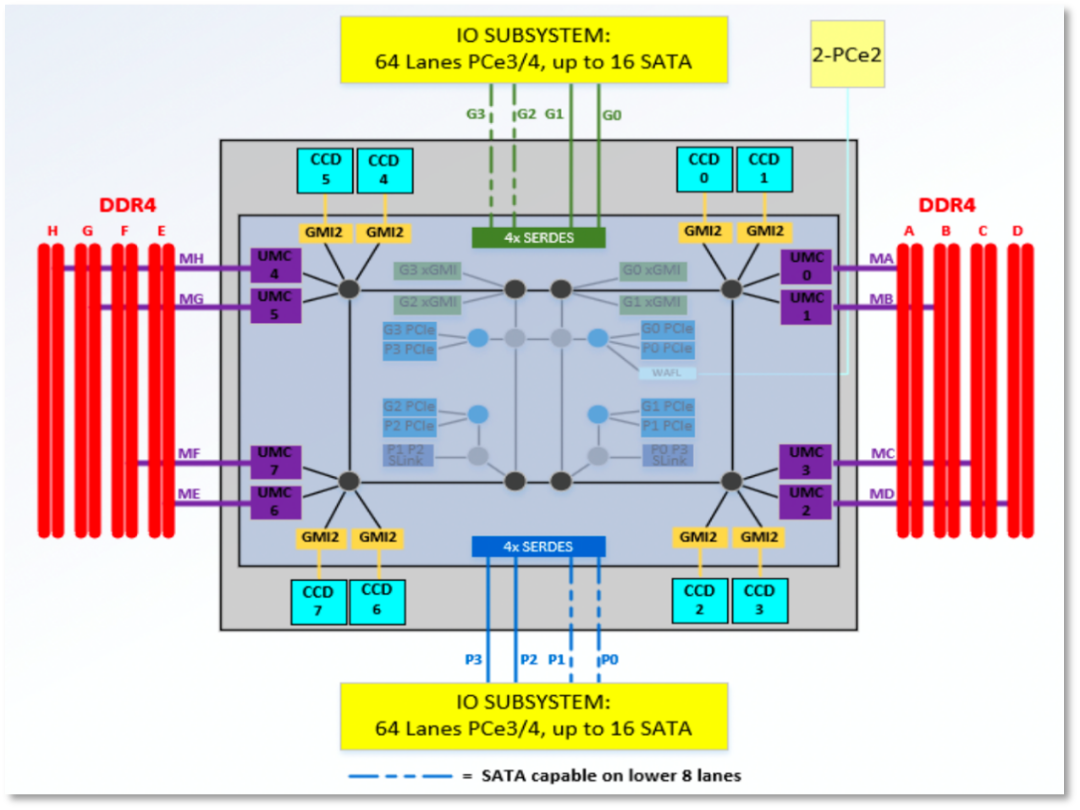

图3是一个二代霄龙IOD的内部照,IOD拥有 83.4亿个晶体管、416平方毫米,左右两侧紫色的是分成八组的双通道DDR4的PHY,总位宽576-bit,最高频率3200Mhz,紧挨着DDR PHY的标注MC的是DDR控制器;中间上下红色的是支持PCIe Gen4 的SerDes PHY,总计128条;在旁边紫色标注CCD IFOP PHY的部分则是GMI2接口的PHY,通过AMD Infinity Fabric技术连接CCD和IOD,可以理解为AMD的D2D的接口。

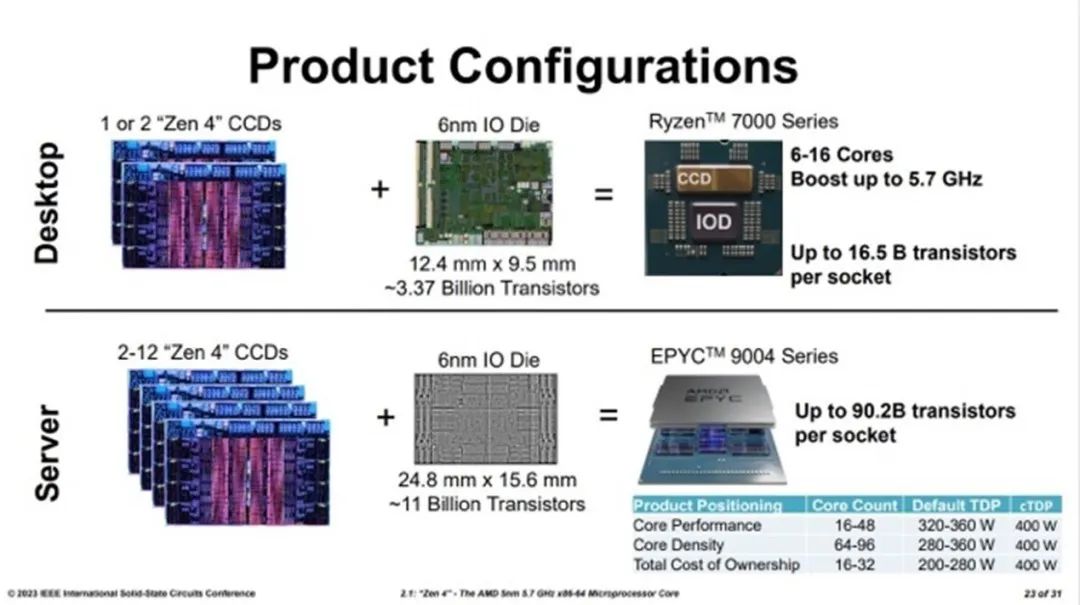

图5:Zen 4架构下霄龙4代和锐龙7000系列的IOD

IEEE ISSCC 2023国际固态电路大会上,AMD披露了部分霄龙4代IOD的信息,可以看到台积电6nm工艺下霄龙4代IOD的面积仅为24.8×15.6=386.88平方毫米,多支持4个CCD的情况下面积依旧小于2代的IOD,总计约110亿个晶体管,晶体管密度提升显著。同时这边还披露了锐龙7000系列的IOD,也是基于6nm工艺,但是桌面应用中的核显集成在IOD中,所以结构上不能简单的认为是霄龙4代IOD的简化版。

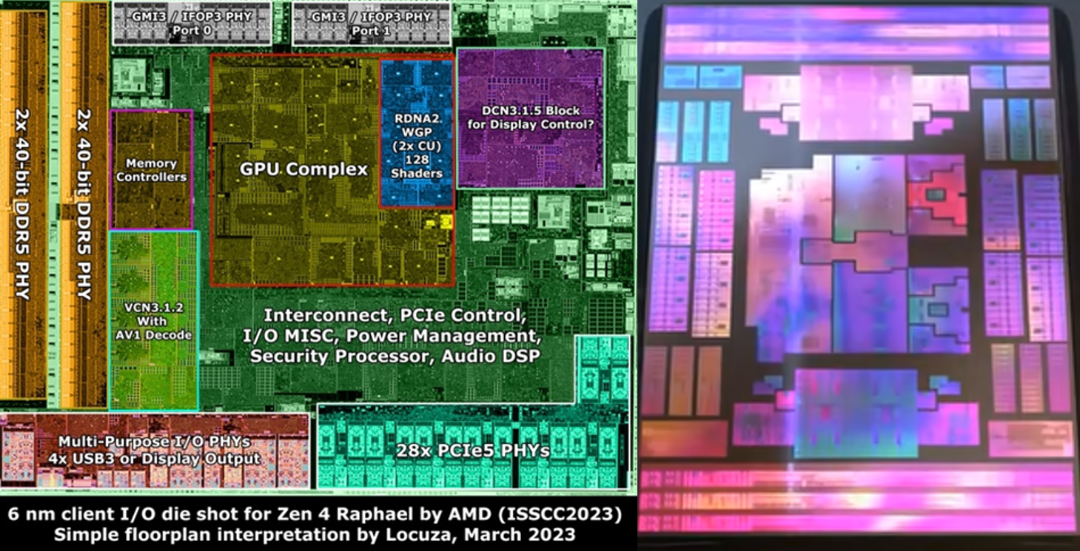

图6:锐龙IOD的详细布局图+霄龙4代IOD的渲染图

目前由于未能找到霄龙4代IOD的实图,辅以图6右侧AMD渲染美图替代,图6左侧是锐龙IOD的详细布局图,我们借其标注的一些接口来看看4代霄龙IOD有哪些提升。

内存接口方面,霄龙4代拥有12 通道 DDR5-4800,从通道个数上比上一代多50%,AMD还将从DDR4-3200速度提高到DDR5-4800速度,从而大幅提升每通道带宽。

霄龙4代利用出色的SerDes性能,每个处理器依旧是128通道,64(或4×16)支持xGMI(插槽到插座Infinity Fabric)和PCIe Gen5(霄龙二代和三代是PCIe Gen4)。其他64个通道支持xGMI,PCIe,CXL和SATA。另外还有一些额外的PCIe3.0*8的通道,支持SATA低速传输,霄龙2代和3代中则有4个。

GMI接口也从GMI2升级到GMI3了,第四代 EPYC(霄龙)CPU 可将 8 核 CCD 的数量从 4 个扩展到 12 个,4* CCD 变体(最多 32 个内核)有一个有趣的技巧,它们可以为每个 CCD 获得 2 倍的 IO 芯片链接,也就是单CCD可以通过两个GMI3链路连接到IOD,而12 和 8 CCD 变体只有一个 GMI3 链路连接到 IO芯片。

AMD采用Chiplet技术打造CPU的策略所引发的市场关注和业绩来看,已经形成了正向的反馈。IOD可以选择最适合的工艺节点,不用紧跟CPU core采用最先进的工艺节点,可以每两三代处理器更新的时候再做一次大的迭代,性价比简直拉满。从二代霄龙的IOD可以看到占据芯片面积最大的部分是各类高速接口的PHY,其次是它们的控制器电路,在数据大爆炸的时代,高性能计算离不开高速接口IP的支持,从高速接口IP占据IOD芯片面积的比例,其重要性已不言而喻。奎芯科技在DDR类和SerDes类接口均有布局,已陆续研发推出LPDDR、HBM、PCIe、SerDes、MIPI、USB、ONFI等IP和解决方案,针对大算力芯片Chiplet应用,奎芯科技可以提供M2LINK-D2D的方案,采用DDR架构,支持UCIe和中国Chiplet互联标准。

审核编辑 :李倩

-

控制器

+关注

关注

112文章

16402浏览量

178588 -

接口

+关注

关注

33文章

8650浏览量

151409 -

IP

+关注

关注

5文章

1712浏览量

149666

原文标题:从AMD CPU IO Die演进看高速接口IP发展趋势

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

未来物流发展趋势与TMS的关系

Type-C接口的未来发展趋势

边缘计算的未来发展趋势

未来AI大模型的发展趋势

从小鹏、理想、蔚来布局看自动驾驶发展趋势

变阻器的未来发展趋势和前景如何?是否有替代品出现?

高速光耦发展趋势与应用前景

DC电源模块的发展趋势和前景展望

中国网络交换芯片市场发展趋势

制冷剂的发展历程与发展趋势

3D HMI应用场景和发展趋势

DC电源模块的未来发展趋势

从AMD CPU IO Die演进看高速接口IP发展趋势

从AMD CPU IO Die演进看高速接口IP发展趋势

评论