大家好!今日分享一些关于Video In to AXI4-Stream IP 核的知识。在具体学习IP核的过程中,我也将分享一些关于如何看xilinx英文文档的技巧。相比于翻译的xilinx中文文档,直接看原汁原味的英文文档当然是最好的。或许我们一开始看起来会很费劲,但是我们看多了后就会知道先看哪一部分,以及常用的重复频率高的专业词汇是什么意思。再次提醒下大家,翻译的中文文档是辅助作用,大家最终一定要学会看英文文档,英文文档才是最准确的,这是成为一个合格的FPGA工程师的必备技能。下面进入对Video In to AXI4-Stream IP 核的介绍。

通常来说,官方给的xilinx英文文档通常都含有以下几个章节:

这几个章节也是我们经常看的,至于其他什么Example Design、版本修订等章节都很少看。

当我们需要学习一个完全陌生的IP核时:

首先,我们应该看第一章:Overview,对IP核有一个大概的了解。就像公司来了新同事,首先我们看到的是他的外表,最先了解的是他的名字、工种等大致的内容。

其次,我们要去看第二章:Product Specification,第二章又要先看Port descriptions,即IP核的引脚(管脚)信息。为什么呢?这一点如果你做过Zynq相关项目就能够理解了。通常我们需要在block中把各个IP核连线,而连线的点就是各个IP核的引脚。如果引脚连错了,Vivado会疯狂报错。

再次,就是第三章:Designing with the Core。这一章通常会对IP核使用的时钟、复位以及其他使用要点进行讲解。

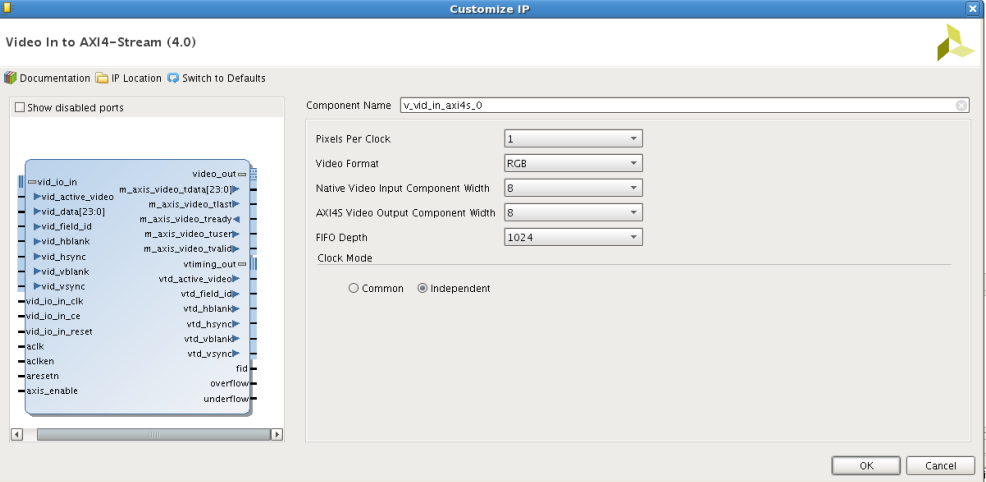

最后,就是第四章:Design Flow Steps。对于我们一开始应用IP核时,最想看的其实就是第四章,因为其中有对IP核的各个参数的解释。也就是我们在Vivado中调出IP后需要选的那些参数以及参数的含义,都包含在第四章Design Flow Steps中。如下图界面就是调出IP核后的界面,这是不是我们最想看的内容呢?

当然,这只是我个人的经验,仅供参考。有的朋友也会直接看第四章:Design Flow Steps。因为调出IP核后不就是设置参数这些操作嘛!管它是啥,就是干!哈哈。

以上是方法论,就是对于不同的文档都可以这样看,这样用。

-

Xilinx

+关注

关注

71文章

2163浏览量

120971 -

Video

+关注

关注

0文章

195浏览量

45159 -

引脚

+关注

关注

16文章

1179浏览量

50254

原文标题:Video In to AXI4-Stream IP核介绍

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Video Frame Buffer IP初学者入门案例分析

有人有经验AXI4-Stream到视频输出IP核吗?

请问我对AXI4-Stream FIFO的理解不正确吗?

请问AXI4-Stream到Video核心的技巧有什么?

如何将AXI4-Stream与CH7301接口?

axi4-stream互连问题如何解决

axi4-stream combiner问题的解决办法?

AXI-stream数据传输过程

Xilinx的LogiCORE IP Video In to AXI4

AXI-Stream代码

关于AXI4-Stream协议总结分享

AXI4-Stream Video 协议和AXI_VDMA的IP核介绍

AXI4 、 AXI4-Lite 、AXI4-Stream接口

LogiCORE IP AXI4-Stream FIFO内核解决方案

Video In to AXI4-Stream IP核知识介绍

Video In to AXI4-Stream IP核知识介绍

评论