微系统技术是突破摩尔定律极限的重要解决途径之一,受到广泛关注。微系统的实现途径有SoC、SiP和SoP三个层级,其中SiP和SoP以其灵活性和成本优势成为近期最具应用前景的微系统集成技术。综述了SiP和SoP的技术内涵、集成形态以及关键技术,为微系统集成实现提供参考。

关键词:微系统;系统级封装(SiP);基于封装的系统(SoP)

0 引言

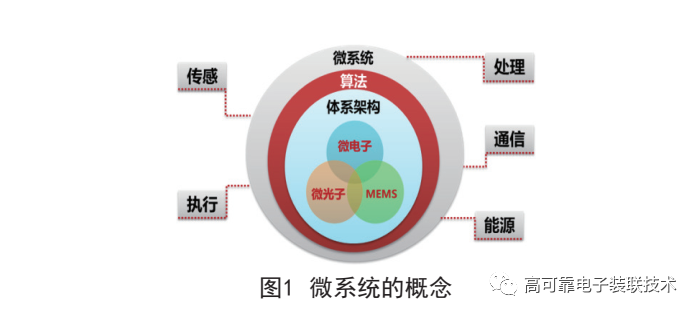

微系统是融合体系架构、算法、微电子、微光子、微机电系统(Micro Electro Mechanical Systems,MEMS)五大要素,采用新的设计思想、设计方法、制造方法,将传感、处理、执行、通信、能源等五大功能集成在一起,具有多种功能的微装置[1]。其中,体系架构是构建微系统的骨架,功能算法是微系统的灵魂,微电子、光电子、MEMS等是微系统的基本元素,学科交叉融合是微系统创新的源泉(如图1所示)。

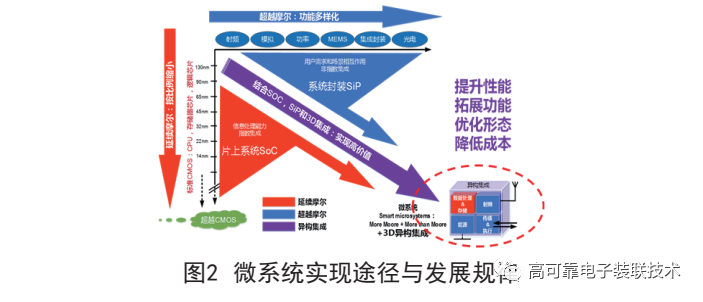

近年来,微电子技术的发展已经从单一的摩尔定律向超越摩尔定律发展,即在尺度缩小的基础上更加突出功能的融合。微系统的发展与微电子和集成技术的发展息息相关,微电子沿着摩尔定律继续发展,它追求的是更小的纳米尺度工艺,以此推动集成电路向更高的集成度方向发展。

集成技术沿着超越摩尔定律的方向发展,它面向应用,通过射频、模拟、光电等多种功能的融合集成提升集成密度[2]。微系统集成则是综合了延续摩尔和超越摩尔两条路径的最新成果,通过三维异质异构集成实现更高的价值(如图2所示)。系统的多功能融合和多专业多学科高度交叉给集成制造能力和工艺技术带来了前所未有的机遇与挑战。

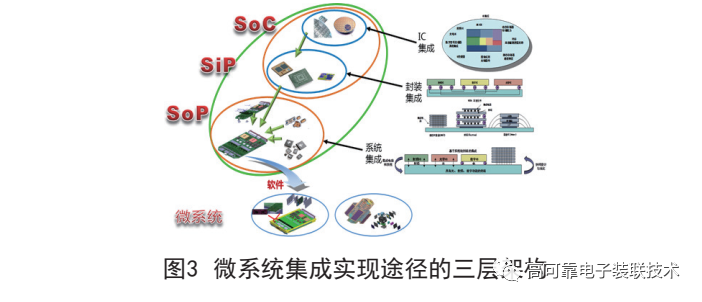

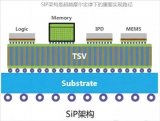

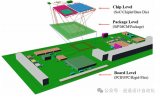

微系统有三种典型的实现路径,分别是SoC(Systemon Chip,片上系统)、SiP(System inPackage,系统级封装)和SoP(System on Package,基于封装的系统),其中SoC是芯片级的集成,SiP是封装级的集成,而SoP是系统级的集成。多功能芯片是SoC,基于封装基板和多功能芯片的高密度集成构成SiP,若干个具有特定功能的SiP及其他辅助元器件与系统母板集成构成SoP,而SoP再与系统软件结合最终构成了面向用户的微系统产品。系统软件与功能算法是微系统的“灵魂”,而SoC、SiP和SoP构成了微系统的“肉身”,成为微系统的物理实现途径(如图3所示)。

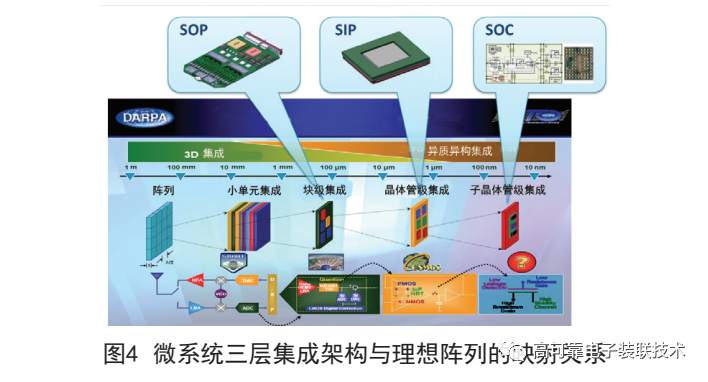

在三层架构的微系统集成实现途径中,SoC期望在单芯片上通过异构甚至异质的方式集成多个系统功能,是微系统的终极目标,但其受限于材料和工艺兼容性等问题,技术难度大,研发周期长,成本高昂,还无法实现大规模的集成。

因此,目前更多是以多功能芯片的形态存在,必须与其他技术手段相结合才能实际应用于电子装备和系统。SiP是将多种异构芯片、无源元件等采用二维或三维形式集成在一个封装体内。其具有更高的灵活性,更高的综合集成密度,更高的效费比,是目前微系统集成的热门研究领域。

然而,SiP由于其本身集成规模的限制,以及部分功能集成手段的制约,仍很难综合解决散热、电源、外部互连和平台集成等系统必备需求,也仍无法构成独立的系统。SoP则是面向系统应用,基于系统主板,将SiP、元器件和连接器、散热结构等部件集成到一个具备系统功能的广义封装内。SoP可以加载系统软件,可以具有完整的系统功能,是功能集成微系统最合理、最直观的集成形势,也是整机和系统的核心集成能力[3]。

如图4所示,在DARPA提出的理想阵列中,也可以见到从SoC到SiP,再到SoP最终到系统的实现过程,其中需要从纳米到微米,再到毫米的跨越多个尺度的集成制造手段。

本文将重点分析SiP和SoP的内涵形态与关键技术。由于SoC的集成关键技术主要集中在微电子芯片工艺,在本文中不做重点论述。

1 SiP的内涵形态与关键技术

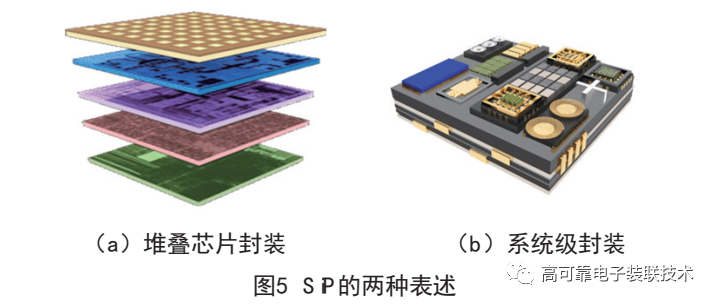

如图5所示,SiP在集成封装行业中有两种不同的表述,分别是堆叠芯片封装(Stacked ICs andPackage)和系统级封装(System in Package)。其中,后者的使用较为广泛。然而,这两种表述具有很强的互补性,其关键技术共同构成了SiP的丰富内涵。堆叠芯片封装的关注焦点在芯片和芯片的堆叠形态,可以理解为芯片级/晶圆级的集成封装。系统级封装则更多的关注功能的融合,主要依托于多功能的封装基板,可以理解为基板级的集成封装。

1.1 堆叠芯片封装

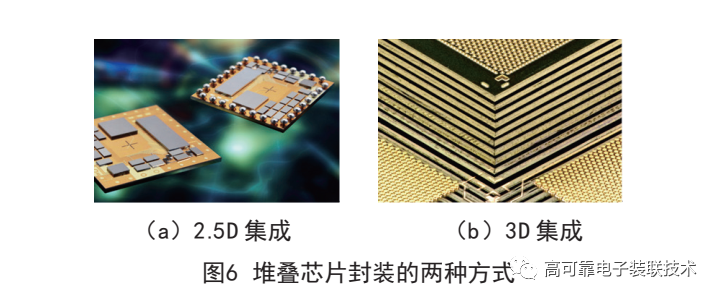

堆叠芯片封装的集成形态是在硅、玻璃或其他材料的圆片或晶圆上通过微米级的工艺手段集成各类裸芯片与无源元件。该集成方式具有微米级的线宽和精度,具有高精度、高密度集成特点,是半导体工艺向上拓展后在异构集成中的应用。然而,与SoC类似,堆叠芯片封装的集成规模、功能复杂度相对较低,结构强度较低,环境适应性较弱,当前较难直接在系统中集成应用,通常需要进行二次封装。如图6所示,堆叠芯片封装的集成形态既包括以转接板为过渡的2.5D集成,也包括芯片/晶圆直接堆叠的3D集成[4]。

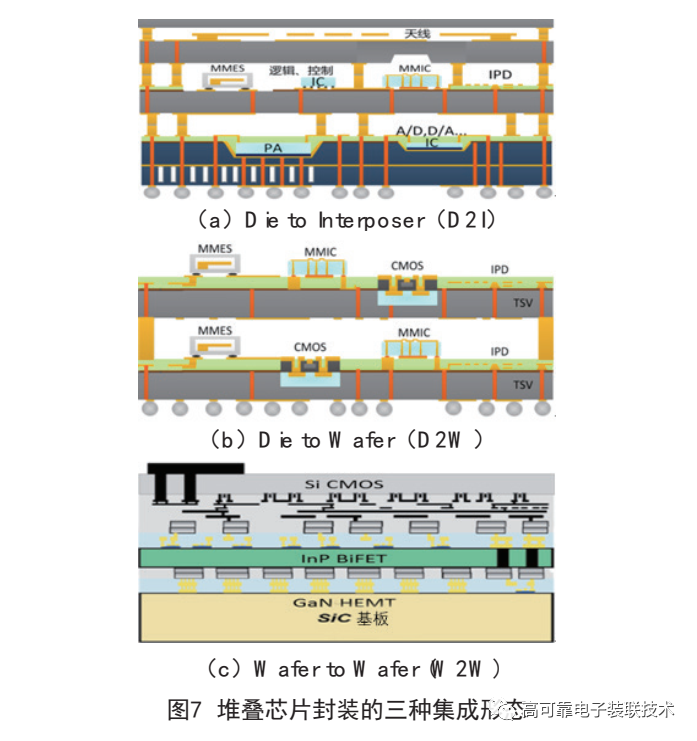

如图7所示,在2.5D和3D集成的基础上,堆叠芯片封装有三种典型的集成形态:

1)D2I(Die toInterposer):制作带TSV(ThroughSi Vias,硅通孔)互连通孔、IPD(集成无源元件)和微通道散热的硅基无源转接板,表面集成有源器件后三维堆叠。

2)D2W(Die toWafer):对已有CMOS(ComplementaryMetal-Oxide-SemiconductorTransistor,互补金属氧化物半导体)晶圆做重布线和TSV互连通孔,表面集成其他非CMOS器件后三维堆叠。

3)W2W(Waferto Wafer):各同类或异类晶圆直接三维堆叠键合集成。

其中D2I是典型的2.5D集成形态,D2W进入到3D集成领域,而W2W是典型的3D集成形态。三种集成形态的兼容性、灵活性和技术成熟度可以简单排序为D2I>D2W>W2W[5-7]。

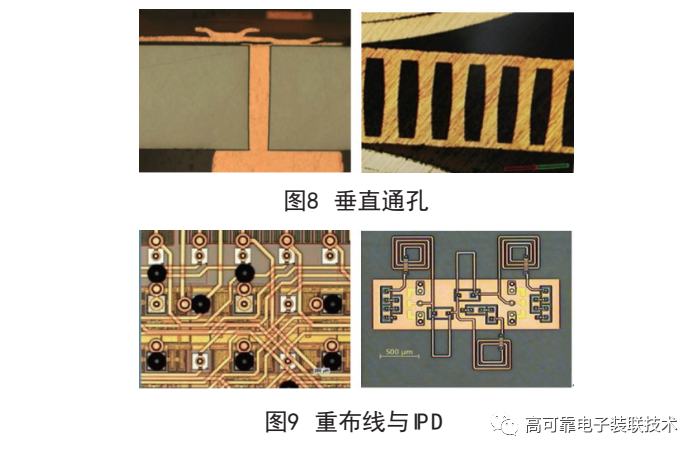

堆叠芯片封装主要采用晶圆后道工艺,有三项主要关键技术:垂直通孔、重布线与IPD集成和互连与键合。

如图8所示,垂直通孔是通过硅、玻璃等转接板或晶圆内的互连通孔,实现信号的高密度低损耗垂直互连。典型孔径为550 μm,典型深径比为5:110:1。

如图9所示,重布线与IPD集成是通过转接板/晶圆表面的多层重布线,实现裸芯片与晶圆间,晶圆与晶圆间的接口匹配,同时将占据表面的部分无源元件内埋。典型线宽为2~10 μm。

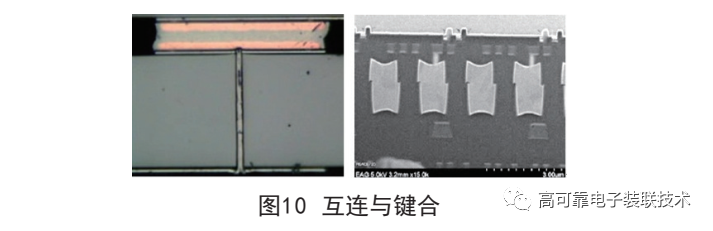

如图10所示,互连与键合是通过同质/异质材料的键合集成,实现裸芯片与晶圆间,晶圆与晶圆间的机械连接和电气互连。键合方式包括金属键合、高分子键合、硅-硅/氧化硅-氧化硅/硅-氧化硅键合等[8-10]。

1.2 系统级封装

系统级封装的集成形态是以高密度基板为核心,集成组装射频、模拟、数字、光电等各类元器件,构建高性能核心功能单元,实现芯片的互连、散热和环境适应性防护[11]。该集成方式与晶圆级集成相比集成规模更大,功能更复杂,结构强度更能适应各种复杂环境需求(如图11所示)。相应的,该集成方式的集成密度相对晶圆级集成较低。

系统级封装主要采用封装工艺,有三项主要关键技术:高密度基板、多功能异构组装、封装与防护和封装多层堆叠(Package on Package,PoP)。

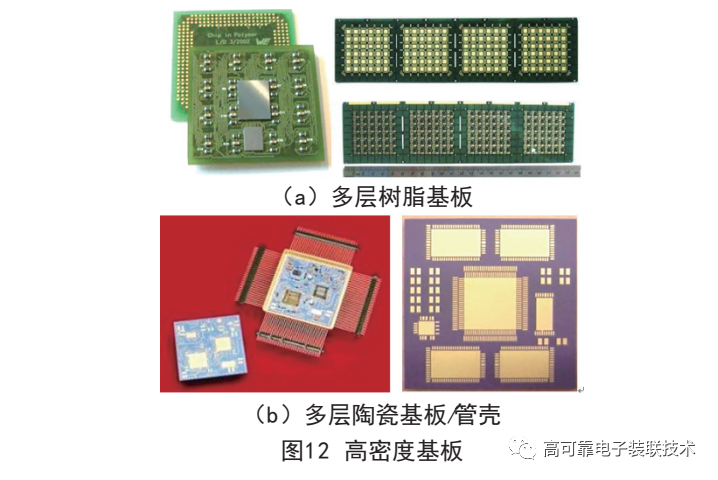

高密度基板是SiP集成的物理载体,其功能包括元器件之间的电气互连,传输射频、模拟、数字等信号;内埋集成部分无源元件,包括电容、电阻、电感,以及功分器、滤波器等;为元器件提供散热通道。常用的SiP封装高密度基板包括多层树脂基板和多层陶瓷基板/管壳,其选择的影响因素包括线条宽度、布线层数、后续封装防护方式等(如图12所示)。

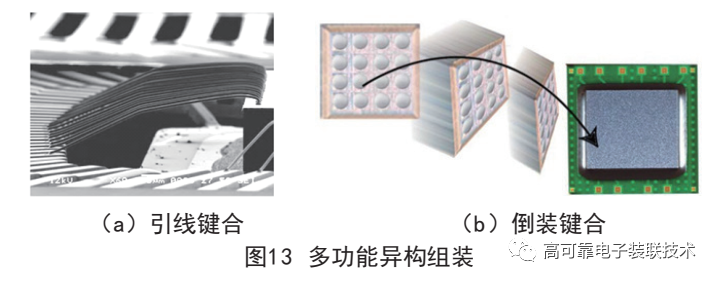

如图13所示,多功能异构组装是通过引线、倒装等主要手段,将数字、模拟、射频甚至光电器件通过键合集成组装在高密度基板上,实现特定的部件功能。其还包括粘接、贴片、底部填充等集成关键技术。

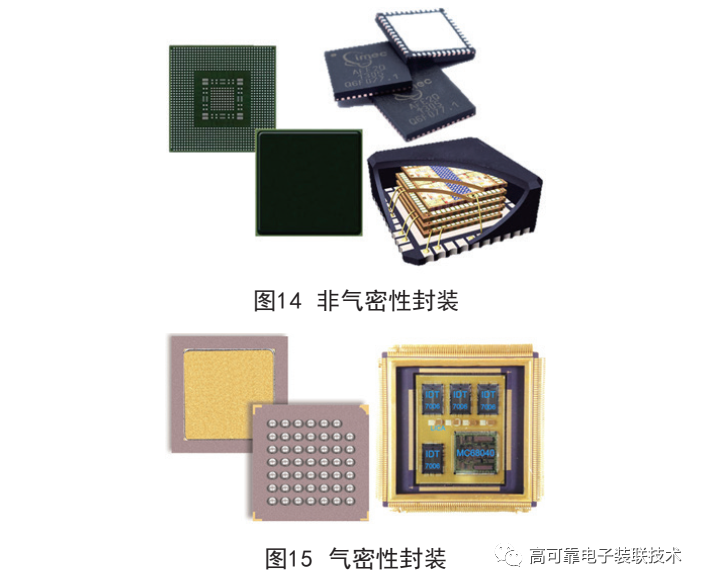

封装与防护是以一定的手段将较脆弱的芯片保护起来,以满足特定应用下的环境适应性要求和可靠性要求。根据应用领域的不同和对环境适应性可靠性的要求不同,可以采用非气密性封装和气密性封装(如图14和图15所示)。其中,非气密性封装用于对可靠性要求较低的场合,包括塑封、包封、粘接金属盖等手段实现保护与电磁屏蔽。气密性封装主要用于高可靠场合,包括陶瓷/玻璃封装、金属封装等手段。

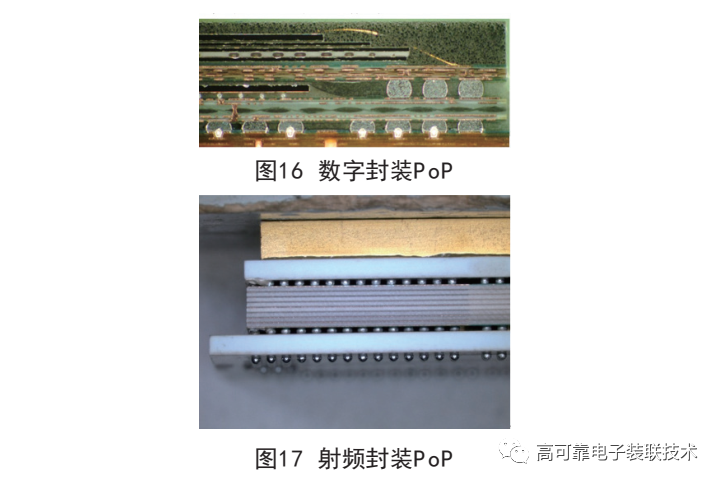

多层堆叠:与芯片和晶圆级的三维堆叠类似,SiP封装在平面上的集成空间已经不足,可通过三维堆叠集成,在提升集成密度的同时,降低互连长度,提升性能(如图16和图17所示)。

2 SoP的内涵形态与关键技术

在一个电子系统中,半导体IC芯片通常只占体积的10%,通过SoC和SiP技术可以解决系统体积10%~20%的缩减。其余空间则被大量的分立无源元件、电路板及其线缆连线占据。SoP提供了解决这80%~90%问题的系统集成路径,通过“超越摩尔定律”的方式,从根本上大幅提升系统集成密度,成数量级降低系统整体的体积质量(如图18所示)。

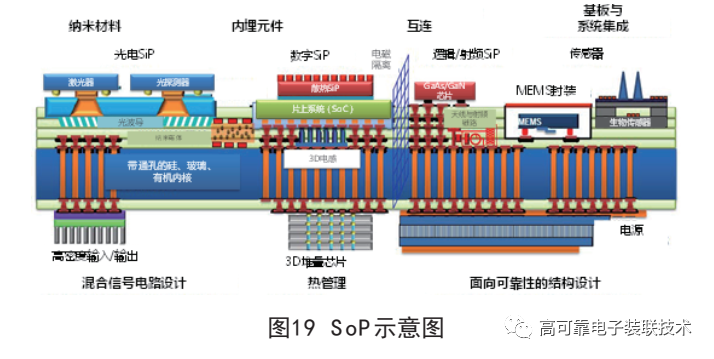

如图19所示,SoP是基于封装的系统,是基于系统主板,将SiP、元器件和连接器、散热结构等部件集成到一个具备系统功能的封装内。它通过对数字、射频、光学、微机电系统的协同设计和制造,提供几乎所有的系统功能,是在SiP以上更高层次的集成,也属于广义的封装集成领域。

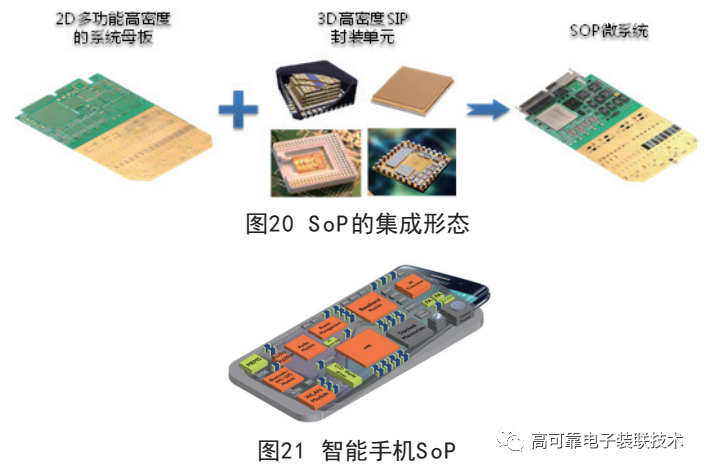

如图20所示,SoP的基本集成形态是2.5D的板级集成,是在2D的多功能高密度系统母板上集成3D的高密度封装单元,最终形成一个具有系统功能的板级微系统。在消费电子领域,智能手机的核心功能就是通过SoP的形式集成实现的(如图21所示)。

SoP集成有四项关键技术,分别是系统母板、高密度混合信号多工艺跨尺度异构集成与互连、集成可靠性与多层级热管理。

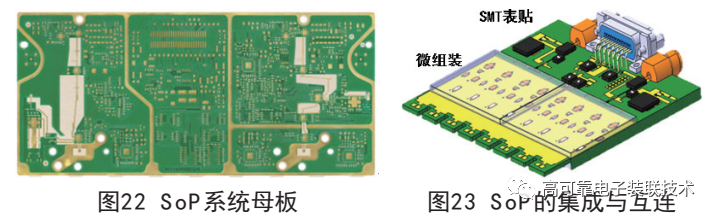

如图22所示,系统母板是整个SoP微系统提升集成密度的基础和核心。在系统母板内部嵌入射频、数字、光等所需的高质量信号传输,以替代大量线缆,大幅缩小体积重量;嵌入阻容、功分、滤波等无源元件,以替代大量分立无源元件,大幅节省平面面积,用于有源芯片的集成;嵌入散热结构,以替代部分分立散热结构,降低体积质量。

如图23所示,SoP微系统具有基本完整的系统功能,需将各类异构SiP封装或元器件在SoP主板上组装集成并实现高质量信号互连。集成互连的信号包括数字、模拟、射频、光等复杂信号;集成工艺包括正装集成、引线键合、倒装集成、SMT和光电集成等;集成尺度从10 μm到mm跨过至少两个量级。因此,高密度混合信号多工艺、跨尺度异构集成与互连工艺兼容性是核心问题。

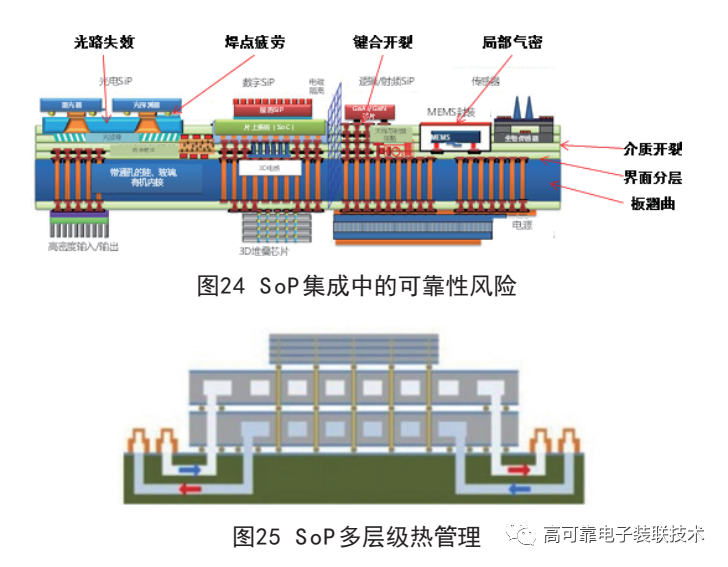

如图24所示,SoP主板与SiP封装相比尺寸大、密度高、材料体系多样、集成要素种类数量多、工艺过程复杂,系统可靠性保障难度明显增加,需要更加详细精确的可靠性设计与验证。

SoP系统集成密度大幅提升,带来热耗的大幅增加,系统散热压力剧增,需建立芯片到SiP封装到SoP微系统的全套多层级热管理体系(如图25所示)。传统主要通过热传导的散热方式将可能不再适用,需要引入微流道、微热管、微喷流、相变散热等新型散热手段。

3 结论

微系统技术是突破摩尔定律极限的重要解决途径之一,当前已进入“百花齐放、百家争鸣”的高速发展阶段。微系统的集成实现途径有SoC、SiP、SoP三个层级,其中SiP和SoP以其灵活性和成本优势成为近期最具应用前景的微系统集成技术,本文浅析了SiP和SoP的技术内涵、集成形态以及关键技术,为微系统集成实现提供参考。

参考文献

[1] 汤晓英.微系统技术发展和应用[J].现代雷达,2016,38(12):45-50.

[2] RADOJCICR. More-than-Moore 2.5D and 3D SiP integration[M].Berlin, GER: SpringerPublishing Company, 2017.

[3] TUMMALA RR, SWAMINATHAN M. Introduction to system-on package (SOP): Miniaturization ofthe entire system[M]. NYC, USA:Mc Graw-Hill Companies, Inc. 2008.

-

SiP

+关注

关注

5文章

501浏览量

105314 -

SOP

+关注

关注

0文章

92浏览量

27513 -

微系统

+关注

关注

1文章

31浏览量

10174

发布评论请先 登录

相关推荐

一文看懂SiP封装技术

SiP(系统级封装)技术的应用与发展趋势

SIP(封装系统),SIP(封装系统)是什么意思

基于ARM和FPGA的SiP通用微处理系统封装设计

SIP系统封装技术浅析

三点说明SIP与SOP的区别

什么是SiP技术 浅析SiP技术发展

微系统与SiP、SoP集成技术

微系统与SiP、SoP集成技术

评论