5.2流自适应

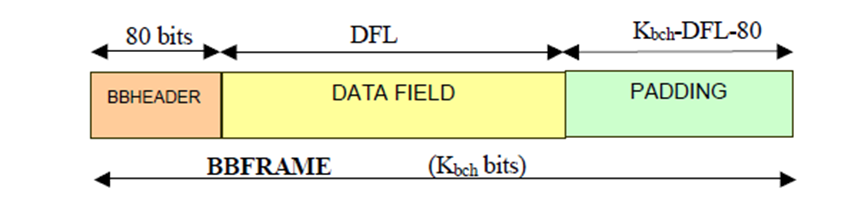

流自适应(见图1和图4)提供填充以完成定长(Kbch bit)的BBFRAME和加扰。Kbch取决于FEC码率,如表5所示。当可用于传输的用户数据不足以完全填充BBFRAME时,或者当必须在BBFRAME中分配整数个UP时,可以应用填充。

输入流应该是一个BBHEADER后面跟着一个DATA FIELD。输出流应该是一个BBFRAME。

图4:流适配器输出处的BBFRAME格式

5.2.1 填充

(Kbch-DFL-80)个零bit应附加在DATA字段之后。产生的BBFRAME应具有Kbch位的恒定长度。对于广播服务应用,DFL = Kbch -80,因此不应用填充。

5.2.2基带加扰

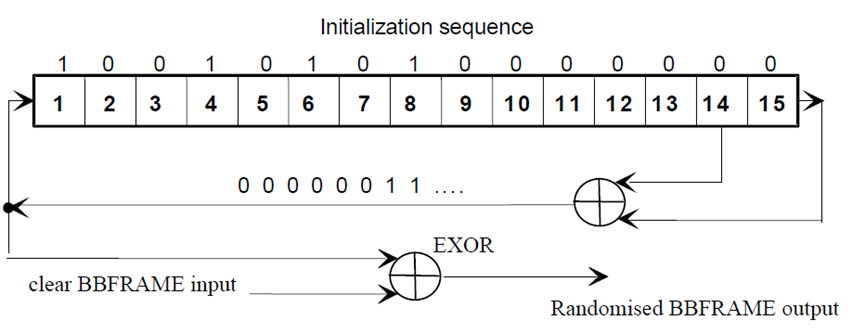

完整的BBFRAME将被随机化。随机化顺序应与BBFRAME同步,从MSB开始,以Kbch bit后结束。

加扰序列由图5的反馈移位寄存器产生。伪随机二进制序列(PRBS)发生器的多项式应为:

将序列(100101010000000)装入PRBS寄存器,如图5所示,应在每个BBFRAME开始时启动。

图5:PRBS编码器的可能实现

5.3FEC编码

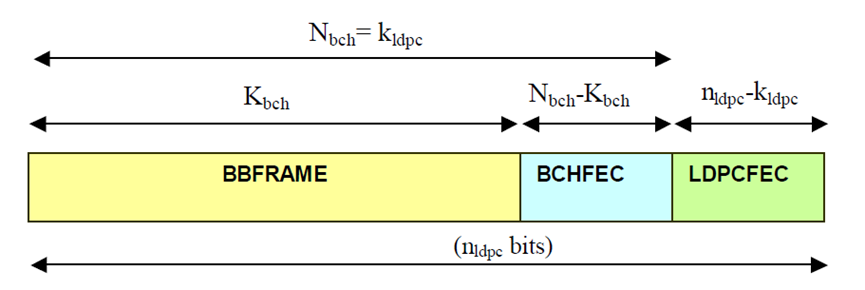

该子系统应执行外码(BCH)、内码(LDPC)和比特交织。由输入流BBFRAME和输出流FECFRAME组成。

每个BBFRAME (比特)由FEC编码子系统处理,生成一个FECFRAME (比特)。系统BCH外码的奇偶校验位(BCHFEC)应附加在BBFRAME字段之后,内部LDPC编码器的奇偶校验位(LDPCFEC)应附加在BCHFEC字段之后,如图6所示。

图6:比特交织前的数据格式(常规FECFRAME的nldpc = 64 800 bit,短FECFRAME的nldpc = 16 200 bit)

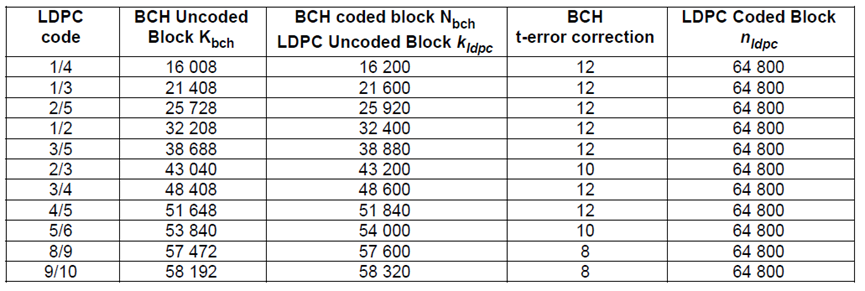

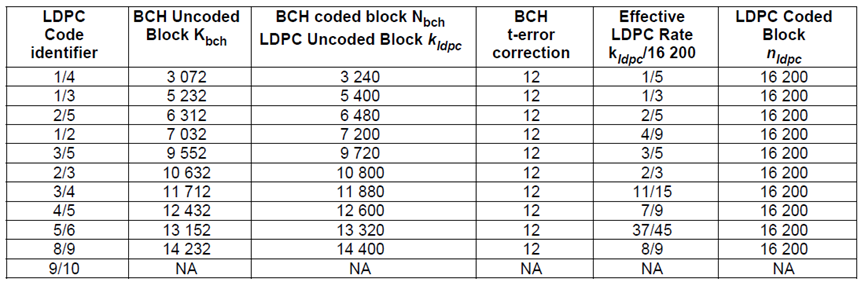

表5a给出了常规FECFRAME (= 64 800 bits)的FEC编码参数,表5b给出了短FECFRAME (= 16 200 bits)的FEC编码参数。

表5a:编码参数(常规FECFRAME nldpc = 64800)

表5b:编码参数(短FECFRAME nldpc = 16 200)

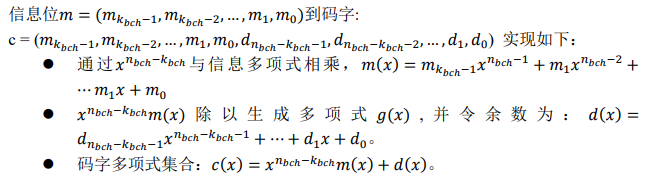

5.3.1 外码(BCH)

每个BBFRAME(Kbch)应应用t个纠错的 BCH (Nbch, Kbch)码以生成错误保护包。nldpc = 64 800的BCH代码参数见表5a, nldpc = 16 200的BCH代码参数见表5b。

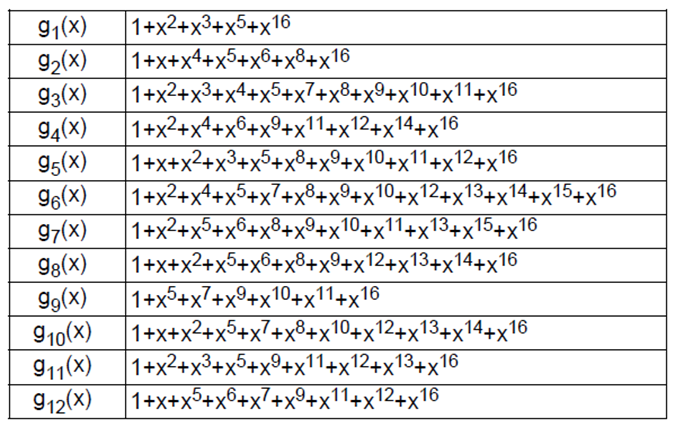

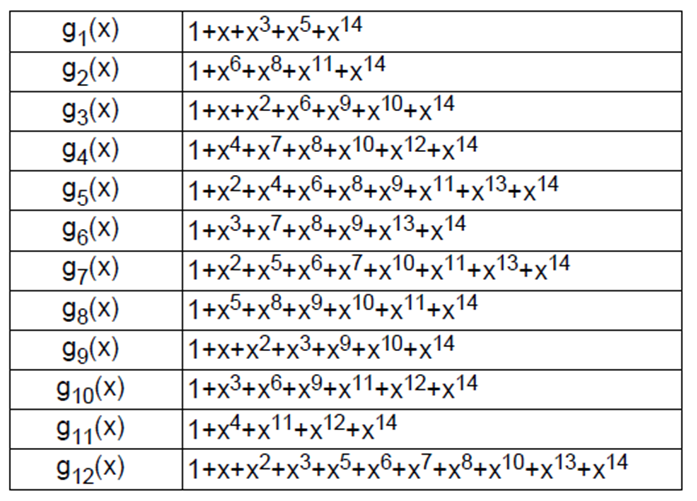

t个纠错BCH编码器的生成器多项式由表6a中nldpc = 64 800和表5b中nldpc = 16200的第一个t多项式相乘得到。

表6a: BCH多项式(对于常规FECFRAMEnldpc = 64 800)

表6b: BCH多项式(对于短FECFRAME nldpc = 16 200)

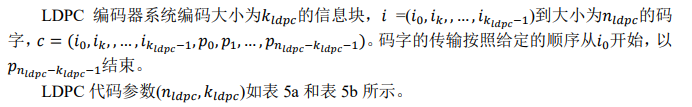

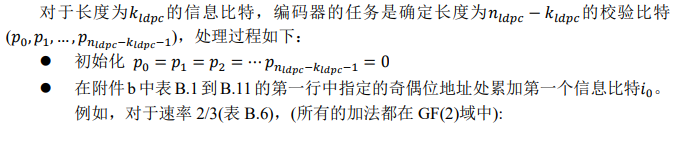

5.3.2 内码(LDPC)

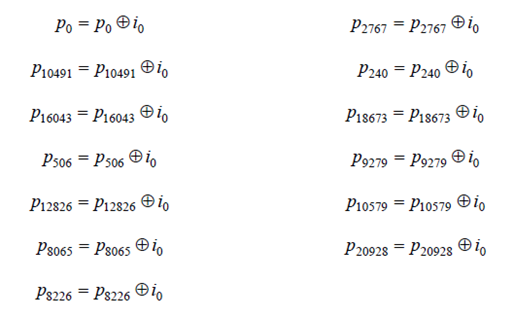

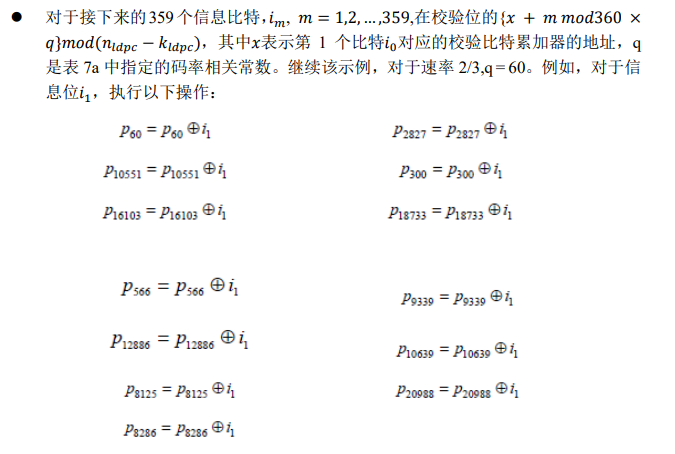

5.3.2.1 常规FECFRAME的内码

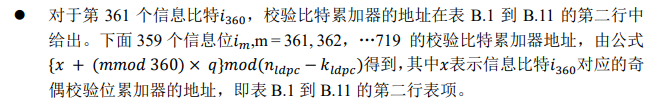

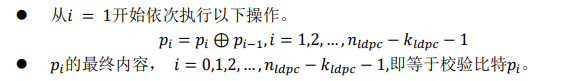

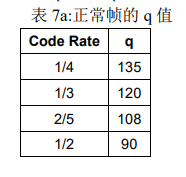

以类似的方式,对于每一组360个新信息比特,从表B.1到B.11中的新行用于查找校验位累加器的地址。

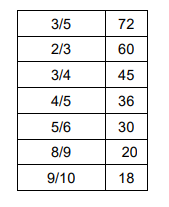

用完所有信息比特后,得到最终校验位如下:

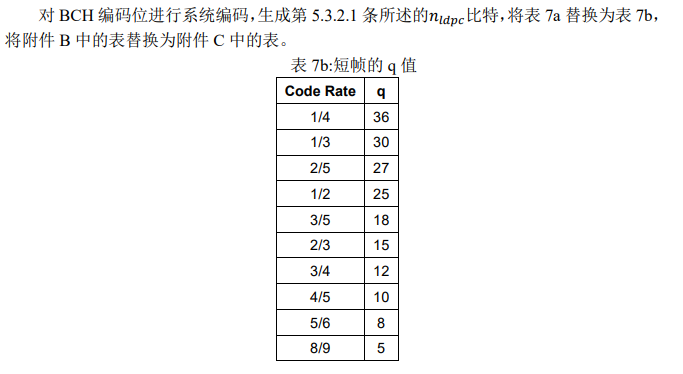

表7a:正常帧的q值

5.3.2.2 短FECFRAME的内码

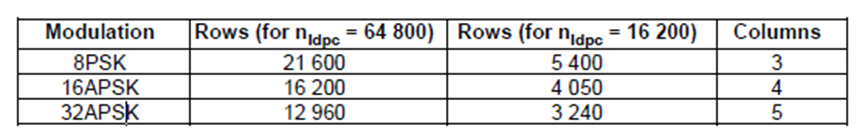

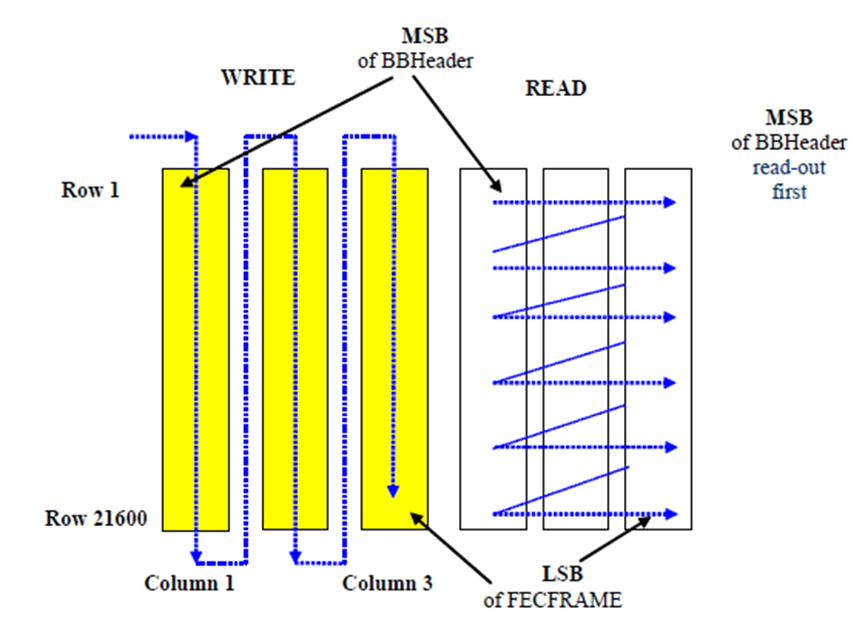

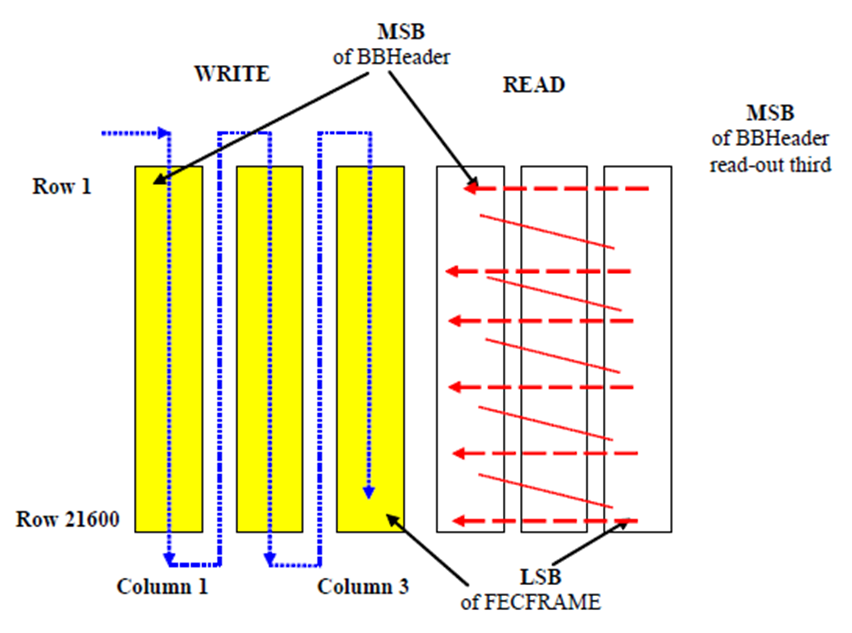

5.3.3 比特交织(仅适用于8PSK, 16APSK和32APSK)

对于8PSK、16APSK和32APSK调制格式,LDPC编码器的输出应使用块交织器进行位交织。数据按列顺序写入交织器,按行顺序读出(首先读出BBHEADER的MSB,但在8PSK速率3/5的情况下,BBHEADER的MSB在第三读出),如图7和图8所示。

每个调制格式的块交织器的配置如表8所示。

表8:位交织器结构

图7:8PSK和正常FECFRAME长度的比特交织方案(除3/5外的所有速率)

图8:8PSK和正常FECFRAME长度的比特交织方案(速率仅为3/5)

审核编辑:刘清

-

发生器

+关注

关注

4文章

1432浏览量

64684 -

移位寄存器

+关注

关注

4文章

352浏览量

23434 -

FEC

+关注

关注

0文章

41浏览量

14289 -

PRBS

+关注

关注

0文章

10浏览量

3058

原文标题:DVB-S2标准协议:流自适应与FEC编码

文章出处:【微信号:FPGA算法工程师,微信公众号:FPGA算法工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

国内外主流DVB-S ,DVB-S2及ISDBT 方案,功能

N5182A信号发生器能生成dvb-s2信号吗?

采用MSD7S45的海外DVB-S2高清机顶盒方案

基于MSD7S01的DVB-S2机顶盒方案

DVB-S/DVB-S2信号发生器 (DVB-S/S2 Si

基于人工神经网络的DVB-S2数字信号调制模式识别

基于PXA270 和STi710x 的双CPU DVB-S2

基于PXA270和STi710x的双CPU DVB-S2标准

澜起科技发布DVB-S2解调芯片M88DS3103

SUNNISKY TS2000-S2 DVB-S2卫星数字信号处理器

基于网络编码的速率自适应协作介质访问控制协议

基于FEC技术和QPSK调制技术实现DVB-S芯片的帧格式转换设计

DVB-S2标准协议:传输系统描述

DVB-S2标准协议:模式自适应

DVB-S2标准协议:流自适应与FEC编码简析

DVB-S2标准协议:流自适应与FEC编码简析

评论