MIPI Dsi的使用相比于CSI多了一些寄存器控制,生成的example直接仿真是可以的,但是修改了参数,一些参数也要做相应的调整。这里我们来做个简单总结 。

(1)BANK电压要配置成1.2V

(2)输出要接相应bank的REF_RES管脚。

(3)修改配置参数

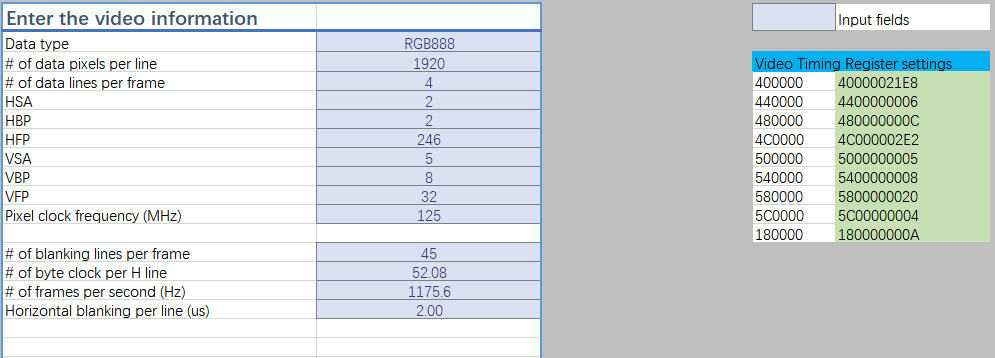

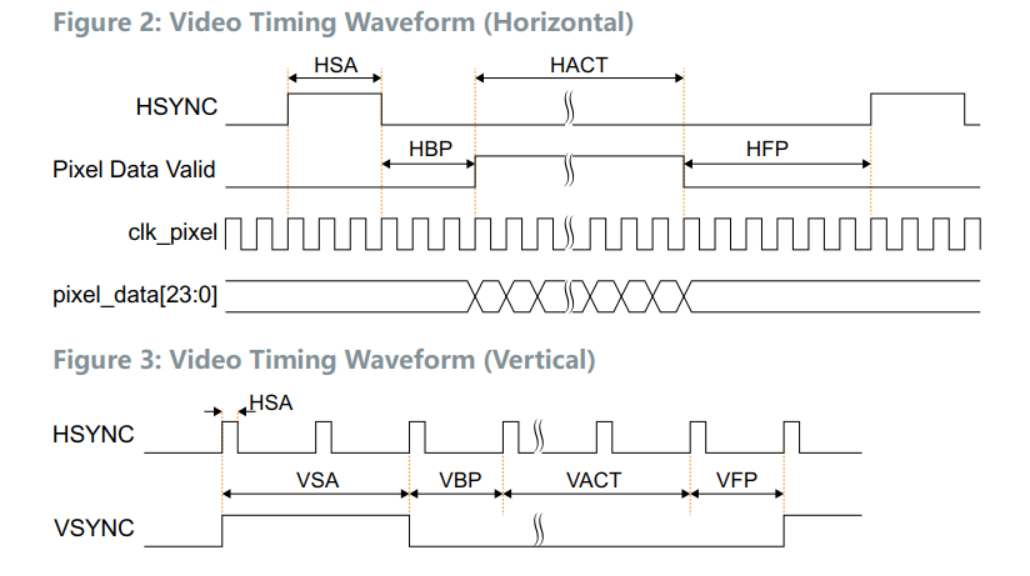

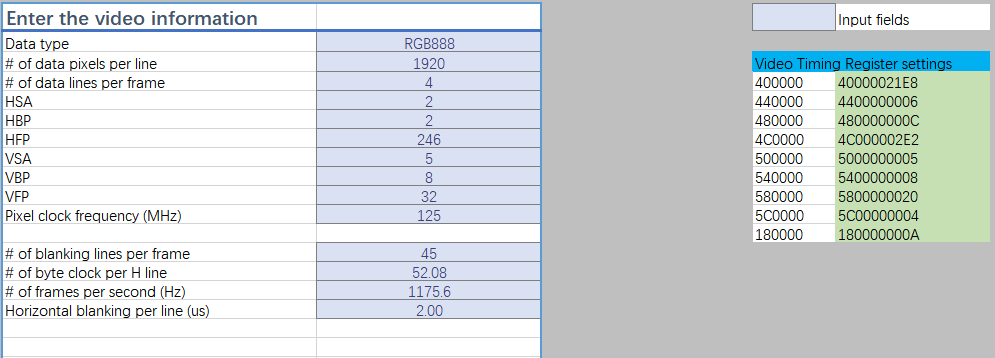

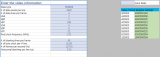

视频格式如下,可能根据实际的需要进行修改。

parameter MAX_HRES = 16'd1920; parameter MAX_VRES = 12'd4; parameter HSP = 10'd2; parameter HBP = 10'd2; parameter HFP = 10'd246; parameter VSP = 6'd5; parameter VBP = 6'd8; parameter VFP = 6'd32;

修改了参数要在Tianium-mipi-utility文件中验证确保文件没有错误提示。

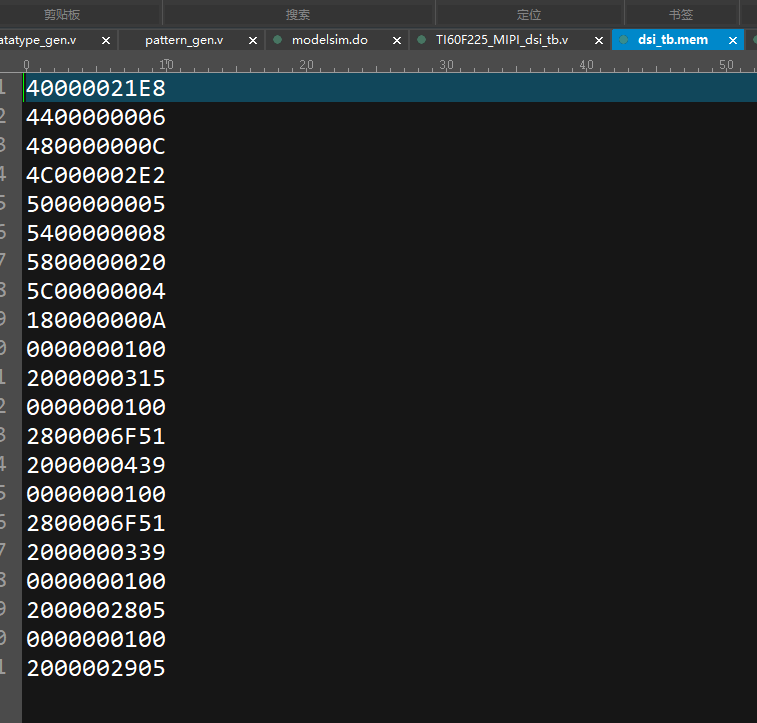

另外要把Tianium-mipi-utility文件中input fields中的信息替换dsi_tb.mem中的相应信息。这是IP需要的视频格式信息。

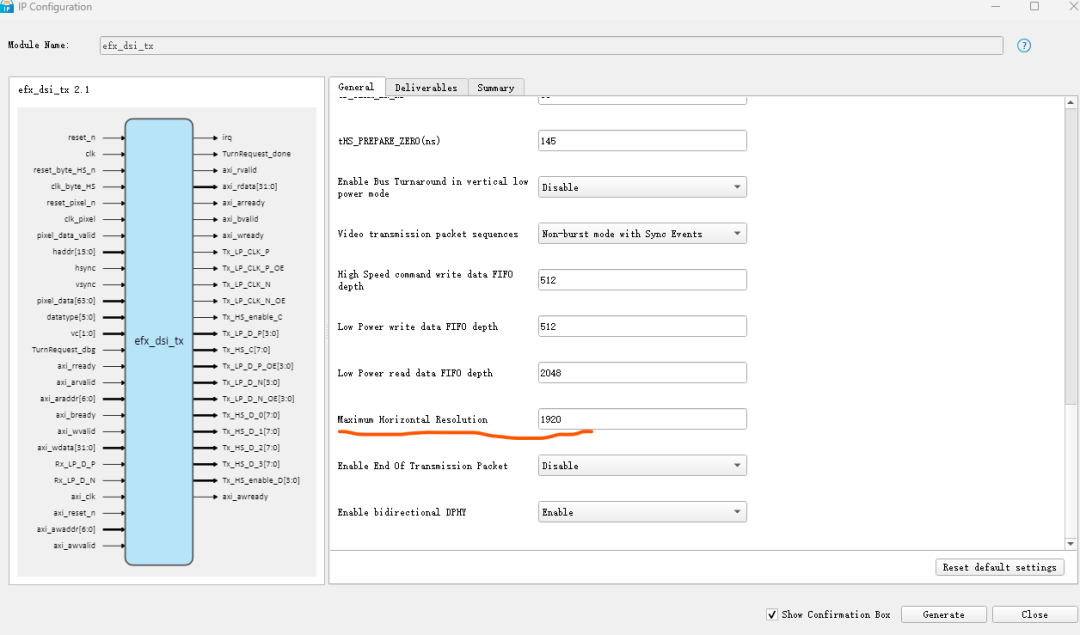

(4)另外还在注意在IP中修改所支持的Maximum Horizontal Resolution信息,确认我们测试的行长度小于等于该值。

(4)另外还在注意在IP中修改所支持的Maximum Horizontal Resolution信息,确认我们测试的行长度小于等于该值。

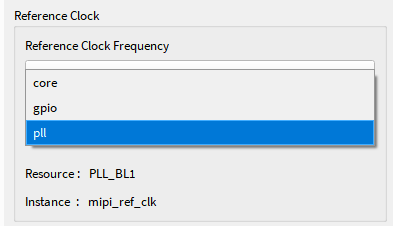

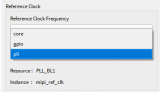

(5)注意修改相应的时钟

在下面,i_pclk是单像素的时钟。o_pclk对应MIPI接口的像素时钟。

i_sys_clk是MIPI AXI接口的配置时钟。i_mipi_tx_pclk是MIPI发送8位HS数据的并行时钟。

在使用中可能根据设置参数修改i_pclk,o_pclk和i_mipi_tx_pclk;一般不用修改i_sys_clk。

//video生成时钟是125M initial begin i_pclk <= 1'b1; forever #4.00 i_pclk <= ~i_pclk; end //转换成MIPI接口的pixel clock是62.5M initial begin o_pclk <= 1'b1; forever #8.00 o_pclk <= ~o_pclk; end //MIPI配置接口时钟是50M initial begin i_sys_clk <= 1'b1; forever #10 i_sys_clk <= ~i_sys_clk; end //MIPI时是100M initial begin mipi_clk <= 1'b1; forever #5 mipi_clk <= ~mipi_clk; end //数据速率是1000M initial begin i_mipi_tx_pclk <= 1'b1; forever #4 i_mipi_tx_pclk <= ~i_mipi_tx_pclk; end

(6)所设置的参数既要在Tianium-mipi-utility在评估通过,还要满足公式

PIX_CLK_MHZ < (DATARATE_MPBS * NUM_DATA_LANE) / PACK_BIT

1)这里的PIX_CLK_MHZ就是指MIPI IP接口的pixel_clk

2)DATARATE_MPBS是指MIPI的数据速率,并非video的带宽。

3)NUM_DATA_LANE是指传输所用的lane数

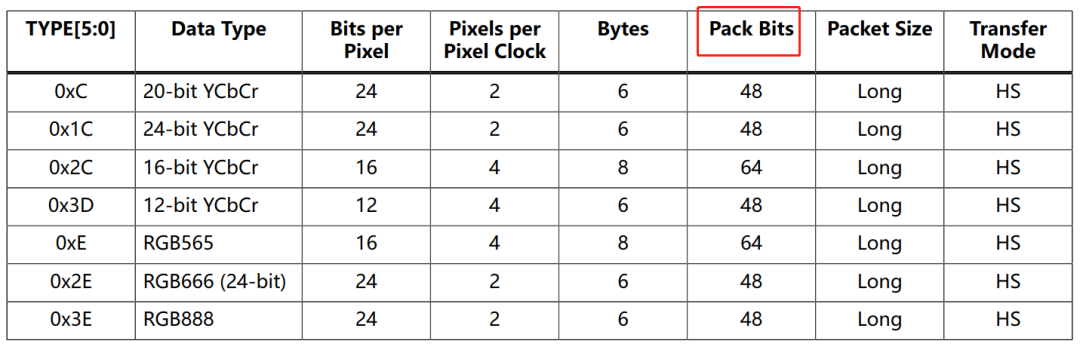

4) PACK_BIT如下,详细信息请参考MIPI DSI ds。

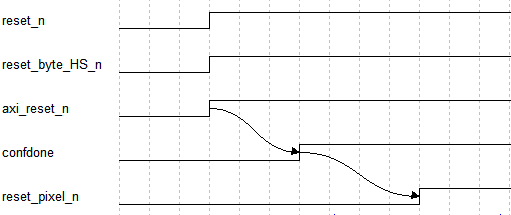

(7)复位处理

复位timing

关于DSI_TX复位处理:

1)reset_n,reset_byte_HS_n和axi_reset_n先释放;

2)等待panel_config的o_confdone拉高,也就是panel_config配置完成

3)通过confdone拉高来释放video_stream的复位

4)confdone可以用于reset_pixel_n,也可以通过video_stream的输出的vs信号,在vs为blank时释放复位。

parameterFRAME_NUM = 5 reg vs_r; reg [10:0] r_vs_cnt; wire neg_vs; always@(negedge sys_rst_n or posedge i_sysclk_div_2) begin if(!sys_rst_n) vs_r <= 1'b0; else vs_r <= vs; end assign neg_vs = {vs_r,vs} == 2'b10; always@(negedge sys_rst_n or posedge i_sysclk_div_2) begin if( !sys_rst_n ) r_vs_cnt <= 16'b0; else if (neg_vs && r_vs_cnt <= FRAME_NUM ) r_vs_cnt <= r_vs_cnt + 1'b1; end always@(negedge sys_rst_n or posedge i_sysclk_div_2) begin if (!sys_rst_n) reset_pixel_n <= 1'b0; else if (neg_vs && r_vs_cnt == FRAME_NUM-1 ) // reset_pixel_n <= 1'b1; end

(8) MIPI IP接口的timing时序要求如下:

(9)video接口数据类型格式

视频格式的顺序请参考AN015。

审核编辑:汤梓红

-

寄存器

+关注

关注

31文章

5343浏览量

120401 -

仿真

+关注

关注

50文章

4085浏览量

133636 -

移植

+关注

关注

1文章

379浏览量

28135 -

MIPI

+关注

关注

11文章

310浏览量

48634 -

DSI

+关注

关注

0文章

51浏览量

42357

原文标题:MIPI dsi TX移植注意事项 - update3

文章出处:【微信号:gh_ea2445df5d2a,微信公众号:FPGA及视频处理】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

1.5G MIPI dsi TX移植注意事项及demo - update8

MIPI解决方案 ICN6202:MIPI DSI转LVDS转换芯片

MIPI DSI 转 LVDS 单路, ZA7783

ICN6202 MIPI DSI转LVDS的桥接芯片

MIPI dsi TX移植注意事项

MIPI dsi TX移植注意事项 - update7

MIPI dsi TX移植注意事项

MIPI dsi TX移植注意事项

评论