编 者 按

当在SpinalHDL中调用别人的RTL代码时,需要采用BlackBox进行封装。对于大多数场景,想必小伙伴们都已轻车熟路。今天着重来看下当RTL代码的接口中存在数组形式的接口时如何处理。

合并数组和非合并数组 在开始之前先了解两个概念:合并数组与非合并数组。在SystemVerilog中,关于可综合的数组存在两种形式:

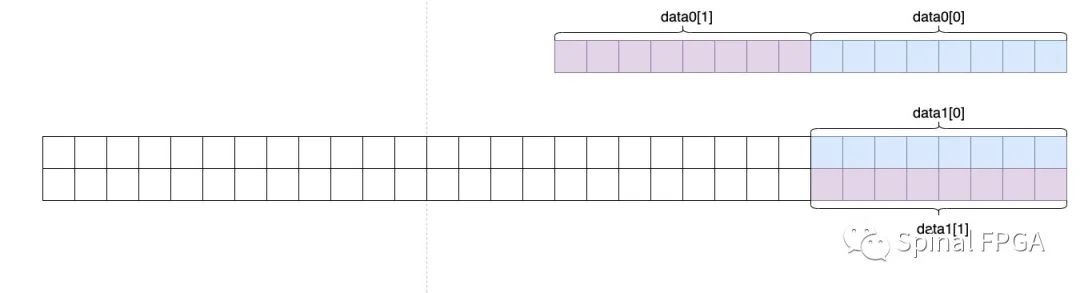

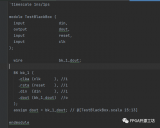

wire [1:0][7:0] data0; //合并数组 wire [7:0] data1[1:0]; //非合并数组 在仿真方面,合并数组是紧密排列的,而非合并数组则是按照内存对齐的形式进行排列(电路综合中则无需考虑):

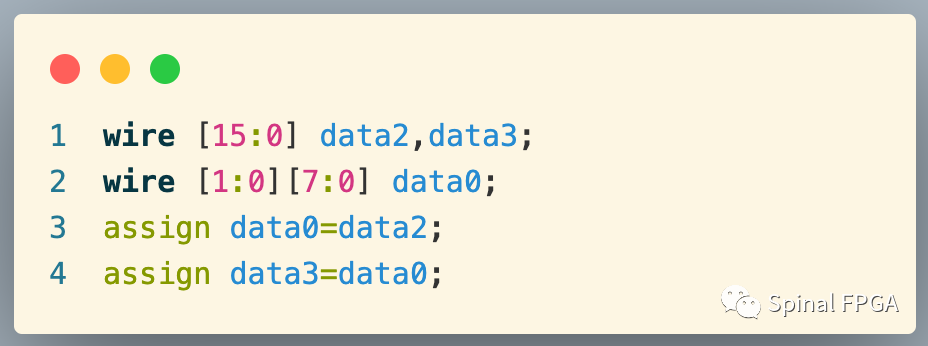

相应的,合并数组则可以作为一个整体进行赋值,而非合并数组则不可以:

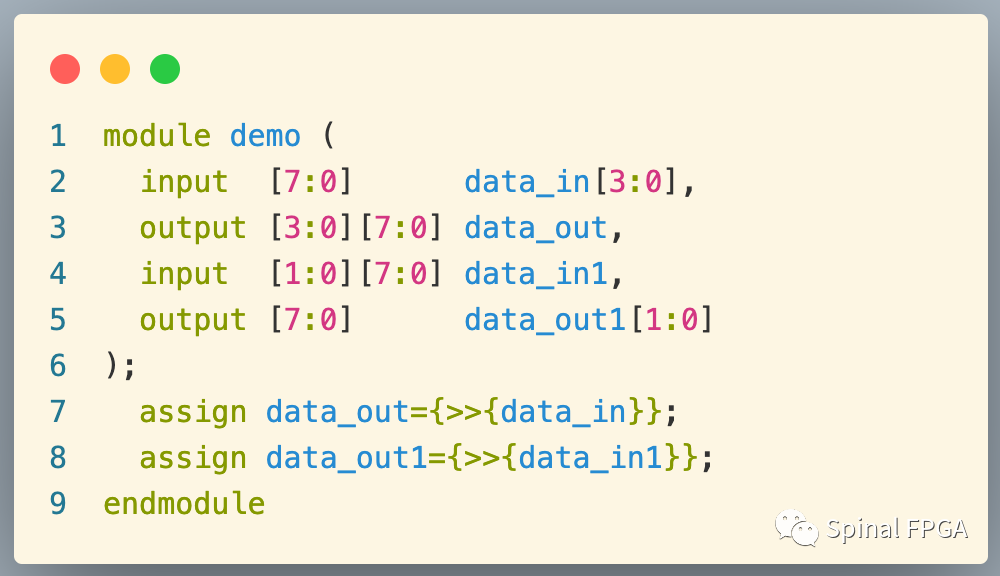

而合并数组与非合并数组,则可以通过SystemVerilog中所提供的流操作符进行相互转换处理(是可以综合的):

》BlackBox封装

在了解了上面的背景知识之后,再来看如何这种数组类场景如何封装至BlackBox。两条规则:

1、BlackBox封装针对数组类接口仅能支持合并数组类型。

2、当接口中存在非合并数组接口时则需手动封装一层通过流操作符将非合并数组转换为合并数组。

基于上面的规则,可以进行数组接口的BlackBox封装。

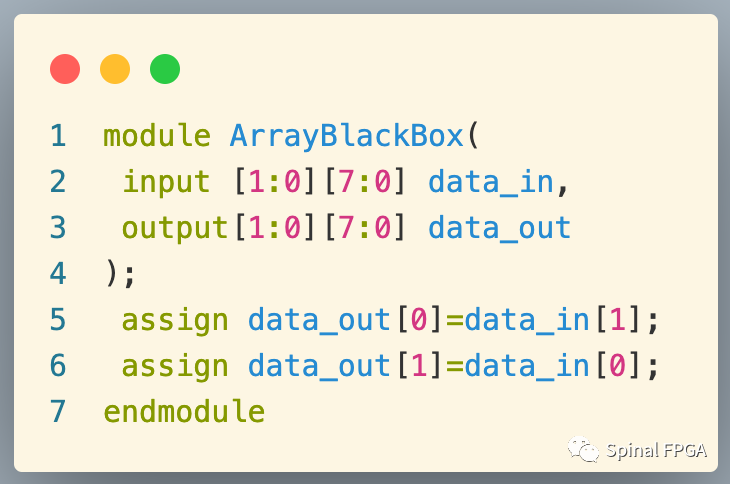

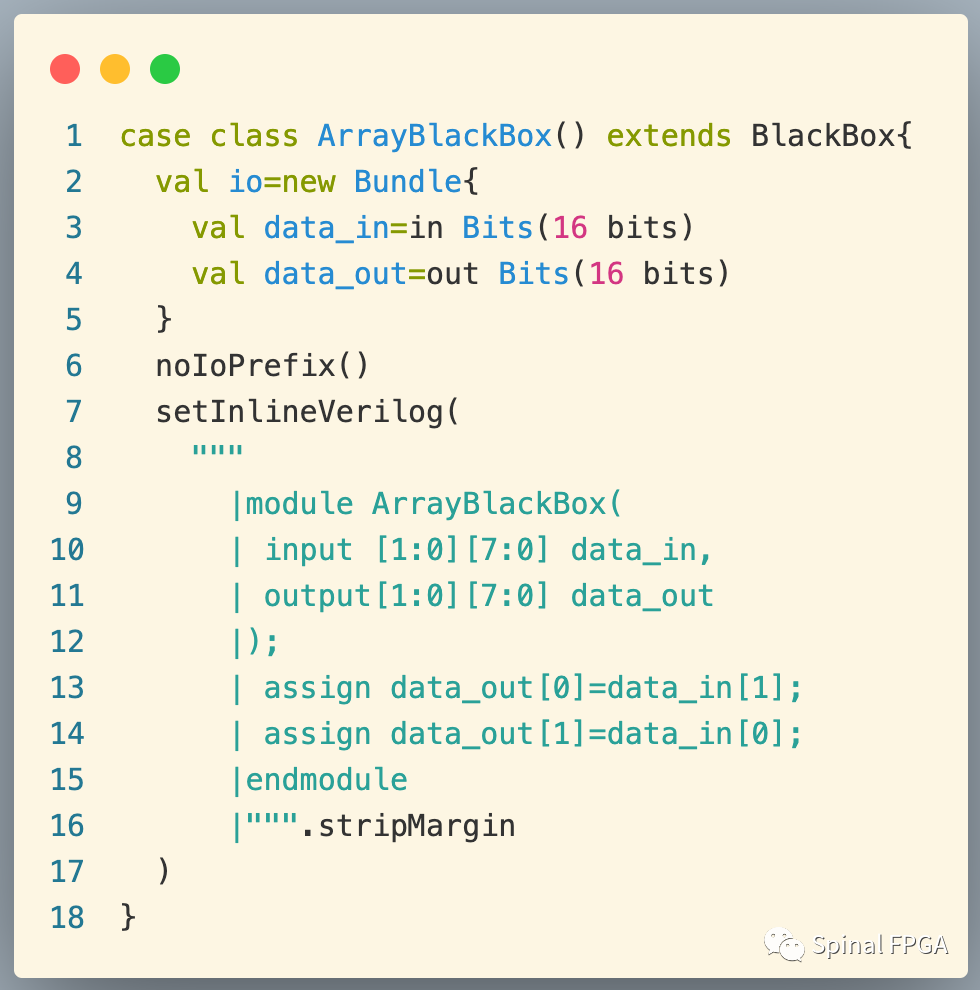

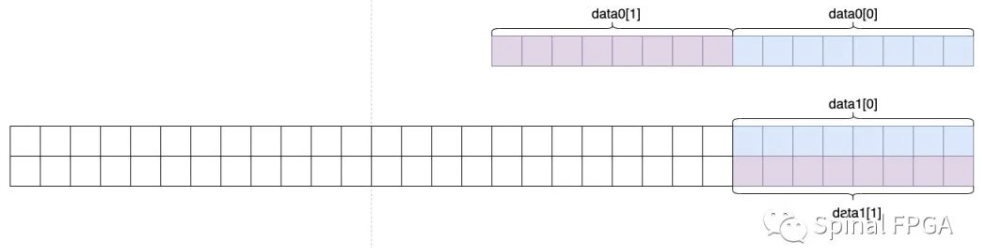

看下面的RTL代码示例:

该模块输入,输出均为一个合并数组,实现功能为两个元素的数据交换。我们在进行封装BlackBox时可采用下面的封装形式:

这里我们在BlackBox中定义接口时将合并数组data_in,data_out均定义为Bits类型,宽度为合并数组中所有元素的位宽总和(2*8).

(这里面的setInlineVerilog也可不写,主要是懒得再创建一个SV文件了。关于这部分功能可参见《彩——看blackBox的inline功能》)

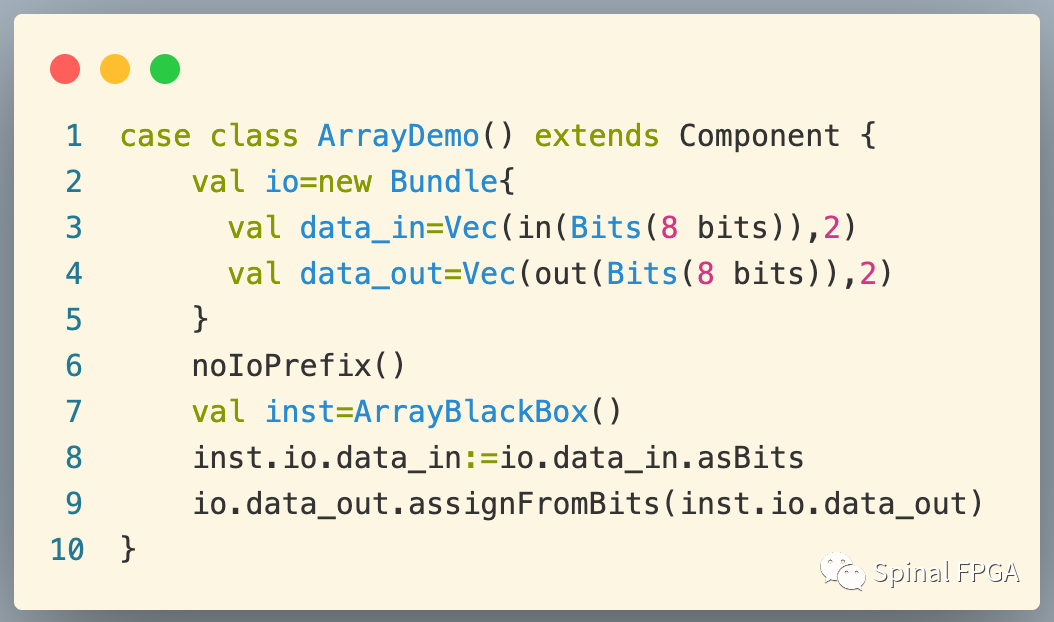

在进行调用时就可以和其他调用没有区别了:

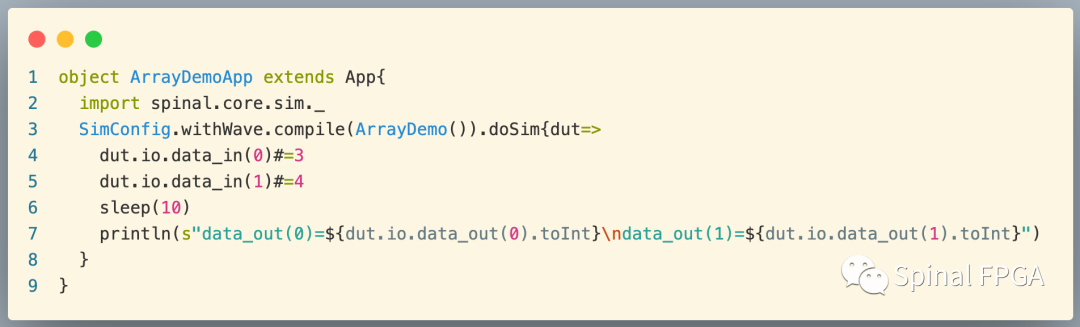

进行仿真:

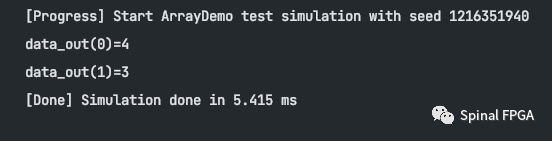

结果非常符合预期:

审核编辑:汤梓红

-

接口

+关注

关注

33文章

8823浏览量

152646 -

封装

+关注

关注

128文章

8208浏览量

144063 -

RTL

+关注

关注

1文章

387浏览量

60307 -

代码

+关注

关注

30文章

4864浏览量

69749 -

数组

+关注

关注

1文章

419浏览量

26185

原文标题:惊!原来SpinalHDL中BlackBox封装数组接口如此简单

文章出处:【微信号:Spinal FPGA,微信公众号:Spinal FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

在SpinalHDL里实现优雅的添加待跟踪波形信号

在SpinalHDL的设计中集成现有RTL设计(IP)的渠道——BlackBox

关于SpinalHDL中的验证覆盖率收集简单说明

聊一聊SpinalHDL 1.6.1引入的blackbox inline功能

聊聊SpinalHDL中的FIFO

SpinalHDL是如何让仿真跑起来的

记录一个在使用BlackBox中parameter踩到的坑

SpinalHDL BlackBox时钟与复位

当RTL代码的接口中存在数组形式的接口时如何处理?

Verilog代码封装后门访问

原来SpinalHDL中BlackBox封装数组接口如此简单

原来SpinalHDL中BlackBox封装数组接口如此简单

评论