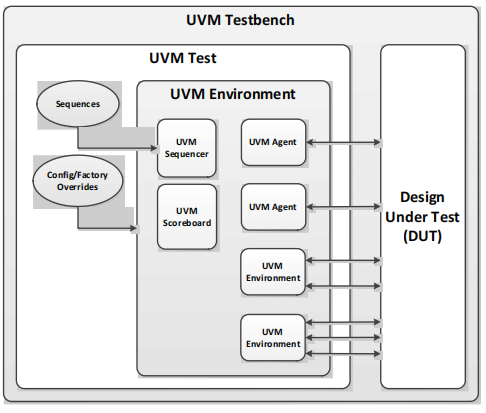

UVM类库提供了通用的代码功能,如component hierarchy、transaction levelmodel(TLM),configuration database等等,使用户能够创建任何类型的Testbench架构。

上图是一个非常通用的testbench架构,并不能够表示所有类型的testbench架构。

UVM Testbench

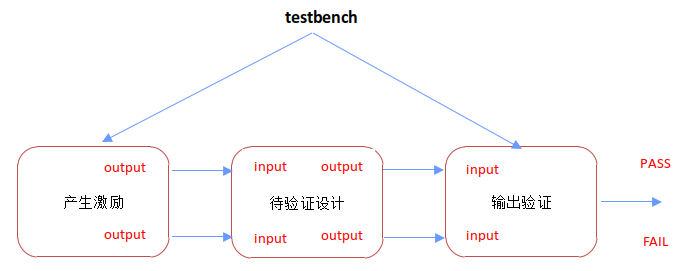

UVMTestbench通常实例化Design under Test (DUT)module和UVM Test class,并进行连接。

UVMTest是在运行时动态实例化的,这使得UVM Testbench可以只编译一次,然后运行不同的测试用例。

1.1.2 UVM Test

UVMTest是UVM Testbench中的顶层组件。UVM Test 通常会执行三个主要功能:

实例化top-level验证环境

配置验证环境(通过factory overrides或configuration database)

通过调用UVM Sequences来施加激励到DUT

通常,会有一个实例化UVM Environment的base UVM Test,然后其他的Test将扩展这个base test,以不同的方式配置验证环境或选择运行不同的sequences 。

1.1.3 UVM Environment

UVMEnvironment是一个分层验证组件,它将相互关联的其他验证组件组合在一起。通常在UVM Environment中实例化的典型组件是UVM Agents, UVM Scoreboards,以及其他UVM Environments。顶层UVM Environment封装了针对DUT的所有验证组件。

例如:在芯片(SoC)UVM Environment上,你会找到对应于各个IP的UVM Environment(例如PCIe Environment, USB Environment, Memory Controller Environment等等)。有时这些IP Environments被组合到Cluster Environments中(例如IO Environment, Processor Environment等等),最终在顶层SoC Environment中组合在一起。

1.1.4 UVM Scoreboard

UVMScoreboard的主要功能是检查某个DUT的行为。UVM Scoreboard通常通过UVM Agentanalysis ports接收DUT的输入和输出事务,通过参考模型来产生预期结果,然后和实际输出进行比较。

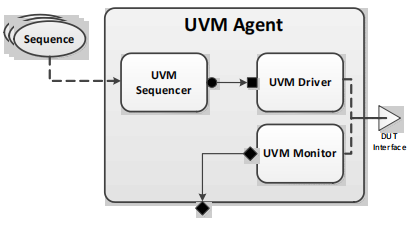

1.1.5 UVM Agent

UVM Agent是一个分层组件,它将其他和DUT接口交互的验证组件组合在一起。一个典型的UVM Agent包括一个UVM Sequencer管理激励,一个UVM Driver将激励施加到DUT接口和一个UVM Monitor监测DUT接口。

UVM Agents也可能包括其他组件,如coverage collectors,protocol checkers等等。

UVM Agent可能工作在active mode(能够产生激励),或者工作在passive mode(只监测接口而不驱动)。

1.1.6 UVM Sequencer

UVMSequencer是一个从多个激励sequences中控制事务流的仲裁器。更具体地说,UVM Sequencer控制着一个或多个UVM Sequences。

1.1.7 UVM Sequence

UVMSequence是一个包含产生激励行为的对象,并不是验证组件层次结构中的一部分。UVM Sequences同样也可以是分层的,可以由一个sequence(parent sequence)调用另一个sequence(child sequence)。

每个UVMSequence都被绑定到一个UVM Sequencer上。多个UVM Sequence可以绑定到相同的UVM Sequencer。

1.1.8 UVM Driver

UVMDriver从UVM Sequencer中接收UVM Sequence Item,并在DUT接口上驱动。因此,UVM Driver将transaction-level激励转换为pin-level激励。

1.1.9 UVM Monitor

UVMMonitor对DUT接口进行采样,并发送到UVM的其他验证组件中继续下一步的analysis行为。因此,UVM Driver将pin-level转换transaction-level。UVM Monitor有一个TLM analysis port来广播所监测到的创建的transactions。

UVM Monitor可以在内部对产生的事务执行一些处理(如覆盖率收集、检查、日志记录等)或者可以将这些任务交给连接到monitoranalysis port的其他验证组件。

审核编辑:汤梓红

-

芯片

+关注

关注

463文章

54411浏览量

469150 -

soc

+关注

关注

40文章

4622浏览量

230148 -

UVM

+关注

关注

0文章

183浏览量

20095 -

代码

+关注

关注

30文章

4976浏览量

74369

原文标题:典型的UVM Testbench架构

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

数字IC验证之“什么是UVM”“UVM的特点”“UVM提供哪些资源”(2)连载中...

数字IC验证之“典型的UVM平台结构”(3)连载中...

什么是uvm?uvm的特点有哪些呢

谈谈UVM中的uvm_info打印

我的第一个UVM代码——Hello world

参数化UVM IP验证环境(上)

testbench怎么写_testbench经典教程VHDL

数字IC验证之“典型的UVM平台结构”(3)连载中...

UVM中uvm_config_db机制背后的大功臣

一文详解UVM设计模式

编写高效Testbench的指南和示例

典型的UVM Testbench架构

典型的UVM Testbench架构

评论