我们知道在车载芯片的数字实现中,常用的安全机制有安全寄存器(Safety Register),所以识别出关键路径上失效风险高的寄存器(也就是热点寄存器)就非常重要,需要EDA工具重点发力识别,并把识别出的热点寄存器替换为安全寄存器。

常用的TMR、DMR安全寄存器的原理如下:

• 三模冗余寄存器(TMR: Triple-Modular Redundancy):将热点寄存器复制为三个寄存器、读取同一输入,并用多数表决投票逻辑对它们的输出进行投票,具备输出自动校正功能。

• 双模冗余寄存器(DMR: Dual-Modular Redundancy):将热点寄存器复制为两个寄存器、读取同一输入,使用比较逻辑对两者的输出进行比较,只检测错误,不进行自动校正。

尤其,数字后端设计中,安全寄存器的布局布线和时钟树需要特别设计。首先,同一组TMR寄存器或者DMR寄存器如何place ?其次,安全寄存器的时钟树如何设计?复位线如何设计?答案参见全栈芯片工程师知识星球。

安全寄存器是一种硬件冗余方法,用于预防和缓解单粒子翻转(SEU:Single Event Upset)的影响。单粒子翻转是指高能放射粒子撞击电路中的敏感节点,造成时序电路逻辑错误翻转引起的芯片功能错误。车规芯片的数字后端设计,对EDA工具要求极高,通过定义安全寄存器规则(Safety Register Rule)让后端工具自动实现。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5317浏览量

120002 -

DMR

+关注

关注

1文章

32浏览量

13573 -

EDA工具

+关注

关注

4文章

264浏览量

31712 -

时钟树

+关注

关注

0文章

53浏览量

10732

原文标题:车规芯片-安全寄存器的布局设计

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

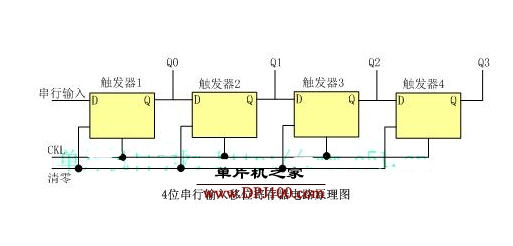

移位寄存器的原理

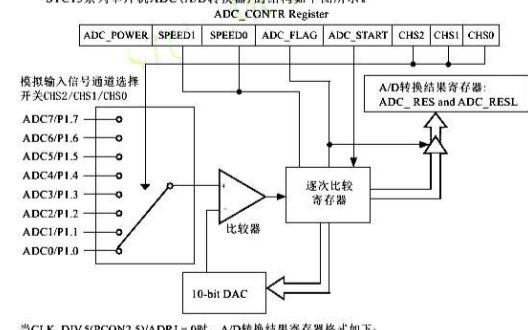

芯片与寄存器

GPIO寄存器

车载芯片安全寄存器的布局设计

车载芯片安全寄存器的布局设计

评论