SystemVerilog中,initial begin-end是仿真开始就会执行的代码块。比如UVM的test入口函数run_test,一般就是在initial begin-end中调用。还有一些tb会在initial begin-end中使用fork join_none,用于创建一些仿真中的后台进程,如时钟产生,后门驱动等。

那么initial begin-end真的是仿真最早执行的吗?

如果是消耗仿真时间的,那initial begin-end中的代码是仿真开始最早执行的。如果不消耗仿真时间,那还有一种代码会早于initial begin-end执行。

static property/function !!!

static类型变量,无论是全局变量,还是class内部参数,会在仿真开始前确定其初始值。如果该初始值是一个由static类型的function返回值决定,则该function的代码会在initial begin-end前执行完毕。

可以参考如下的测试:

importuvm_pkg::*; `include"uvm_macros.svh" classstatic_wrapper; staticbitfst_flag=cls_func_before_initial("static_wrapper:fst_flag"); staticbitsnd_dlag=cls_func_before_initial("static_wrapper:snd_flag"); staticfunctionbitcls_func_before_initial(stringx); intcnt; cnt++; $display("cls_func_before_initial:",x,"@",$time); return1; endfunction endclass staticfunctionbitglb_func_before_initial(stringx); intcnt; cnt++; $display("glb_func_before_initial:",x,"@",$time); return1; endfunction classtestextendsuvm_test; `uvm_component_utils(test) functionnew(stringname="test",uvm_componentparent=null); super.new(name,parent); endfunction virtualtaskmain_phase(uvm_phasephase); super.main_phase(phase); phase.raise_objection(this); uvm_top.print(); phase.drop_objection(this); endtask endclass programtb_top; staticbitthd_flag=glb_func_before_initial("thd_flag"); initialbegin $display("initialbegin...@",$time); run_test("test"); $display("initialend...@",$time); end endprogram

仿真结果如下:

cls_func_before_initial:static_wrapper:fst_flag@0 cls_func_before_initial:static_wrapper:snd_flag@0 glb_func_before_initial:thd_flag@0 initialbegin...@0 UVM_INFO@0:reporter[RNTST]Runningtesttest... ------------------------------------- NameTypeSizeValue -------------------------------------uvm_root-@172 uvm_test_toptest-@336 ------------------------------------- UVM_INFO/apps/vcsmx/vcs/S-2021.09//etc/uvm-1.2/src/base/uvm_report_server.svh(904)@0:reporter[UVM/REPORT/SERVER] ---UVMReportSummary--- **Reportcountsbyseverity UVM_INFO:2 UVM_WARNING:0 UVM_ERROR:0 UVM_FATAL:0 **Reportcountsbyid [RNTST]1 [UVM/RELNOTES]1 $finishcalledfromfile"/apps/vcsmx/vcs/S-2021.09//etc/uvm-1.2/src/base/uvm_root.svh",line527. $finishatsimulationtime0

可以看到cls_func_before_initial和glb_func_before_initial两个function都会在initial begin-end前执行。

上面的例子也可以看到,在run_test之后的代码块并不会执行,这是因为run_test执行结束后,UVM机制会直接调用$finish函数结束仿真。

其实在UVM中,已经利用了static变量的初始化这一特性。UVM的工厂模式中,使用uvm_component_utils/uvm_object_utils向工厂中注册组件时,就利用了这一特性。逐层展开uvm_component_utils宏时,可以看到如下的代码:

classuvm_component_registry#(typeT=uvm_component,stringTname="")extendsuvm_object_wrapper; //.... localstaticthis_typeme=get(); staticfunctionthis_typeget(); if(me==null)begin uvm_coreservice_tcs=uvm_coreservice_t::get(); uvm_factoryfactory=cs.get_factory(); me=new; factory.register(me); end returnme; endfunction //....

思路打开,利用static变量初始化这一特性,可以尝试更多的应用。

审核编辑:刘清

-

Verilog

+关注

关注

28文章

1352浏览量

110517 -

UVM

+关注

关注

0文章

182浏览量

19240

原文标题:initial begin-end真的是SystemVerilog 仿真最早执行的吗?

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

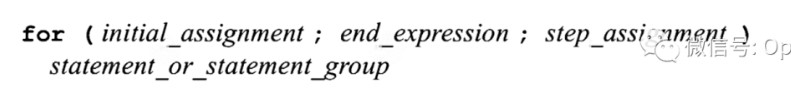

重点介绍所有综合编译器都支持的for和repeat循环

initial begin-end真的是仿真最早执行的吗?

initial begin-end真的是仿真最早执行的吗?

评论