随着后摩尔时代的到来, AI、5G、自动驾驶等众多热门应用不断涌现,芯片规模呈指数级增长,十亿门甚至几十亿门的芯片设计比比皆是,芯片规模越大、工艺节点越高,流片成本也是水涨船高。为了提高流片成功率,EDA验证成为高端芯片设计必不可少的环节,贯穿从设计到量产的全流程。验证在整个芯片开发过程中,投入时间最长、耗费资源最多,也面临着诸多技术挑战。如何解决大芯片的验证痛点,成为芯片设计公司的关注焦点。

一、EDA验证为何至关重要

如今芯片设计软件已走过了60多年的浩浩荡荡发展史,其过程是从辅助绘图CAD,到能够仿真验证的CAE阶段,再到模块化的自动化工具EDA。EDA作为集成电路设计的基础工具,随着大规模集成电路、计算机和电子系统设计技术的不断发展,发挥了至关重要的作用,已经从辅助性技术成为了芯片产业的核心支柱技术之一,是IC设计最上游、技术壁垒最高的部分。没有EDA软件的支持,芯片的设计成本将几十上百倍地增加。

根据应用场景的不同,EDA工具的使用主要分为设计、验证、封装、制造等几大类,其中验证(Verification)在EDA工具中覆盖从前端逻辑设计、到后端物理设计、最终制造量产的整个环节,随着芯片设计成本越来越高昂,以及集成度的提高,复杂性也在大幅提升,通过验证发现所有的设计缺陷和错误已命系成败,验证EDA工具已成为责任担当。

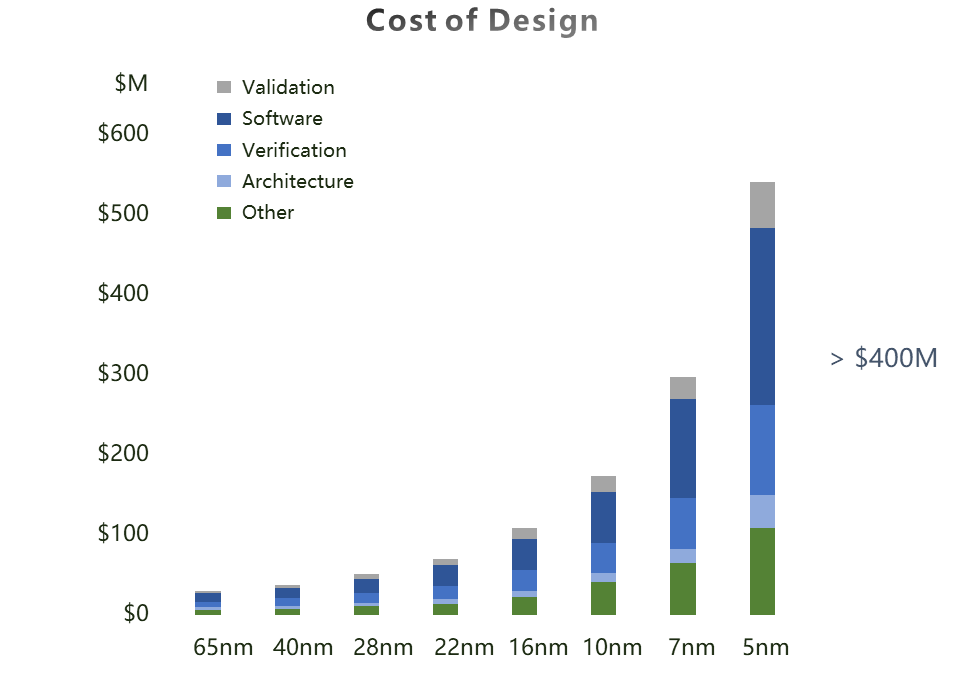

数据来源:IBS, Design Activities & Strategic Implications, July 2018

从验证来看,EDA软件非常复杂,技术壁垒也很高,最重要的是不仅要开发出工具,而且一定要不断迭代,要有生态和客户的支持,才能形成闭环。尽管国际三大巨头经过多年的积累,在验证市场已有相应的成熟产品,但如果想进一步创新和迭代,则必须要考虑向前兼容,这无疑是一个沉重的历史包袱。这也促成了中国在验证EDA领域破局的机会。

二、大芯片有哪些验证痛点

大芯片一般指大型SoC芯片,包含AI engine、CPU、GPU等,多使用12nm以下先进制程,应用于机器学习、自动驾驶、图像识别、自然语言处理、数据中心等领域。对大芯片的验证,是一项复杂且具有挑战的任务,主要痛点体现在如下四个方面。

第一,验证工具需要支持足够大的芯片设计容量。大芯片的流片成本居高不下,流片失败的损失难以估量,因此验证工具需要与时俱进,能够灵活堆叠,从而支持超大规模的芯片设计,并且保障正确性、可靠性。

第二,验证时间需要尽可能缩短。有些验证工具的自动化程度较低,部分流程需要手动干预,这将耗费工程师的精力,影响芯片上市时间。比如,在原型验证方面,因芯片设计过大,需要进行分割后才能验证,传统方法是采用手动分割,既费时费力,又极易出错,自动、智能的分割方法及工具是必然趋势。

第三,需要高效的调试工具。一旦出现问题,需要尽快找到设计中的问题点进行调试,实现最快的迭代速度。面对复杂芯片,有些验证平台的观测性和调试性较差,影响验证效率。此外,调试工具在迭代过程中,还要不断引入方法学和流程的创新,不仅支持功能的调试,还应拓展至功耗、覆盖率、安全等方面的调试;不仅要支持不同设计层级如RTL和Gate级的需求,还要支持事务级和系统级的验证调试。

第四,流片前的验证算力峰值需求如何解决。IC企业流片前存在3-6个月的算力峰值需求,芯片验证需要大内存、高主频的算力以及高性能存储等。如果本地搭建,会耗费大量人力、物力、财力,还会存在计算、存储等硬件资源的限制,加上耗时的采购与部署流程,导致验证工程师难以在预定上市时间内完成所有期望的作业。

三、FPGA原型验证是大芯片验证的首选方法

面临这些痛点,FPGA(现场可编程门阵列)原型验证已发展成为芯片公司首选的验证方法。FPGA原型验证,是基于FPGA的一种芯片功能验证方式。它利用了FPGA可以多次擦写的特性,在芯片RTL代码开发的过程中,将RTL代码综合到FPGA上来做芯片的功能验证。其目的是在芯片流片之前,为芯片开发团队提供一个可以反复迭代的逻辑验证平台。在芯片设计定型之后,流片回片之前,为软件开发团队提供一个可以提前开发软件功能的硬件环境,缩短芯片回片之后产品的上市时间。这个验证环境能够让芯片验证与软件验证并行,确保芯片软硬件功能在真实应用场景中准确无误。

FPGA通过级联,即可轻松实现大规模的芯片验证;并且运行速度高,特别适合系统级验证。再进一步通过级联数台FPGA原型验证仿真器,即可搭建EDA云数据中心,通过云端弹性算力,满足IC企业峰值算力需求,并能有效降低企业的IT投入和运维成本,提高芯片设计和验证的效率和质量,还可以实现跨地域、跨平台、跨设备的协同工作。

四、相比其它验证手段,FPGA原型验证有何优势

现代SoC芯片是一个软硬件协同运行的系统。上面有复杂的软件运行,和芯片硬件共同实现各种功能。与芯片协同工作的软件系统,其设计、开发和验证工作需要和芯片设计验证工作同步展开。这样才能保证芯片功能正确,降低芯片流片失败的风险,缩短产品的上市周期。

为了保证芯片功能正确,在芯片RTL代码开发之后,需要经过一系列的验证流程。常见的数字芯片验证手段,包括逻辑功能仿真、形式化验证、硬件仿真和FPGA原型验证等。

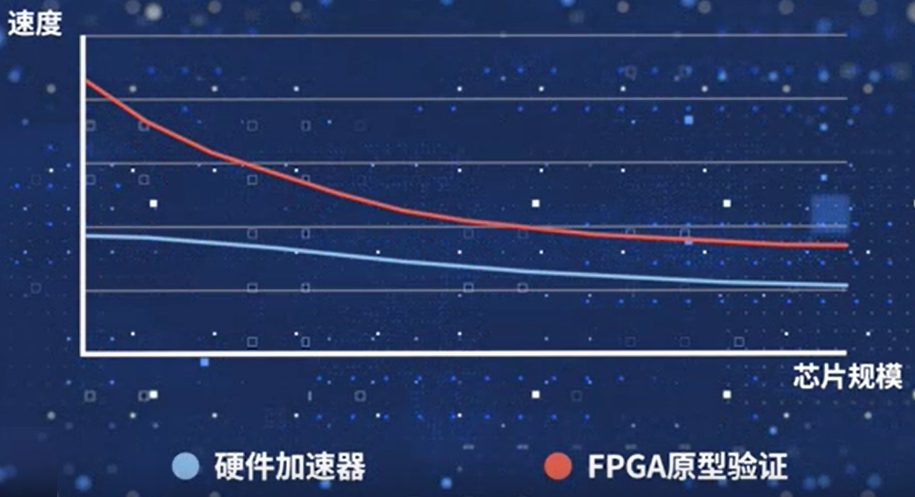

这几种常见的数字芯片验证手段中,FPGA原型验证技术是最适合芯片软硬件协同功能的验证技术之一。FPGA原型验证平台可以提供调试芯片软件必要的真实物理接口和硬件环境。这是逻辑功能仿真和形式化验证无法提供的。相比硬件加速器,FPGA原型验证平台的软件运行速度快一个数量级,很大程度缩短了软件运行时间和验证迭代的周期,优化接口逻辑运行频率可以使之对接真实设备,同时也使得软硬件开发验证并行成为可能。在芯片验证流程中,FPGA原型验证技术是软硬件协同功能验证的必备解决方案,具有显著的不可替代性。

因此,FPGA原型验证技术,作为主流且成熟的芯片验证方法,已成为数字芯片公司不可或缺的验证工具。

五、合见工软数字验证全流程及新一代时序驱动FPGA原型验证系统UV APS

上海合见工业软件集团有限公司(简称“合见工软”)作为自主创新的高性能工业软件及解决方案提供商,核心是数字芯片验证的全流程支持,实现从点到面的突破。合见工软现已推出完整的数字芯片验证全流程工具,包括:商用级别逻辑仿真器UVS,时序驱动的高性能原型验证系统UV APS、数字功能仿真调试工具UVD、大规模功能验证回归测试管理平台VPS、即插即用的混合原型系统级IP验证方案HIPK。同时合见工软还对上海阿卡思、孤波科技进行战略投资,补充形式化验证工具和半导体自动化测试工具为全流程验证平台。

其中,2022年6月发布的新一代时序驱动FPGA原型验证系统UniVista Advanced Prototyping System(UV APS)为合见工软旗舰产品。自产品面世以来,已经在高性能计算、5G通信、GPU、人工智能、汽车电子等领域的IC企业中成功部署应用。

UV APS单套设备使用了4片 FPGA,可灵活堆叠,最大容量支持25套设备级联(100片FPGA互联)。集成智能化、自动化的全流程编译软件 APS Compiler,为芯片设计者提供了高效的验证方式,降低在验证阶段的时间成本;同时提供丰富的FMC接口子卡,以适配各种接口验证,提供充足的One-Bank互联通道,以支撑系统扩展;配合深度调试方案,缩短测试周期,加快芯片上市。

图 新一代时序驱动FPGA原型验证系统UV APS

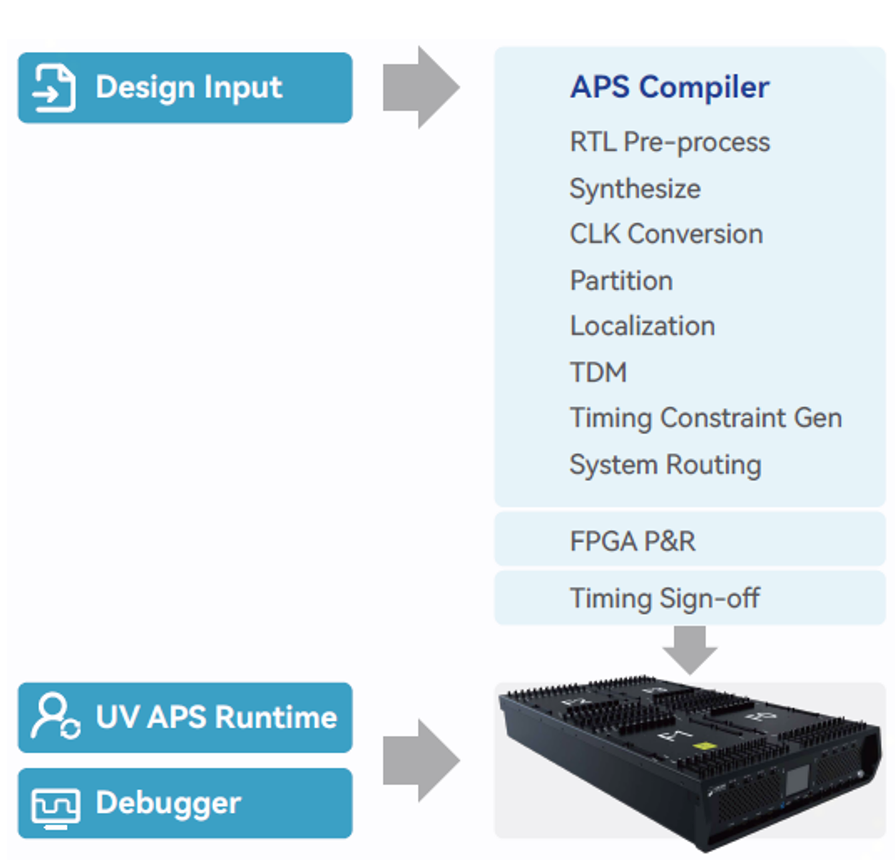

创新点一:创新自研的时序驱动全流程编译软件APS Compiler

UV APS集成了创新自研的时序驱动全流程编译软件APS Compiler,在性能和自动化程度方面具有明显优势。

在性能上:APS Compiler内嵌时序驱动分割引擎,可通过大范围的TDM Ratio自动最优求解,轻松处理多达100颗FPGA的设计容量,让逻辑电路运行速度更快。同时,APS Compiler还能实现自动化时序驱动分割、片间走线、逻辑本地化、MCP(多周期路径)分析等,使时序驱动流程更完整。对于典型的SoC设计,APS Compiler的验证性能高达20+MHz,可轻松支持10亿门以上设计的分割需求。

在自动化程度上:APS Compiler可基于RTL Module的时序驱动分割算法,提供全自动和人工向导两种模式,助力实现高效验证。而对于FPGA不能支持的设计单元,比如多端口存储(Multi-port Memory)、多维数组、跨模块引用(XMR)、三态门(Tri-state)等,业界一些主流工具会要求用户修改RTL代码,而UV APS可实现自动化转换。

图 UV APS自动化时序驱动编译流程

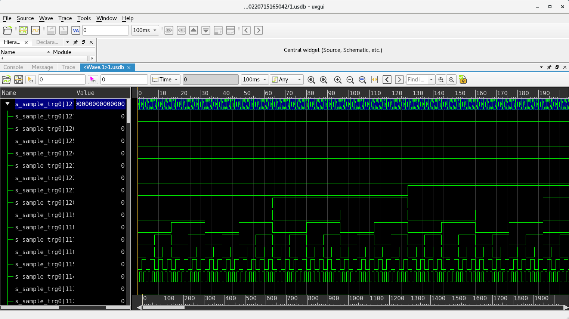

创新点二:多样化调试手段

在原型验证过程中,调试功能是不可或缺的。传统FPGA原型验证平台受限于自身容量,其观测性和调试性较差,而UV APS在这两方面做出了较大提升。

UV APS中的信号波形采集工具不占用FPGA内部存储空间,通过可配置的Trigger条件,抓取设计内部信号波形,存储到外部专用Memory上。可支持多种逻辑组合的触发条件,波形显示清晰便于直观查看。

同时,UV APS支持FPGA芯片回读捕获调试,可读取片内寄存器值;Back Door功能可实现后门读写,有效避免用户频繁地重启系统;支持多FPGA、多触发条件调试,多时钟域信号采集至单一波形文件,多波形单一窗口组合显示。此外,ECO功能通过利用VIVADO工具的增量布局布线特性,可以加快周转时间。这些调试方式都能极大地提高调试效率,大幅缩短测试周期和上市时间。

图 UV APS丰富的Debug功能

创新点三:大容量、拓展灵活的硬件系统

FPGA原型验证平台作为一个生产工具,其硬件系统的大容量与可拓展的灵活性都将直接影响芯片验证的进度。

在容量方面,UV APS硬件系统能够支持最多25台设备级联。

在灵活性方面,UV APS硬件系统中单颗FPGA便可支持46路以上高速GTY收发器,速度高达28Gbps,支持多路全局可编程时钟。此外,UV APS中单颗FPGA还拥有超过1700个IO接口,并提供FMC外部标准扩展接口和One Bank连接器,可满足用户的互联需求。

UV APS硬件系统还提供了自检功能,同时支持上位机软件控制上电、断电功能,并且带有:系统状态监测、过流过压保护、温度监测等一系列的安全保护措施。

创新点四:适配典型应用场景的解决方案

合见工软UV APS同时提供了面向多种行业应用的原型验证子卡、Memory Model、Speed Adaptor及快速定制服务;UV APS支持PCIe Gen5、DDR5、HBM2e、HBM3、MIPI、LPDDR5、Gigabit Ethernet等高性能接口速率适配,支持虚拟原型混合验证等一系列适配多种典型应用的解决方案,以满足用户对原型验证的各种复杂场景需求。

六、大芯片验证算力集群解决方案——企业级EDA云数据中心

区别于传统的云数据中心,EDA云数据中心需要搭建专用的硬件仿真器,来进行大规模的芯片验证。其次,数据安全性对IC企业尤为重要,必须确保芯片设计、验证是在安全的工作环境中。再结合灵活的付费模式、云端弹性算力,EDA云数据中心可以有效降低企业的硬件投入成本,提高芯片验证效率。

以合见工软针对某半导体设计公司的云数据中心项目为例,合见工软为本项目定制化部署了企业级EDA云数据中心,建设了专用的IDC机房。根据客户的算力要求,搭建了FPGA硬件验证云设备集群,级联数百颗FPGA,全天候7x24小时运行,为客户的超大规模系统芯片做验证。并可同步运作多种验证场景,包括芯片设计仿真Simulation云任务、系统级PCB设计软件云任务等,同时支持跨地域验证团队协同使用云数据中心资源。

七、结语

基于自建的EDA云数据中心,结合新一代时序驱动FPGA原型验证系统UV APS等旗舰产品,合见工软在解决大芯片的验证问题方面实现了升维和突破,不仅进一步提升了我国在EDA验证工具领域的水平,也将为国内半导体设计业的发展持续助力。

合见工软秉承两点原则为中国芯片企业提供支持:“以客户为中心,以产品为核心竞争力”。EDA是一个产品为王的行业,在保持技术和性能领先的同时,需要更快地把握设计公司的真正需求和痛点,从前端需求上研发和演进EDA设计方法学,打造更好的产品和技术,并持续优化,秉持“守正出新,笃行致远”的企业精神,合见工软将不断的进行迭代和技术更新,以保持产品竞争力。

审核编辑 :李倩

-

FPGA

+关注

关注

1629文章

21736浏览量

603419 -

芯片

+关注

关注

455文章

50816浏览量

423672 -

eda

+关注

关注

71文章

2759浏览量

173275

原文标题:设计大芯片,这个问题不容忽视!

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

i.MX处理器如何解决工业自动化三大痛点:PLC、人机交互、机器人

【直播预告】ADI &amp; WT·世健MCU痛点问题探索季:MCU应用难题全力击破!

光伏电站运维系统解决传统光伏电站运维痛点

IO模块助力水处理行业升级,破解行业发展痛点

芯片测试和芯片验证的区别

工业级路由器:解决网络传输的痛点

锡膏点胶时拉丝不均匀,如何解决?

数据采集边缘网关解决企业数据采集痛点的关键

电源测试系统如何解决电源模块测试痛点?

如何解决大芯片的验证痛点

如何解决大芯片的验证痛点

评论