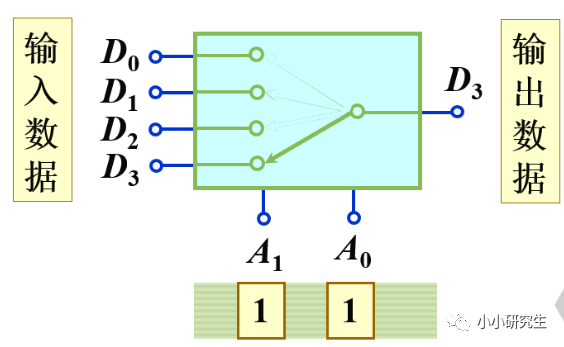

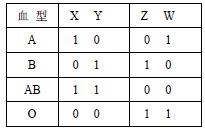

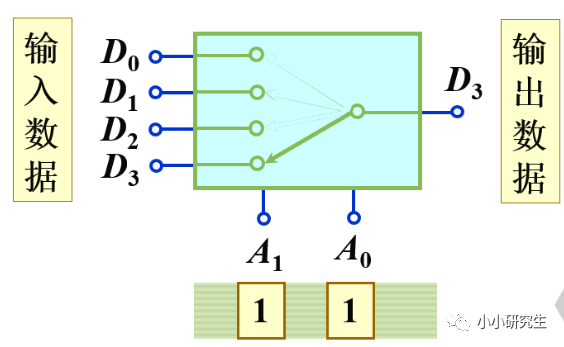

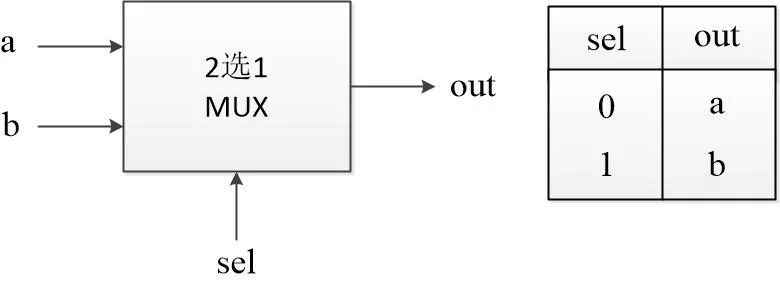

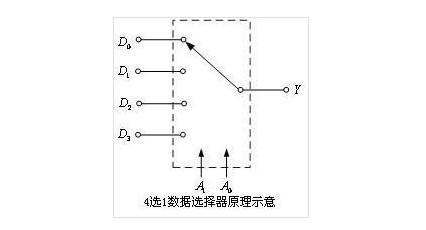

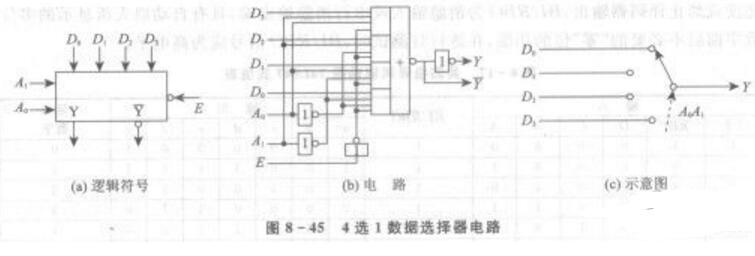

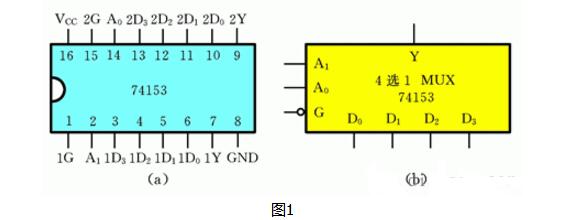

组合逻辑电路的输出信号只与当前时刻的输入信号有关,与其他时刻的输入状态无关,无存储电路或反馈电路。多路选择器是在多路数据传送过程中,根据需要选择一条电路。如果还没看懂功能,结合真值表就好理解了。

A1A0是选择线,D0-D3是数据线,A1A0构成00-11共4种选择,对应着D的下标,被选中的数据线作为输出。8选1,16选1同理。在本例中,选择最简单的2选1电路。

设计规划

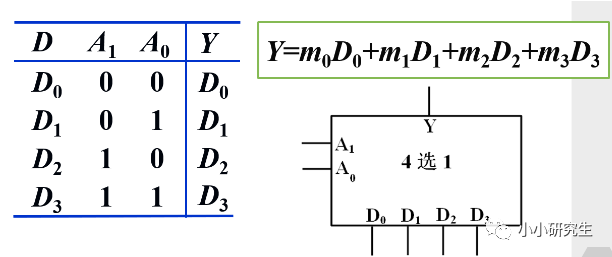

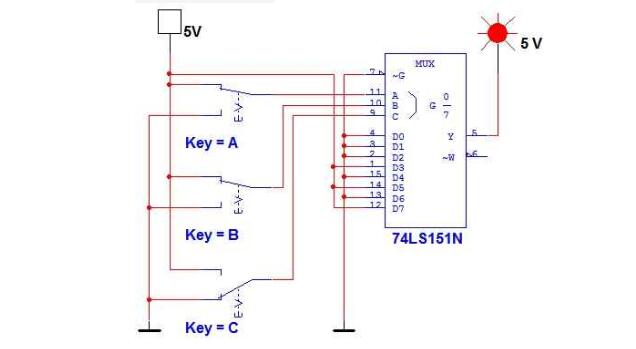

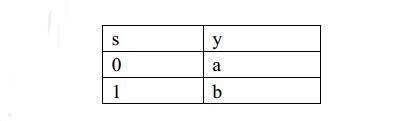

这个示例中,采用两个按键作为信号输入,一个按键作为信号选择,LED作为数据输出。需要实现的功能是,当按下按键sel时(sel=0),LED灯状态取决于按键in2,当不按下sel时(sel=1),LED灯状态取决于按键in1。h绘制波形图如图所示。

编写代码

module mux2_1(

input wire in1,

input wire in2,

input wire sel,

output wire out);

assign out=(sel==1'b1)?in1:in2;

endmodule

这里的组合逻辑电路可以采用always中if-else实现方法,always中case实现方法,assign中条件运算符(三元运算符)实现方法。涉及到always的语句还没进行总结,这里采用最简单的assign语句,用到了很熟悉的三元运算符。编写好.v文件后编译通过。

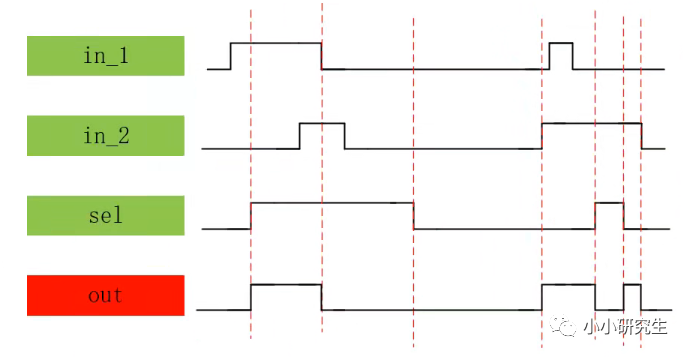

点击RTL viewer可以查看设计的硬件电路结构,和我们设计所表达的意思相同。

编写testbench

`timescale 1ns/1ns

module tb_mux2_1();

//在testbench中待测试RTL模块的输入永远是reg型变量

reg in1;

reg in2;

reg sel;

//在testbench中待测试RTL模块的输出永远是wire型变量

wire out;

initial

begin

in1 <=1'b0;

in2 <=1'b0;

sel <=1'b0;

end

//每隔10ns产生输入随机数0或1

always #10 in1 <= {$random} % 2;

always #10 in2 <= {$random} % 2;

always #10 sel <= {$random} % 2;

//------------------------mux2_1_inst------------------------

mux2_1 mux2_1_inst

(

.in1(in1), //input in1

.in2(in2), //input in2

.sel(sel), //inputsel

.out(out) //output out

);

endmodule

和上一节中结构类似,tb_mux2_1模块中,首先定义初始的输入信号in_1,in_2,sel为低电平(一般时序电路使用非阻塞赋值<=),延迟10个时间单位(ns)产生随机数0或1赋值给输入,就完成了输入信号的波形设计。根据实例化的讲解,第2-6行和第22-28行完成的功能是将上一个mux2_1.v文件中mux2_1模块与tb_mux2_1模块相连。这样随机生成的输入信号就被加到mux2_1模块上,并得到输出mux2_1_out,通过验证mux2_1_out与我们期望的输出是否一致,就知道我们的设计是否正确。

对比波形

波形显示当sel为高电平时,out与in1一致,sel为低电平时,out与in2一致。

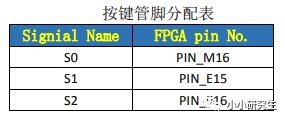

分配管脚

全编译后上板验证

按下S2(sel=0)时,按下S1(in2=0)LED就亮(out=in2=0),只按下S0(in1=0)LED就亮(out=in1=0)。

-

led灯

+关注

关注

22文章

1592浏览量

107936 -

RTL

+关注

关注

1文章

385浏览量

59752 -

组合逻辑电路

+关注

关注

6文章

70浏览量

14648 -

多路选择器

+关注

关注

1文章

22浏览量

6524

发布评论请先 登录

相关推荐

4选1多路选择器是什么?

译码器及多路选择器的使用( EDA 仿真) 实验

8选1多路选择器电路图(五款8选1多路选择器电路)

Verilog HDL之多路选择器设计

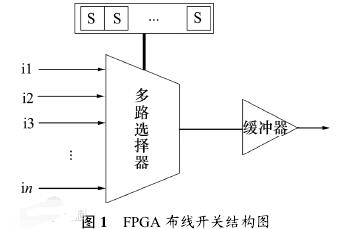

基于FPGA的多路选择器设计

多路选择器设计

多路选择器设计

评论