介质的填充:

|

填孔间隔 |

CVD方式 |

特点 |

|

0.8μm以上 |

PECVD |

对于小于0.8μm的间隔,用PECVD工艺填充高的深宽比的间隔时,会在间隔中部产生夹断(pinch-off)和空穴 |

|

0.25μm以上 |

APCVD(常压)、SACVD(亚常压) |

缺乏等离子体辅助沉积产生的膜有低密度和吸潮性的问题,需要增加PECVD薄膜对其进行保护,或者进行后沉积处理(如退火回流等)。这些工序的加入提高了生产成本,增加了整个工艺流程的步骤和复杂性。 |

|

0.25μm以下 |

HDPCVD |

同时满足高深宽比间隙的填充和控制生产成本的要求 |

|

亚65nm、器件深宽比大于8 |

SACVD |

HDPCVD的工艺变得非常复杂,沉积速度变慢,而且随着循环次数的增加,刻蚀对衬底的损伤会变得更加严重。O3-TEOS基的SACVD可以在保证填充能力的条件下,获得较快的生长速度。 |

-

影响台阶覆盖率的因素:

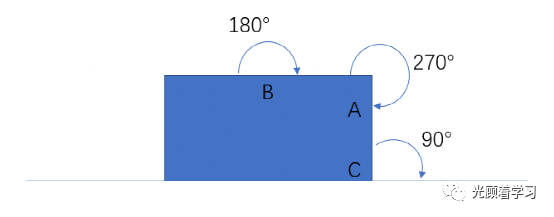

1、反应体到达时,衬底的接收角度;

2、反映腔压力(质量运输控制或表面反应控制);

3、被吸附反应体在衬底表面的迁移率

A能接收更多的先驱体,淀积生成物更多,形成的悬垂突起,悬垂突起会造成孔内空洞的产生。

-

HDPCVD作用机理:

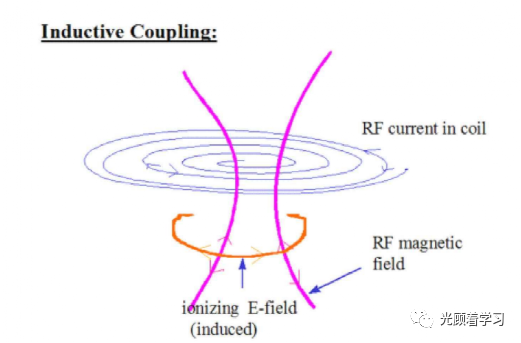

为了形成高密度等离子体,需要有激发混合气体的射频(RF)源,并直接使高密度等离子体到达硅片表面。在HDP-CVD反应腔中,主要是由电感耦合等离子体反应器(ICP)来产生并维持高密度的等离子体。当射频电流通过线圈(coil)时会产生一个交流磁场,这个交流磁场经由感应耦合即产生随时间变化的电场,如图所示。电感耦合型电场能加速电子并能形成离子化碰撞,由于感应电场的方向是回旋型的,因此电子也就往回旋方向加速,使得电子因回旋而能够运动很长的距离而不会碰到反应腔内壁或电极,这样就能在低压状态(几个mT)下制造出高密度的等离子体。

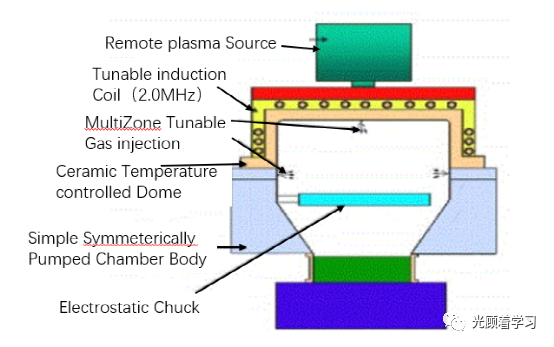

应用材料HDP-CVD反应腔

电感耦合等离子体反应器(ICP)工作原理示意图

为了实现HDP-CVD的bottom up生长,首先要给反应腔中的高能离子定方向,所以沉积过程中在硅片上施加RF偏压,推动高能离子脱离等离子体而直接接触到硅片表面,同时偏压也用来控制离子的轰击能量,即通过控制物理轰击控制CVD沉积中沟槽开口的大小。在HDPCVD反应腔中,等离子体离子密度可达10^11 ~10^12/cm3(2~10mT)。由于如此高的等离子体密度加上硅片偏压产生的方向,使HDPCVD可以填充深宽比为4:1甚至更高的间隙。

HDPCVD可用于金属形成前或形成后。某些金属如NiSix或Al会对形成后的工艺温度有一定限制,而在HDPCVD反应腔中高密度等离子体轰击硅片表面会导致很高的硅片温度,另外,高的热负荷会引起硅片的热应力。对硅片温度的限制要求对硅片进行降温,在HDPCVD反应腔中是由背面氦气冷却系统和静电卡盘(electrostatic chuck)共同在硅片和卡盘之间形成一个热传导通路,从而来降低硅片和卡盘的温度。

Centura Ultima HDP CVD应用材料公司的HDPCVD设备 https://www.appliedmaterials.com/cn/zh_cn/product-library/centura-ultima-hdp-cvd.html

HDPCVD的反应包含两种或多种气体参与的化学反应。根据沉积的绝缘介质掺杂与否及掺杂的种类,常见的有以下几种:

(1)非掺杂硅(酸盐)玻璃(un-doped silicate glass,USG)

SiH4 +O2 —→USG+挥发物

(2)氟硅(酸盐)玻璃(fluorosilicate glass,FSG)

SiH4 +SiF4 +O2 —→FSG+挥发物

(3)磷硅(酸盐)玻璃(phosphosilicate glass,PSG)

SiH4 +PH3 +O2 —→PSG+挥发物

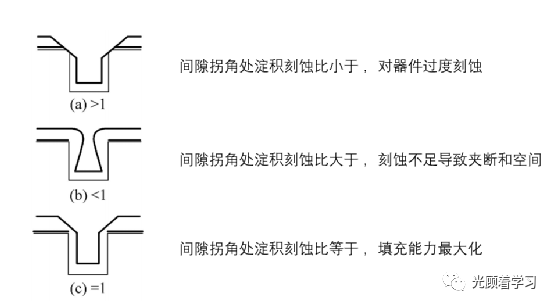

沉积刻蚀比=总沉积速率/刻蚀速率=(净沉积速率+刻蚀速率)/刻蚀速率

实现对间隙的无孔填充的理想条件是在整个沉积过程中始终保持间隙的顶部开放,以使反应物能进入间隙从底部开始填充,也就是说,我们希望在间隙的拐角处沉积刻蚀比为1,即净沉积速率为零。对于给定的间隙来说,由于HDP-CVD工艺通常以SiH4 作为绝缘介质中Si的来源,而SiH4 解离产生的等离子体对硅片表面具有很强的化学吸附性,导致总沉积速率在间隙的各个部位各向异性,在间隙拐角处的总沉积速率总是大于在间隙底部和顶部的总沉积速率;另外,刻蚀速率随着溅射离子对于间隙表面入射角的不同而改变,最大的刻蚀速率产生于45°~70°之间,正好也是处于间隙拐角处,因此需要优化沉积刻蚀比来得到最好的填充效果。

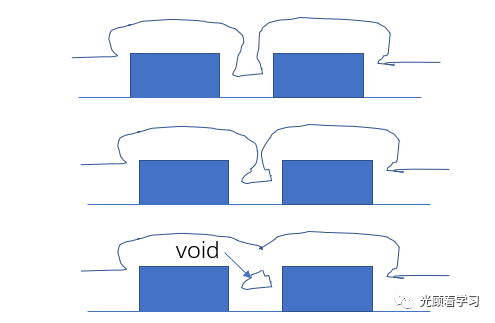

下图即是HDP-CVD工艺在不同沉积刻蚀比下对间隙填充情况的示意图。要得到优化的沉积刻蚀比,最主要的影响因素包括反应气体流量、射频(包括电感耦合和偏压)的功率、硅片温度、反应腔压力等。

-

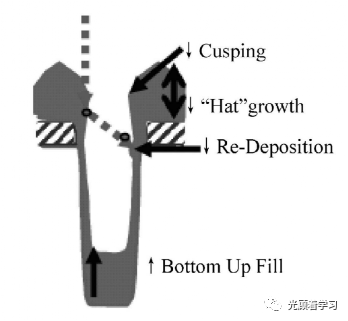

HDP-CVD中的再沉积问题:在HDP-CVD中的物理轰击遵循碰撞中的动量守恒原理,因此被溅射出的物质存在一定角度。随着沟槽开口尺寸变小,当轰击离子质量较大时,被轰击掉的部分会有足够的能量重新沉积到沟槽侧壁另一侧某一角度处,使得这些地方薄膜堆积,过多的堆积将会造成沟槽顶部在没有完全填充前过快封口。随着器件尺寸减小,填充能力的挑战越来越大。为了减少物理轰击造成的再沉积,HDP中的轰击气体主要经历了Ar→O2 →He→H2的变化,通过降低轰击原子的质量来改善再沉积引起的填充问题。但是仅仅通过轰击物质的改变,沟槽填充能力的改善是有限的。

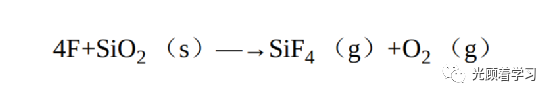

所以在90nm以后,为改善物理轰击所造成的问题,引入同位化学刻蚀对填充结构轮廓进行调整,即在沟槽顶部封口前将其重新打开而不造成再沉积,使得薄膜可以bottom-up填满整个沟槽。其中NF3的干法刻蚀被认为是一种非常有效的方法。NF3 在等离子体中离解形成含氟的活性基团,它可以打断已沉积薄膜中的Si-O键,形成挥发性的SiF4 随着多余的O2 一起被抽走,从而打开沟槽顶部。但是这种单步沉积-刻蚀-沉积对填充能力的改善是有限的。

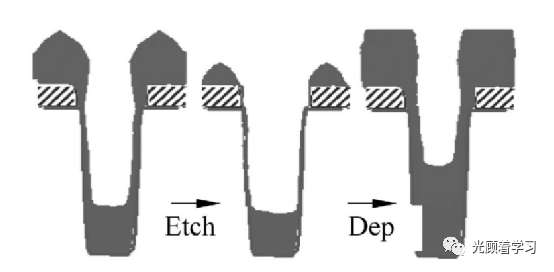

通过多步循环沉积-刻蚀-沉积来实现对所填充结构轮廓的调整,来降低沟槽填充的难度。这样可以在保持HDP本身填充能力的同时,通过NF3 的刻蚀来重新调整沟槽的形状,使得更多的材料可以填充进去,保证沟槽不封口形成孔洞。

-

轮廓修正(多步沉积-刻蚀)的HDP-CVD工艺:与一般的HDP相似,主要通过SiH4 和O2 反应来形成SiO2 薄膜。但是沉积过程的要求与传统的HDP不同,传统的HDP-CVD要求侧壁沉积尽可能薄以提供足够的开口使反应粒子可以到达沟槽底部,最大限度实现从底部到顶部的填充。但是多步DEP-ETCH的HDP-CVD主要是以SiO2 的刻蚀为主导的,因此轮廓结构的控制更重要,最优化的沉积应该有足够厚的侧壁保护,对称的沉积轮廓,较低的沉积温度(230~600℃)能够很大地改善侧壁的保护但又不损伤填充能力,同时可以通过调节沉积温度将薄膜的应力从180MPa调到100MPa。一旦沉积条件确定后,填充能力可以通过每个循环中沉积和刻蚀的量来优化。降低每个沉积过程的沉积厚度可以实现更多次的轮廓调整,但是这样会增加沉积时间也引入更多的F,有可能会对器件可靠性造成影响。而沉积过程中的物理轰击气体分子量越大,可以在沟槽顶部形成Cusping来以保护沟槽顶部在刻蚀过程中不被损伤。目前主要采用He为主的He/H2 混合,主要想通过保证填充能力的同时为沟槽顶部提供足够的保护。

-

多步沉积-刻蚀HDP-CVD的工艺:刻蚀过程是多步dep-etch的关键步骤,刻蚀过程通过与NF3 的反应去除掉SiO2,由于NF3 在沟槽不同部位的入射角不同,可以实现顶部刻蚀较多从而可以修整部分填充后的沟槽的形状得到更容易填充的沟槽结构。刻蚀过程所采用的载气为H2,载气的分子量越小,可以尽量减少物理轰击的效果。另外刻蚀的对称性对最后的完全填充非常重要,尤其在晶片边缘,由于F radical的方向性,这种不对称性就更加严重,可以通过调节压力、NF3 气体流量、衬底偏压大小以及刻蚀化学物质来对对称性进行优化。刻蚀的量必须进行非常好的控制。对于特定的沟槽结构,要进行沉积和刻蚀量的优化,尽可能达到填充、沉积速率以及刻蚀Window的平衡。另外为了尽可能降低薄膜中由于NF3 刻蚀而引入的F。刻蚀结束后,引入Ar/O2/He/H2 等离子体处理可以去除薄膜中所残留的F,通过调整等离子体处理的时间和功率大小可以优化等离子体处理工艺,将薄膜中的F含量降低到0.07at.%。

多步沉积-刻蚀填满沟槽后,进一步沉积一层高温的SiO2 薄膜,进一步去除薄膜中残留的F以及提高薄膜的质量。

HDPCVD的应用:浅沟槽隔离层(STI)、金属前介电质层(PMD)、层间介电质层(ILD)、金属层间介电质层(IMD)和钝化保护层等。

审核编辑 :李倩

-

射频

+关注

关注

104文章

5581浏览量

167719 -

等离子体

+关注

关注

0文章

122浏览量

14223 -

反应器

+关注

关注

2文章

97浏览量

11050

原文标题:半导体绝缘介质的填充-HDPOX

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

常用半导体手册

详解:半导体的定义及分类

芯片,集成电路,半导体含义

功率半导体模块的发展趋势如何?

《炬丰科技-半导体工艺》半导体集成电路化学

半导体的定义及其作用

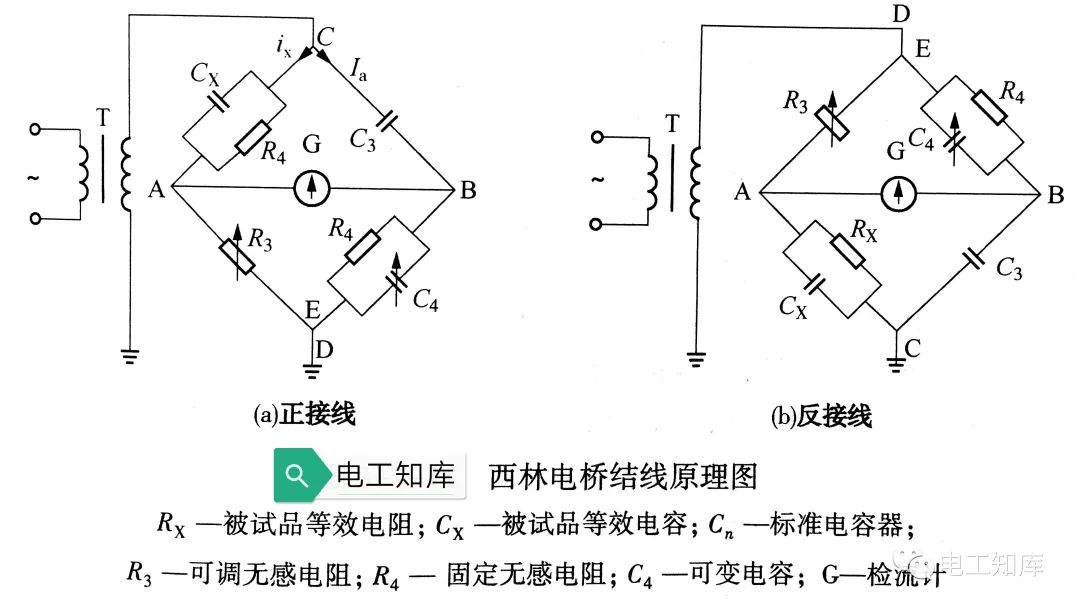

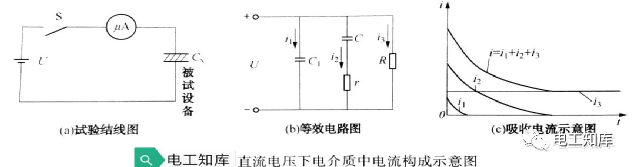

固体电介质的绝缘特性_固体电介质的击穿形式

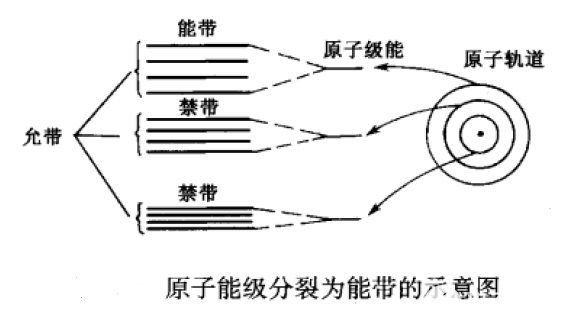

涨知识啦2—导体、半导体和绝缘体

导热绝缘胶BGA底部微空间填充工艺研究

半导体绝缘介质的填充-HDPOX

半导体绝缘介质的填充-HDPOX

评论