PCIE 6.0 (一)

⊙PCIE ⊙介绍

PCI Express® 6.0 (PCIe® 6.0) 规范由 PCI-SIG® 于 2022 年 1 月发布。最新一代的 PCIe 标准带来了许多激动人心的新功能,旨在提高计算密集型工作负载的性能,包括数据中心、 AI/ML 和 HPC 应用程序。

我们将持续几期为大家介绍PCIE 6.0协议

0****1

**###

什么是 PCIe 6.0

**

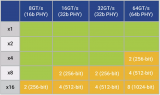

自 PCIe 3.0 以来,每一代新标准的数据速率都翻了一番。 PCIe 6.0 将数据速率提高到每秒 64 千兆传输 (GT/s),是 PCIe 5.0 的两倍。 对于显卡和网卡典型的 x16 链路,链路带宽达到每秒 128 GB (GB/s)。 与前几代产品一样,PCIe 6.0 链路是全双工的,因此它可以同时在两个方向上提供 128 GB/s 的带宽,总带宽容量为 256 GB/s。

PCIe 除了已经广泛扩展到服务器和 PC 之外,其规模使其对物联网、汽车、医疗和其他领域以数据为中心的应用程序具有吸引力。 也就是说,PCIe 6.0 的初始部署将针对需要尽可能高带宽的应用程序,这些应用程序可以在数据中心的核心找到:AI/ML、HPC、网络和云图形。

下图显示了 PCIe 规范随时间的演变:

0****2

**## PCIe 6.0 有什么新功能

**

为实现 64 GT/s,PCIe 6.0 引入了新功能和创新:

1. PAM4 信令:

PCIe 1.0 到 5.0 使用不归零 (NRZ) 信号,每个时钟提供 1 位。 此外,PCIe 1.0 和 2.0 采用 8b/10b(八位/十位)编码,而 3.0 到 5.0 采用 128b/130b 编码。 相比之下,PCIe 6.0(以及即将推出的 7.0)使用脉冲幅度调制 4 级 (PAM4),这是一种多级信号调制格式,每个时钟提供 2 位。

PCIe 6.0 使用 PAM4 信号(“四级脉冲幅度调制”),每个时钟周期将 2 位组合为 4 个幅度级别(00、01、10、11),与 PCIe 5.0 和前几代相比,它 使用 NRZ 调制,每个时钟周期 1 位和两个幅度级别 (0, 1)。

2.前向纠错(FEC)

权衡总是存在的,与 NRZ 相比,向 PAM4 信号编码的过渡引入了明显更高的误码率 (BER)。 这促使采用前向纠错 (FEC) 机制来缓解较高的错误率。 PCIe 6.0 FEC 足够轻,对延迟的影响最小。 它与强大的 CRC(循环冗余校验)结合使用,可将链路重试概率保持在 5×10^-6 以下。 这个新的 FEC 功能旨在将延迟时间缩短到 2ns 以下。

虽然 PAM4 信号更容易出错,但由于调制技术的性质,与 PCIe 5.0 相比,通道损耗不受影响,因此 PCB 上 PCIe 6.0 信号的范围将与 PCIe 5.0 相同。

3. FLIT 模式:

PCIe 6.0 引入了 FLIT 模式,在这种模式下,数据包以固定大小的流量控制单元组织,而不是过去几代 PCIe 中的可变大小。 引入 FLIT 模式的最初原因是纠错需要使用固定大小的数据包; 然而,FLIT 模式还简化了控制器级别的数据管理,并带来更高的带宽效率、更低的延迟和更小的控制器占用空间。 让我们花一分钟时间来解决带宽效率问题:对于固定大小的数据包,不再需要物理层的数据包成帧,这为每个数据包节省了 4 个字节。 FLIT 编码还消除了以前 PCIe 规范中的 128B/130B 编码和 DLLP(数据链路层数据包)开销,从而显着提高 TLP(事务层数据包)效率,尤其是对于较小的数据包。

4. PCIe 6.0的其他变化:

L0p 模式:使用较少的lane以节省电力

PCIe 6.0 有趣的是降低了前几代的 x32 和 x12 接口宽度。 在 PCIe 5.0 和更早的规范中,这些宽度从未在市场上实现。

0****3

**## 为什么现在是 PCIe 6.0

**

2015 年之前,PCIe 在带宽方面远远领先于市场所需。 没有运行得更快的市场驱动力,因此规范的发展速度较慢。 2015年后,全球数据流量呈爆发式增长。 数据中心过渡到 100G 以太网(及以上)将瓶颈推向服务器和网络设备中的 PCIe 互连。

PCIe 6.0 规范完全支持数据中心向 800G 以太网的过渡:每秒 800 Gb (Gb/s) 需要 100 GB/s 的带宽,这在 x16 PCIe 6.0 链路的 128 GB/s 范围内; 800G 以太网与 PCIe 一样,是全双工的。 此外,数据中心通用计算和网络并不是 PCIe 6.0 背后的唯一驱动力。 AI/ML 加速器对更多带宽的需求永无止境。 处理 AI/ML 训练模型的关键在于速度,加速器移入移出数据的速度越快,训练的执行效率和成本效益就越高。

-

PCI

+关注

关注

4文章

666浏览量

130264 -

数据中心

+关注

关注

16文章

4774浏览量

72111 -

PCIe

+关注

关注

15文章

1237浏览量

82621 -

HPC

+关注

关注

0文章

316浏览量

23765

发布评论请先 登录

相关推荐

Samtec技术前沿 | 多重原因促使PCIe® 6.0采用了PAM4

PCIe 6.0元年,AI与HPC迎来新速度

楷登电子发布PCIe 6.0规范Cadence IP

泰克提供业界首创的 PCIe 6.0 测试解决方案

PCIe 6.0的新变化与新挑战

PCIe 6.0规范及它是如何从过去的规范演变而来的

PCIe 6.0有啥用?

干货:PCIE6.0技术剖析

如何破解PCIe 6.0带来的芯片设计新挑战?

AI和数据中心:PCIe 6.0,你是懂加速的

PCIe 6.0的优化设计方案探讨分析

新思科技PCIe 6.0 IP与英特尔PCIe 6.0测试芯片实现互操作

新思科技成功实现与英特尔PCIe 6.0测试芯片的互操作性

如何简化PCIe 6.0交换机的设计

PCIe 6.0入门之什么是 PCIe 6.0

PCIe 6.0入门之什么是 PCIe 6.0

评论