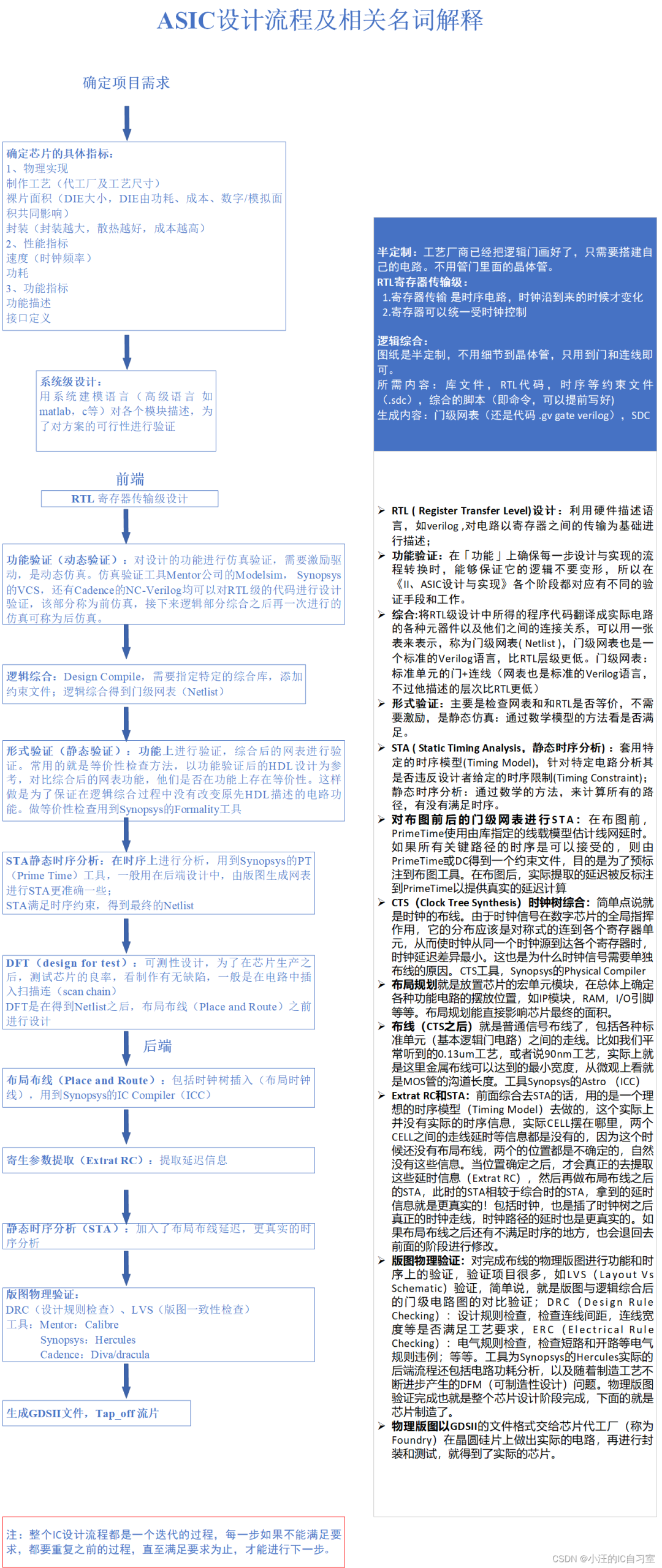

一、确定项目需求

1. 确定芯片的具体指标:

物理实现

制作工艺(代工厂及工艺尺寸);

裸片面积(DIE大小,DIE由功耗、成本、数字/模拟面积共同影响);

封装(封装越大,散热越好,成本越高)。

性能指标:

速度(时钟频率);

功耗。

功能指标:

功能描述

接口定义

2. 系统级设计:

用系统建模语言(高级语言 如matlab,c等)对各个模块描述,为了对方案的可行性进行验证。

二、前端流程

1. RTL 寄存器传输级设计

利用硬件描述语言,如verilog对电路以寄存器之间的传输为基础进行描述。

2. 功能验证(动态验证):

对设计的功能进行仿真验证,需要激励驱动,是动态仿真。仿真验证工具Mentor公司的 Modelsim, Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL级的代码进行设计验证,该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。

3. 逻辑综合(Design Compile):

需要指定特定的综合库,添加约束文件;逻辑综合得到门级网表(Netlist)。

4. 形式验证(静态验证):

功能上进行验证,综合后的网表进行验证。常用的就是等价性检查方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。做等价性检查用到Synopsys的Formality工具。

5. STA静态时序分析:

在时序上进行分析,用到Synopsys的PT(Prime Time)工具,一般用在后端设计中,由版图生成网表进行STA更准确一些;

STA满足时序约束,得到最终的Netlist。

6. DFT(design for test)可测性设计:

为了在芯片生产之后,测试芯片的良率,看制作有无缺陷,一般是在电路中插入扫描连(scan chain);

DFT是在得到Netlist之后,布局布线(Place and Route)之前进行设计。

三、后端流程

1. 布局布线(Place and Route):

包括时钟树插入(布局时钟线),布局布线用到Synopsys的IC Compiler(ICC)工具。

在布线(普通信号线)之前先布局时钟线,即时钟树综合CTS(Clock Tree Synthesis),用到Synopsys的Physical Compiler工具。

2. 寄生参数提取(Extrat RC):

提取延迟信息

3. 静态时序分析(STA):

加入了布局布线延迟,更真实的时序分析

4. 版图物理验证:

DRC(设计规则检查)、LVS(版图一致性检查)

工具:

Mentor:Calibre

Synopsys:Hercules

Cadence:Diva/dracula

5. 生成GDSII文件,Tap_off 流片

(注:整个IC设计流程都是一个迭代的过程,每一步如果不能满足要求,都要重复之前的过程,直至满足要求为止,才能进行下一步。)

IC设计流程相关名词梳理(含各流程EDA工具梳理)

欢迎加入【全栈芯片工程师】知识星球,手把手教你设计MCU、ISP图像处理,从算法、前端、DFT到后端全流程设计。

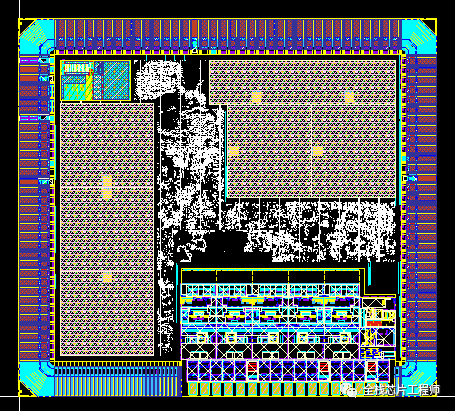

实战MCU+ISP图像处理芯片版图

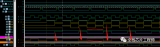

实战ISP图像算法效果

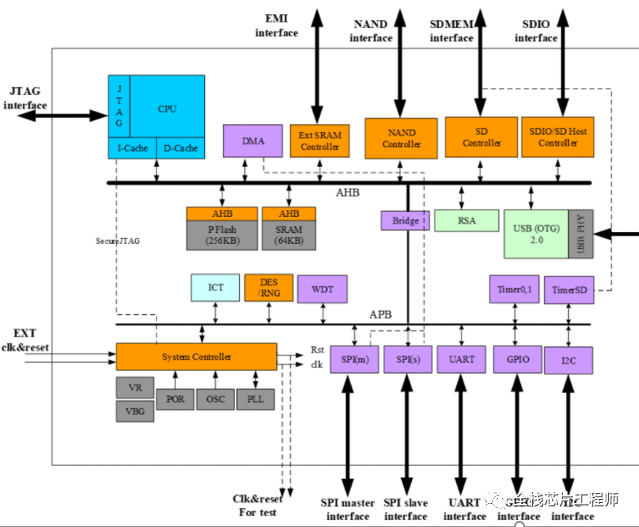

知识星球发起MCU项目启动,大家一起参与MCU项目规格启动讨论,我把设计、验证、DFT、后端的知识点全部罗列出来,大家一起来完善。

以项目驱动的方式介绍MCU芯片全流程设计的方法;提炼相关的检查列表、signoff checklist的样本;让星球成员熟悉SoC架构、设计流程、开发进度、项目管理;

-

寄存器

+关注

关注

31文章

5308浏览量

119980 -

封装

+关注

关注

126文章

7767浏览量

142700 -

MCU芯片

+关注

关注

3文章

246浏览量

11381

原文标题:ASIC设计流程

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

EDA全流程的重要意义,以及国内EDA全流程进展

无线充电器方案XS016MCU+全桥/半桥驱动芯片

建立完善的硬件设计全流程解决方案

MCU芯片全流程设计的方法

MCU芯片全流程设计的方法

评论