现在,工程师比以往任何时候都更多地选择基于碳化硅 (SiC) 的产品,因为它们比基于硅 (Si) 的组件具有更高的效率、功率密度和更好的整体系统成本效益。除了SiC和Si之间常见的基本设计原则,以及需要牢记SiC的不同特性、功能和优势之外,工程师还必须进行建模和仿真,以确保它们能够满足其设计目标。

与硅一样,SiC现在拥有来自各种供应商的优化工具和模型,并且可以应用标准建模缓解措施。虽然LTSpice、PLECS和Wolfspeed的SpeedFit 2.0设计模拟器™等工具之间存在差异,但Wolfspeed的电源专家的提示将有助于实现SiC的仿真精度。

使用 LTSpice 进行静态仿真

Wolfspeed 的 Spice 型号针对 25ºC 和 150ºC 进行了优化。体二极管操作针对驱动电压 VGS进行了优化,第 4 代器件为 -3 V,第 5 代器件为 -2 V。工程师可以结合自发热和瞬态热能力以及寄生电感。然而,没有对寄生双极性和相关效应、雪崩倍增过程以及体二极管导通电压随栅极到源极的变化进行建模。

LTSpice 静态仿真结果(各种 VGS 值下的 IV 曲线和体二极管曲线)与实际测量结果非常吻合。对于电容 — 输入电容 Ciss、输出电容、Coss 和反向传输电容 Crss,静态仿真结果也相当接近。因此,工程师可以对Spice建模的静态参数充满信心。

双脉冲测试

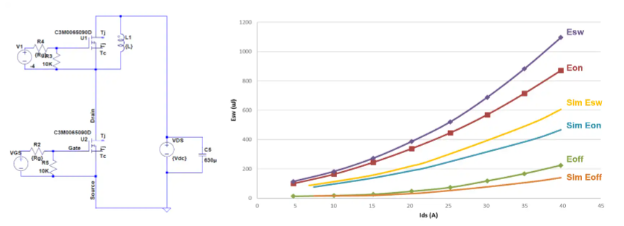

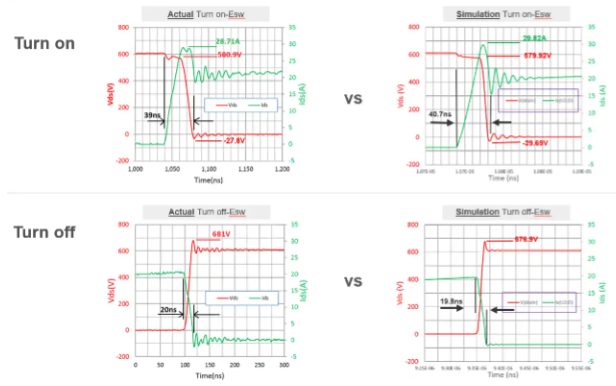

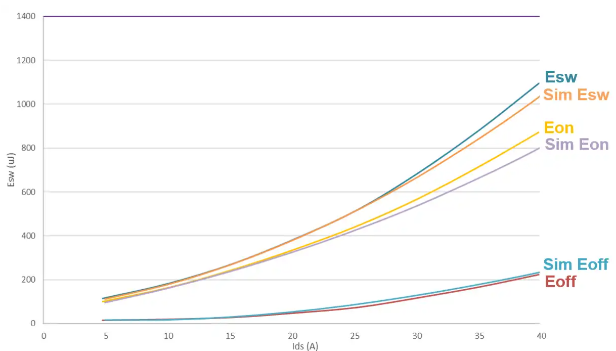

了解动态行为的典型表征基准是半桥双脉冲测试。在没有任何考虑寄生效应等因素的情况下进行建模时,仿真结果明显偏离测量结果(图 1)。由于能耗会影响效率,因此如此大的差异会对热计算产生重大影响。

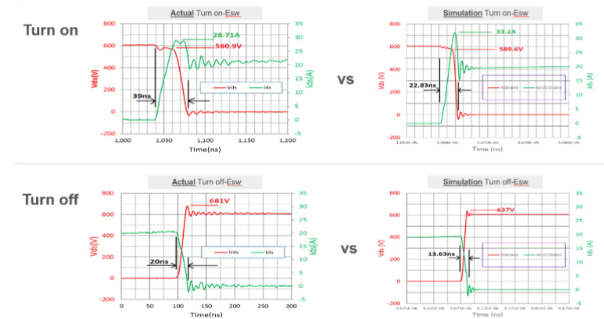

在测试用例中,长脉冲后跟1 μs间隙,后跟短脉冲。导通和关断以传统方式测量,就像使用硅基器件一样。仔细观察波形(图2)可以发现实际仿真结果和理想仿真结果之间的差异。

图1:理想的双脉冲测试仿真开关损耗结果比DUT、U45数据表中的结果低约2%。

仿真中的上升和下降时间都比测量的要快得多,因为实际结果受电感的影响——两个器件之间的寄生杂散电感Lm和封装电感Lpkg,即封装的源极电感。开启和关闭的过冲结果也存在差异。这些差异导致了开关损耗的总体差异。

图2:波形比较显示,实际导通上升时间为39 ns,模拟上升时间为22.83 ns,实际下降时间为20 ns,仿真为13.63 ns。

为了获得精确的模型,必须提取电感并将其手动导入LTSpice。另一方面,PLECS中的热模型不包括寄生元件。

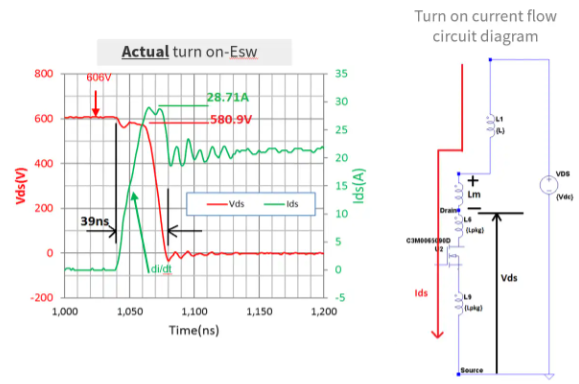

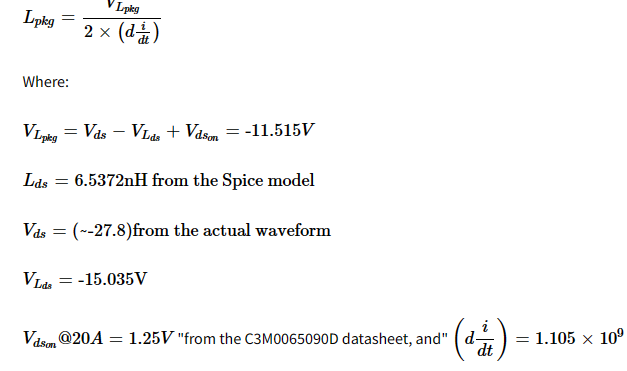

图3:从实际波形中提取的信息可用于计算Lm

发现 Lm

Lm是高边U1器件的源极和低边U2器件的漏极之间的电感。虽然可以直接测量,但也可以这样提取(图3):

这给出了 Lm 的值为 23.1674 nH

无论是同步降压、同步升压、半桥还是全桥,该设计都可能通过PCB配置高端和低端器件。如果遵循良好的布局实践,Lm 在 20 nH 至 25 nH 范围内。工程师可以将其视为在仿真中使用的经验法则。

提取升包

设计人员可能希望 Lpkg 在标准封装(如 TO-247)的供应商中是相同的。但是,由于引线框架的厚度、源极引线键合和封装肩部长度的差异,存在差异。如果数据表中可用,则可以轻松将其插入模型。如果没有,则可以从测量波形中提取它,并外推到手头封装的良好估计值。

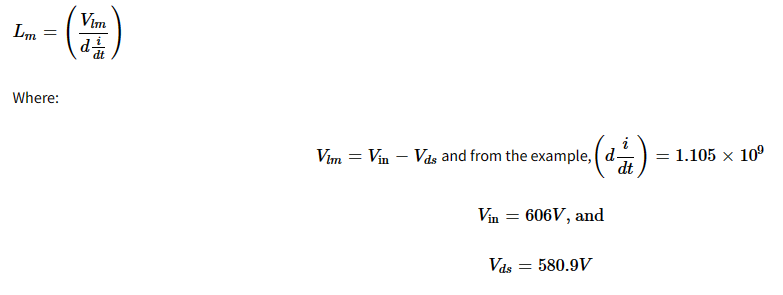

图4:将计算出的电感添加到LTSpice模型中,使其接近实际测量值

在我们的示例中,这给出了 Lpkg 值为 2.503 nH。尽管存在变化,但该值可以被视为一个很好的估计和可靠的经验法则。在考虑电感后进行仿真可使动态模型准确(图 4)。

图5:使用设置寄生效应后,仿真开关损耗与C3M0065090D数据手册相匹配。

考虑到电感,实际和模拟双脉冲测试的总开关能量Esw以及Eon和Eoff变得非常接近(图5)。

使用这些 Lm 和 Lpkg 的经验法则,工程师可以对其热预算进行相当准确的损耗和热计算。

并联 MOSFET

SiC MOSFET通常并联放置,以提高载流能力和功率水平。但是,有一些注意事项需要牢记:

寄生电感不对称导致的电流不平衡

栅极驱动振荡

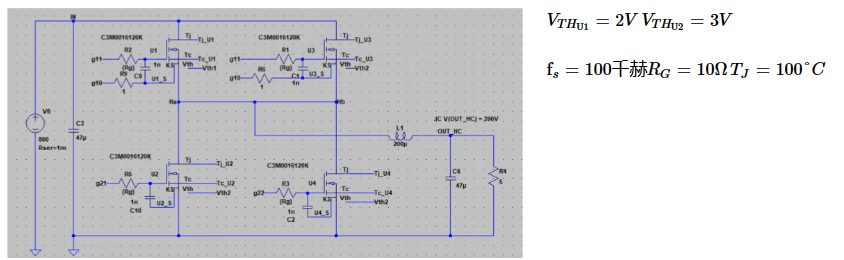

使用Wolfspeed SiC MOSFET,器件特性不匹配的可能性很小。但是,工程师可能需要使用其他规格公差更宽的SiC器件,并且可能会选择具有2 V VTH的器件和另一个具有3 V的器件。具有较低阈值的器件具有较高的瞬态,因此,开关损耗和导通损耗较高,因此总功率损耗较高(图 6)。

图6:由于电流不平衡,2 V器件的总损耗几乎是3 V器件的两倍。

| 参数 | 场效应管 U1 | 场效应管 U3 |

|---|---|---|

| VTH(V) | 2 | 3 |

| i有效值(A) | 29.821 | 25.745 |

| iDC(A) | 21.11 | 18.69 |

| EON(μJ) | 1011.5 | 609.77 |

| E关闭(μJ) | 986.29 | 405.58 |

| E总计(μJ) | 1997.79 | 1014.35 |

| 总损失 (W) | 216.53 | 115.87 |

具有较低阈值电压的 MOSFET

瞬态和静态期间电流较高

更高的开关损耗、更高的传导损耗和总功率损耗

尽管两款器件具有相同的栅极电阻RG,并且在相同的温度和开关频率下工作,但不考虑任何因素的建模导致U1的总损耗超过200 W,U3的总损耗略高于100 W。 仿真波形显示,U1在降至70 A的稳定状态之前峰值约为50 A的过冲, 而U3峰值约为49 A,稳定状态为30 A。因此,两个器件之间的载流能力存在相当大的不匹配,并且导通和关断时间略有不同。

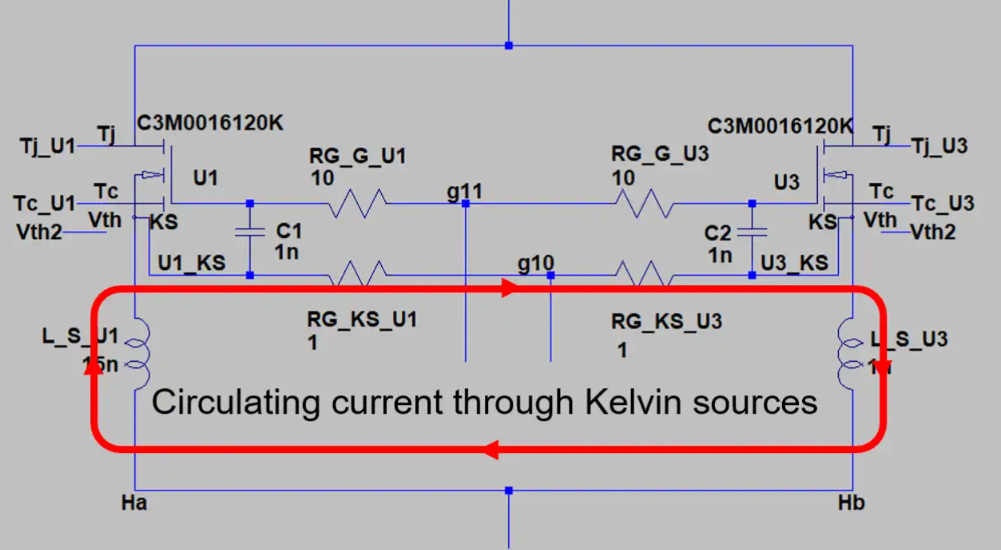

电流不平衡的第二个原因是不对称寄生效应。考虑两个器件,U1和U3(图7),它们的VTH相同,但源极电感不同。这会导致di/dt、杂散电感两端的电压、栅极驱动和漏极电流相当不平衡。仿真波形显示,U3的电流上升和下降速度要快得多,而IDC和IRMS的电流上升和下降速度要快得多,导致该MOSFET的开关损耗增加17.9%,总损耗增加18.3%。

图7:在本例中,U1和U3的杂散电感Ls的差异被夸大了,以证明失配的影响。

| 参数 | 场效应管 U1 | 场效应管 U3 |

|---|---|---|

| VTH(V) | 3 | 3 |

| Stray Ls(nH) | 15 | 1 |

| i有效值(A) | 26.437 | 28.857 |

| iDC(A) | 18.523 | 20.231 |

| EON(μJ) | 391.85 | 1151.6 |

| E关闭(μJ) | 974.05 | 459.02 |

| E总计(μJ) | 1365.9 | 1610.62 |

| 总损失 (W) | 153.21 | 181.29 |

通过良好的设计减少不匹配

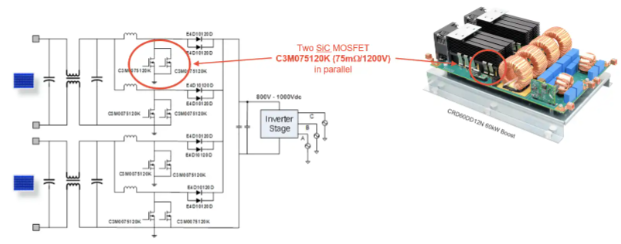

通过采用良好的设计实践,可以大大减少不匹配的MOSFET的影响。例如,以 60 kW 太阳能逆变器升压参考设计 CRD60DD12N 为例,该设计并联使用两个 75 mΩ 1,200V C3M075120K MOSFET(图 8)。如果采用良好的设计实践,则使用来自 247 个器件样本的 TO-4 60 引脚 MOSFET 中的两个具有最高和最低 VTH 的 TO-<> MOSFET,仍然可以实现运行良好的硬件。

图8:尽管存在VTH差异,但该测试电路中器件失配的影响降至最低。

| 参数 | 问1 | 问2 |

|---|---|---|

| VTH(V) | 3.006 | 2.666 |

| RDS_ON(mΩ) | 81.82 | 67.96 |

| i有效值(A) | 3.64 | 4.01 |

从 60 个样品中挑选出两个具有最高和最低 VTH 的零件

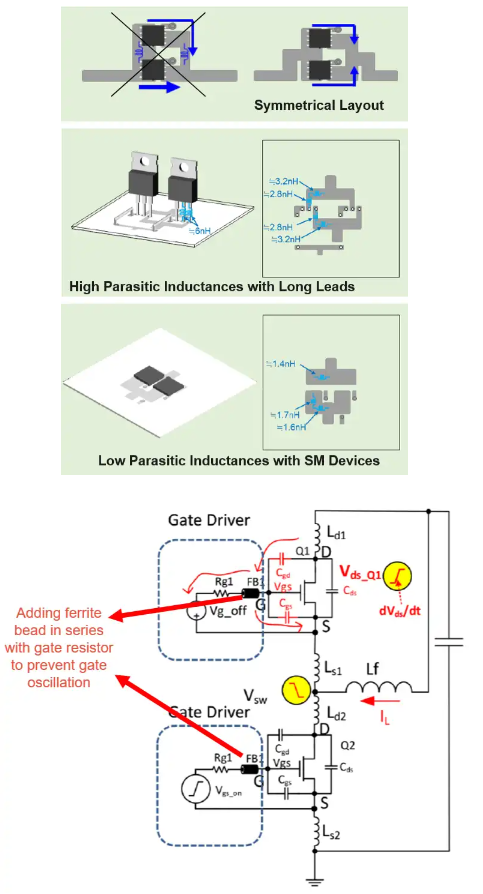

对称的PCB布局对于降低并联开关栅极环路中的环流至关重要。将电源环路与栅极环路分开,提供足够的阻尼以防止栅极振荡,并在栅极支腿处添加铁氧体磁珠,以减少可能导致部件损坏的栅极上的电压尖峰和振铃(图 9)。

图 9:良好的设计实践 – 紧密对称布局、平衡信号、电源和栅极环路分离、防止栅极振荡的阻尼以及带有铁氧体磁珠的小 RG 以减少振铃 – 所有这些都可以减少电流不平衡。

由于这些设计实践,测试电路中的Q1承载总电流的47.6%,而Q2承载52.4%,尽管器件不匹配,但仍达到可接受的实际结果。

增加刀具选择

基于 SiC 的设计可以使用 Wolfspeed 的 SpeedFit、LTSpice 或 PLECS 进行建模。虽然SpeedFit和LTSpice可以通过注册Wolfspeed自由使用,但PLECS需要支付订阅费。工具之间的差异既影响了生成仿真的方式,也影响了它们的局限性,例如在处理寄生效应和计算损耗方面。

审核编辑:郭婷

-

二极管

+关注

关注

149文章

10484浏览量

179953 -

MOSFET

+关注

关注

152文章

10886浏览量

235356 -

SiC

+关注

关注

32文章

3908浏览量

70321

发布评论请先 登录

使用Wolfspeed碳化硅MOSFET对常见拓扑进行建模

使用Wolfspeed碳化硅MOSFET对常见拓扑进行建模

评论