大家好!今天给大家分享的是4位计数器的代码以及仿真程序。

4位计数器代码:

module count4(out,reset,clk); output [3:0] out; input reset,clk; reg [3:0] out; always @( posedge clk) begin if (reset) out<=0; // 同步复位 else out<=out+1; // 计数 end endmodule

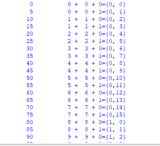

4位计数器的仿真程序:

`timescale 1ns/1ns `include " count4.v " module coun4_tp; reg clk,reset; // 测试输入信号定义为 reg 型 wire [3:0] out; // 测试输出信号定义为 wire 型 parameter DELY=100; count4 mycount(out,reset,clk); // 调用测试对象 always #(DELY/2) clk = ~clk; // 产生时钟波形 initial begin // 激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end // 定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule

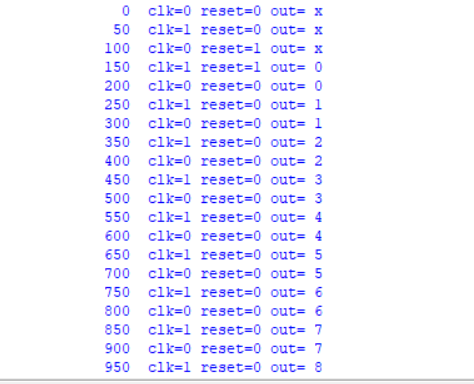

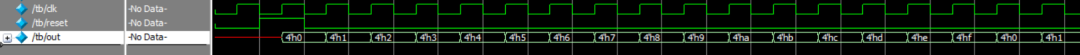

modelsim仿真结果:

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21729浏览量

602978 -

仿真

+关注

关注

50文章

4070浏览量

133552 -

计数器

+关注

关注

32文章

2256浏览量

94476 -

程序

+关注

关注

117文章

3785浏览量

81002 -

代码

+关注

关注

30文章

4779浏览量

68521

原文标题:4位计数器代码及仿真程序

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

用于4位计数器的SDK C程序怎么写

嗨好朋友,我正在研究4位计数器我已经创建了IP以及框图设计。现在停止使用SDK c程序启动硬件。这是我在HLS中的反击#include #include“ap_int.h”#defin

发表于 05-19 12:18

1602液晶的6位计数器程序

;******************************;1602液晶6位计数器:本程序调试通过 *;************************************;* 硬件:此

发表于 04-21 22:44

•57次下载

基于Multisim的计数器设计仿真

计数器是常用的时序逻辑电路器件,文中介绍了以四位同步二进制集成计数器74LS161和异步二-五-十模值计数器74LS290为主要芯片,设计实现了任意模值

发表于 07-26 11:38

•134次下载

基于Proteus的任意进制计数器设计与仿真

提出一种基于Proteus 软件的任意进制计数器的设计。以74LS163 集成计数器为基础,用置数法设计了两种48 进制计数器,采用Proteus 软件对计数器进行

发表于 07-29 18:53

•0次下载

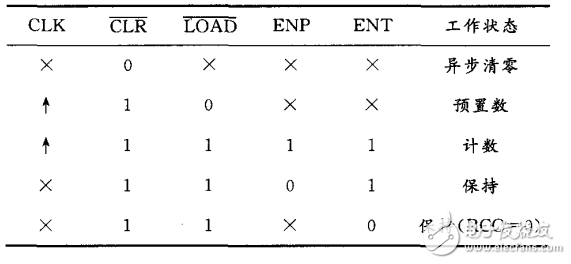

计数器74LS161的Multisim仿真

本文主要介绍了计数器74LS161的Multisim仿真。74LS161是具有异步置零、计数、预置数和保持功能的可编程集成中规模同步4位二进

发表于 01-17 18:19

•6.6w次阅读

上百个Verilog HDL的程序设计实例代码合集免费下载

本文档的主要内容详细介绍的是上百个Verilog HDL的程序设计实例代码合集免费下载包括了:4 位全加器,4

发表于 08-02 17:11

•73次下载

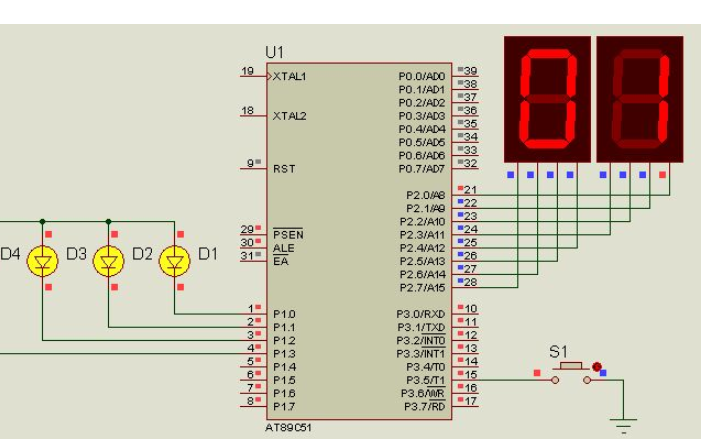

四位计数器的程序和电路图及仿真等资料合集免费下载

本文档的主要内容详细介绍的是使用两个按键实现加一减一的四位计数器的程序和电路原理图及仿真等资料合集免费下载 。

发表于 09-09 08:00

•2次下载

基于FPGA的十进制计数器

本方案是一个基于 FPGA 的十进制计数器。共阳极 7 段显示器上的 0 到 9 十进制计数器,硬件在 Xilinx Spartan 6 FPGA

发表于 12-20 14:52

•2次下载

FPGA设计:4位计数器代码及仿真程序

FPGA设计:4位计数器代码及仿真程序

评论