碳化硅 (SiC) 是一种成熟的器件技术,在 900 V 至 1,200 V 以上的高压、高开关频率应用中,与硅 (Si) 技术(包括硅超结 (SJ) 和绝缘栅双极晶体管 (IGBT) )相比具有明显的优势。1 最近推出的 650 V SiC MOSFET 产品通过轻松取代 IGBT、从 Si SJ 应用领域中脱颖而出,并在中压范围内提供氮化镓 (GaN) 的替代品,进一步扩大了 SiC 的使用范围。

当用SiC替换Si器件或使用SiC重新设计时,工程师必须考虑SiC的不同特性、功能和优势,以确保成功。以下是来自 Wolfspeed 电源专家的 SiC 设计技巧列表。

RDS(ON) 随温度的变化

SiC 的一个关键优势是低 RDS(ON),在很宽的温度范围内变化仅为 1.3× 至 1.4×而在硅或 GaN 器件中,RDS(ON) 可能会从 25°C 时的额定温度增加到 120°C 至 140°C 范围内的实际结温的两倍到三倍(图 1)。因此,仔细检查数据表并指定正确的I2R或传导损耗非常重要。

图1:60 mΩ Si或GaN器件的热>为120 mΩ,而90 mΩ SiC器件的热度为120 mΩ。

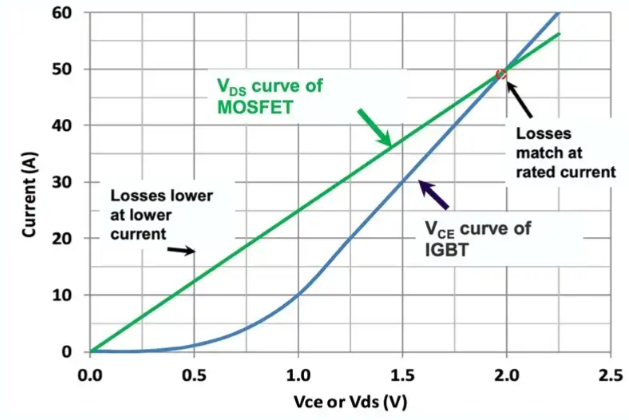

无膝电压

IGBT针对全额定电流下的热设计点进行了优化。低于该点的是VCE(sat)指数“拐”电压曲线(图2)。碳化硅 MOSFET 的 VDS 特性是线性的,在低于全额定电流的任何点均提供较低的导通损耗。

在设计电动汽车传动系统时,这一点特别有用,因为其中驱动循环大多低于全额定功率。当并联使用时,IGBT VCE(sat)曲线加剧了这个问题。

因此,设计人员必须仔细考虑其热设计点和任务概况。

图2:Tj = 50°C 时模块中 50 A IGBT 与 150 A SiC MOSFET 的比较。 在三分之一额定电流下,SiC的损耗是IGBT的一半。

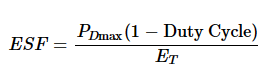

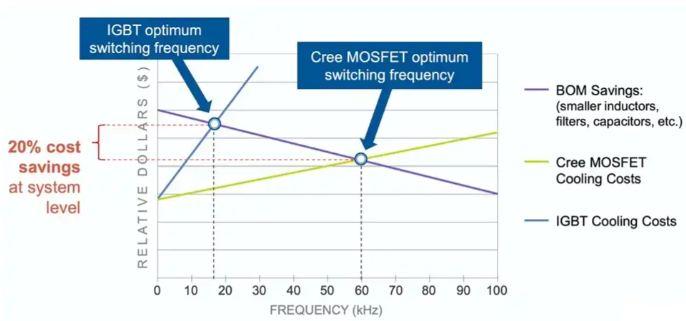

有效开关频率

有效开关频率 (ESF) 定义为硬开关应用中器件在额定I C100 下可以承受的最大频率,方波占空比为 50%,而不会超过器件在工作电压下规定的最大功耗。艺术

其中:

有效开关频率(ESF)定义为硬开关应用中器件在额定IC100下可以承受的最大频率,方波占空比为50%,而不会超过器件在工作电压下规定的最大功耗。艺术

图3:频率优化考虑了冷却开关频率的实际限制和物料清单成本。

与40 mΩ硅器件相比,40 mΩ Wolfspeed SiC MOSFET的理论ESF高10×。虽然这让我们得以一窥SiC的功能,但冷却、磁性和成本对开关频率造成了实际限制。

冷却成本增加,但电感器和电容器的无源BoM成本随着开关频率的降低而降低。对于IGBT,最佳频率约为18 kHz,冷却和无源BoM节约曲线在此相交。对于导通损耗较低的 SiC MOSFET,成本权衡的最佳点约为 60 kHz(图 3)。

设计人员必须注意,最小化电感是有限制的,特别是当系统连接到电网时。虽然SiC器件本身比IGBT更昂贵,但频率优化设计可在系统级节省20%至25%的成本。

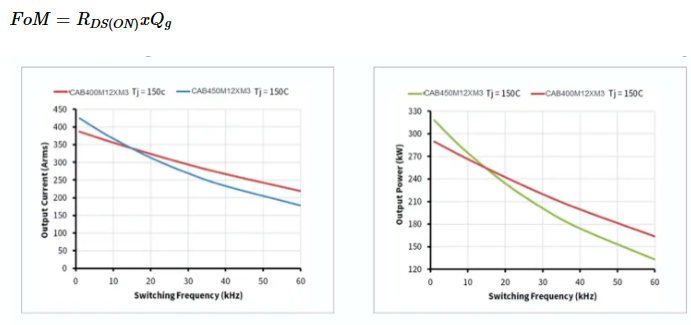

针对应用程序进行优化

MOSFET 的品质因数 (FoM) 由以下公式定义。其背后的想法是,较低的RDS(ON)意味着较低的传导损耗,而较低的栅极电荷Qg意味着较低的开关损耗。如果他们的产品FoM最小化,总损失就会最小化。

图4:对于此概念示例,Fsw 为 15 kHz。在分频点之后,CAB400M12XM3可以提供比CAB450M12XM3更高的安培数。

通过检查 Wolfspeed 两个功率密度最高的功率模块的输出电流和输出功率与开关频率特性,设计人员必须如何仔细选择适合其应用的最佳产品(图 4)。450 A CAB450M12XM3 模块针对极低的 RDS(ON) 进行了优化,但 400 A CAB400M12XM3 模块针对 FoM 进行了优化。超过 15 kHz,400 A 可提供更高的电流和更高的功率。

对于通常在 20 kHz 以下运行的电机驱动器,高安培数模块是有效的,但对于在 48 kHz 至 60 kHz 范围内切换的太阳能逆变器,400 A 模块是更好的选择。

VDS 坚固性和降额

IGBT的额定电压通常为1.2 kV,VDS击穿电压接近1.25 kV。Wolfspeed 的 SiC MOSFET 额定电压为 1.2 kV,但击穿电压通常高出数百伏。在航空航天应用中,设计人员必须降额以考虑宇宙辐射的影响,SiC的鲁棒性提供了优势。

反向恢复

在软开关或使用非对称设计时,设计人员可能不会太关注它,但反向恢复(Qrr)对于对称设计非常重要,包括降压、升压和图腾柱PFC。Wolfspeed 650 V SiC MOSFET 在反向恢复时间 T rr 为 11 ns 时具有 16 nC Q rr,而典型的 650 V Si MOSFET 在 T rr 为 13 ns 时具有 725 μC Q rr。

开尔文源极引脚

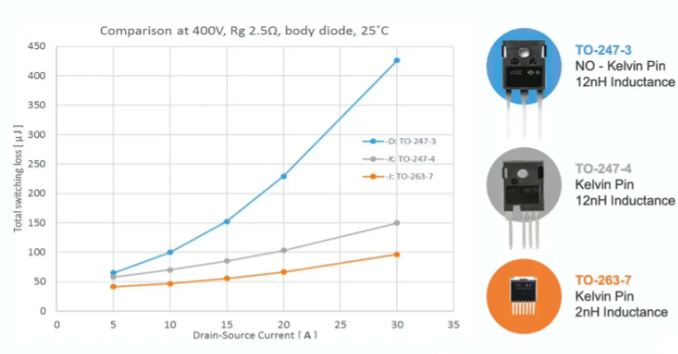

开尔文源极引脚(尽可能靠近 MOSFET 芯片源极连接的开尔文连接)用于减轻 MOSFET 内部键合线引起的电感。为了保持SiC器件的高开关频率优势,开尔文源极引脚至关重要。

开尔文源极引脚也会影响开关损耗。例如,在 30 A IDS下,无开尔文引脚和 247 nH 源极电感的 TO-3-12 SiC MOSFET 的总开关损耗接近 430 μJ(图 5)。采用TO-247-4封装的同一产品(带有开尔文源极引脚)在相同的IDS上只有150 μJ的开关损耗。改用更小的封装,如 TO-263-7 或表面贴装 D2PAK-7,可进一步降低固有的源极电感和损耗。

图5:开尔文源极引脚有助于避免栅极驱动器环路中的电感,并减少开关能量损耗。

栅极驱动注意事项

驱动SiC MOSFET时,设计人员必须记住,需要负栅极驱动以确保硬关断,这与硅不同,硅使用正栅极驱动来接通器件。要记住的其他 SiC 特定因素包括:

更快的 dV/dt 和 >100 kV/μs 的额定共模瞬变抗扰度 (CMTI)

峰值连续工作电压 (V IORM) 高达 1.7 kV

驱动能力通常更高功率,最高可达 10 A

传播延迟和通道失配时间通常为 <10 ns

有源米勒箝位要求,因为开关速度更高,2 V时阈值略低

由于 SiC 芯片尺寸较小 (<1.8 μs),可实现快速短路保护

除此之外,驱动SiC器件就像驱动硅基器件一样。

处理电磁干扰

由于SiC器件的目标开关频率通常较高,并且其上升和下降时间远短于Si产品,因此工程师可能倾向于认为这会导致更大的EMI问题。

但是,与Si相比,对所需的低频噪声或差模EMI滤波器尺寸没有影响。虽然对输入端子上的导通模式噪声有影响,但它仅在兆赫兹范围内。与硅基器件一样,这种高频EMI可以通过使用高频材料和电容器进行EMI抑制来衰减。

应用范围广

如今,SiC 器件用于从 200 kW UPS、180 kW 电动汽车传动系统和 10 kW 太阳能逆变器到 220 W LED SMPS 等各种应用,所有这些应用均在设计时牢记一些 SiC 设计考虑因素和通常的良好设计原则。

审核编辑:郭婷

-

IGBT

+关注

关注

1267文章

3802浏览量

249296 -

晶体管

+关注

关注

77文章

9703浏览量

138443 -

碳化硅

+关注

关注

25文章

2780浏览量

49112

发布评论请先 登录

相关推荐

碳化硅电源的设计注意事项

碳化硅电源的设计注意事项

评论