《Innovus教程 - 输出用于LVS的Verilog网表文件 各种控制选项》

输出用于LVS的Verilog网表文件

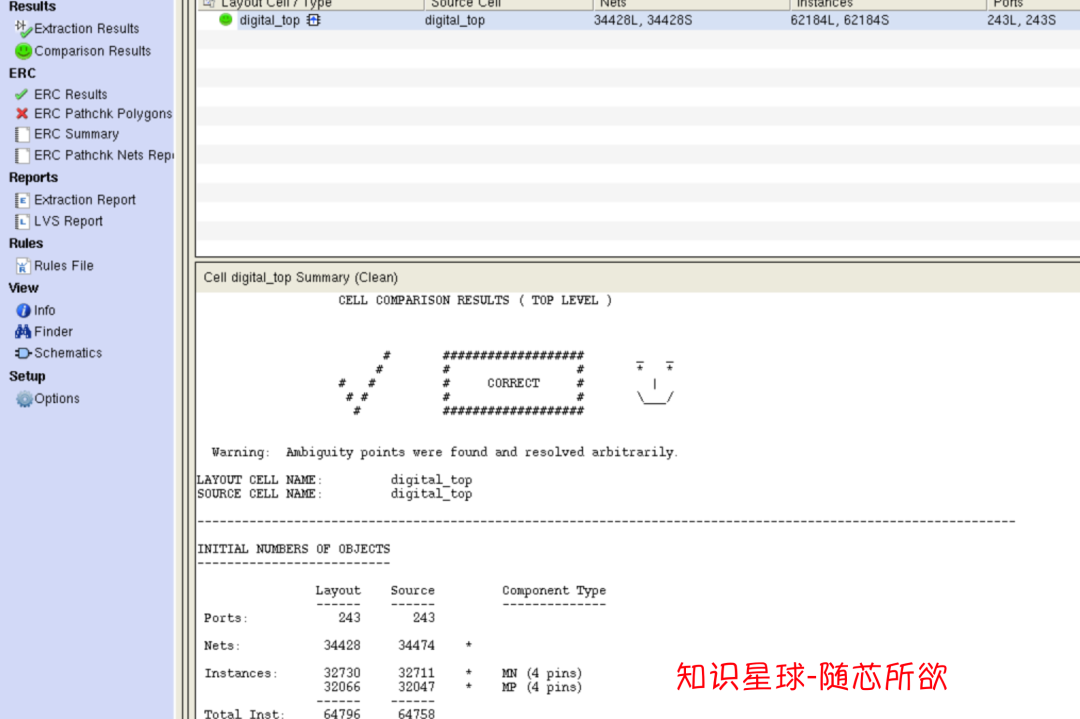

如何导出Verilog网表用于Calibre做LVS?

命令:

deleteEmptyModule

saveNetlist

-includePhysicalCell $FILLER_CELL_WITH_METAL

./dataout/$DESIGN_NAME.output.lvs.v

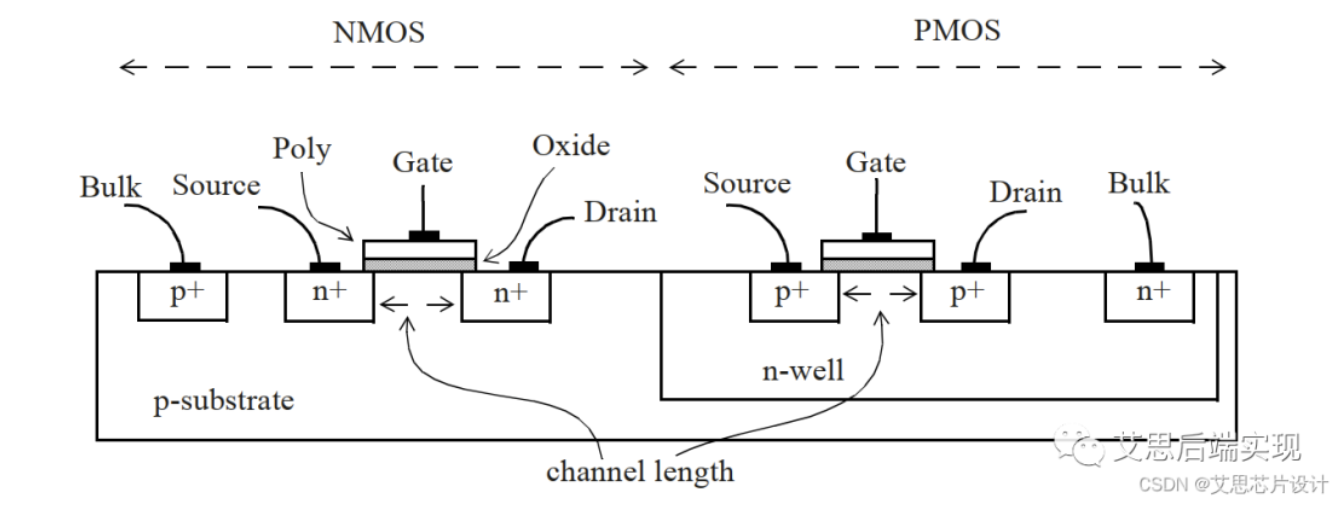

这里的$FILLER_CELL_WITH_METAL主要指的是Decap这种有MOS管的Physical Only Cell,当然如果有其他的Physical Only Cell,内部有MOS管的,也是要加进去的。更多LVS相关细节在网易云课堂视频教程中有讲解。

网易云课堂有PV的视频教程,这些学会之后没有什么难解的PV问题,知识星球成员的话还有8折优惠哦,直接联系我或者在星球里面留言就能获得优惠券:

Calibre DRC版图物理验证教程

https://study.163.com/course/introduction.htm?courseId=1006290023&_trace_c_p_k2_=6566144eb10f47299d45efc1de21d086

Calibre LVS ERC教程--一键搞定

https://study.163.com/course/introduction.htm?courseId=1209591919&_trace_c_p_k2_=20ea4d25b2d84d75b93c74392ea0798b

扩展1 - 如何/为什么要删除空的Module?

有时候网表中可能会有一些空的module(在网表中体现为Module下面没有Cell或者准确说没有含MOS管的有效器件),而它们在版图里面也是不存在的,因此LVS的时候会报source里面能找到,但是版图里面没有找到。为了解决这个问题,可以在导出网表前输入下面的命令来删除这些空module:

deleteEmptyModule

扩展2 - 如何在网表中导出某种Physical only的Cell?

如果Design中有任何Physical only的Cell,它们实际上内部是有MOS管的,那么导出网表的时候都需要用-includePhysicalCell来把它们导出(这里用变量$PO_CELLS_WITH_MOS来表示),否则会报版图里面能找到它们,而Source里面没有的问题:

saveNetlist -includePhysicalCell "$PO_CELLS_WITH_MOS"

../IOs/$DESIGN_NAME.output.lvs.v

除了前面说过的Decap你可以想一想还有哪些内部有MOS管的Physical Only Cell需要导出。

扩展3 - 如何在导出的网表中split bus?

如果Design里面有Macro,比如SRAM,在SRAM的.sp网表中所有的pin都是单个bit声明的,那么在导出网表的时候我们必须把Bus来flatten成单个的bit,加上选项-flattenBus即可,否则在做完v2lvs之后做LVS的时候会这些bus和pin不匹配的问题。

saveNetlist -includePhysicalCell "$PO_CELLS_WITH_MOS"

-flattenBus

../IOs/$DESIGN_NAME.output.lvs.v

扩展4 - Innouvs是否会把Floating的output pin导出到网表?是否影响LVS结果?

......

更多完整内容见知识星球

......

审核编辑 :李倩

-

MOS管

+关注

关注

108文章

2411浏览量

66782 -

Verilog

+关注

关注

28文章

1351浏览量

110085 -

LVS

+关注

关注

1文章

36浏览量

9942

原文标题:Innovus教程 - 输出用于LVS的Verilog网表文件 各种控制选项

文章出处:【微信号:集成电路设计及EDA教程,微信公众号:集成电路设计及EDA教程】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于深亚微米VLSI的物理验证可实现加快芯片研发速度

EDIF网表实施错误

如何为后综合模拟和/或后PAR网表模拟生成VHDL或Verilog网表?

write_vhdl与write_verilog有什么差异?

如何使用Icarus Verilog+GTKWave来进行verilog文件的编译和仿真

DS75LVS+ DS75LVS+ - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

DS75LVS+T&R DS75LVS+T&R - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

MCU项目innovus中get_db使用

VCS编译选项:-y及+libext+

物理验证LVS对bulk(体)的理解和处理技巧

Innovus教程:输出用于LVS的Verilog网表文件 各种控制选项

Innovus教程:输出用于LVS的Verilog网表文件 各种控制选项

评论