1. class内容

class里面包含data和对data进行操作的subroutines(functions and tasks)。class的data称为class properties,subroutines称为methods。两者都是class的members。

class相当于是定义了一个data type。object是该class的instance。Object handle是持有该class type的变量。

class里的method的lifetime必须为automatic,如果定义成static是非法的(这里不是指static task,而是task内static的variables或arguments)

2. class构造函数

systemverilog提供了class的构造函数,支持在创建object的时候对instance进行初始化。

如果用户没有显示指定new方法,那么隐藏的new方法将会被自动加上。在子类的new方法里应该首先call父类的new构造函数。

super.new需要在子类构造函数中第一条语句就执行,这是因为superclass需要在子class之前被初始化,如果用户没有提供superclass的初始化,那么compiler会自动插入super.new。

3. static

class中的static properties可以直接引用,不需要该通过class的instance。

class中的methods也可以是static,static method不能访问non-static members(properties或methods),但它可以访问同个class内的static members。如果它访问了non-static members或this handle,那么应该报编译错误。Static methods也不能是virtual。

Static method和task with static lifetime是不一样的,前者描述的是class内method的lifetime,而后者描述的是task内variables和arguments的lifetime。

4. shallow copy和deep copy

Shallow copy只是复制原有object的properties,但如果原有object里含有object handler,也只是复制handler的值,不会把handler object里的properties也进行复制。

Shallow copy也不会创建新的coverage objects(covergroup instances)。

如果要做到连handler里的properties都复制,那么需要deep_copy,deep copy需要user自己实现的。

5. chaining constructors

如果多层class extend的话,那么在constructor里需要调用父类的constructor。

如果父类的constructor需要arguments,那么有两种方法:1. 用super.new(xx)传进去;2. 在extend父类class时就传进去的,用这种方式,在constructor里就别加super.new(xx)了。

父类的new函数如果不需要arguments(没有参数或参数带默认值),那么在子类constructor里对super.new()可写可不写,不写的话,compiler会自动插入。如果父类的constructor需要传参数,那么compiler自动插入也只是为super.new(),也不会给你传参数值进去的(除非在extend时指定),这样simulator会报错。

记住:如果将new定义为local,那么该类将不可以被继承的。

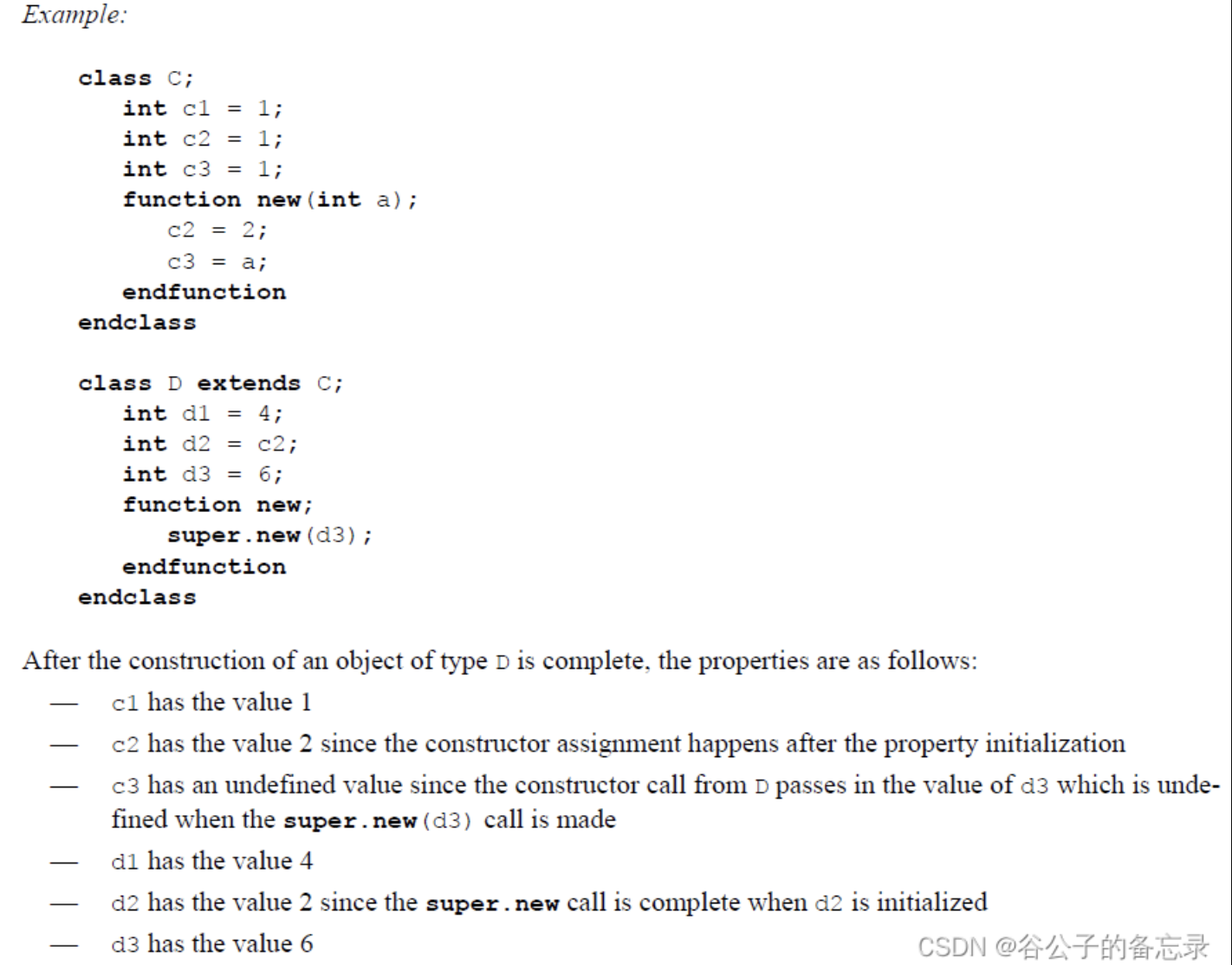

在子类构造函数中需要第一条调用父类构造函数super.new()中,要等super.new()执行完之后,才会做son class的property初始化,如果property有指定初始值,那么就赋值,如果没有指定,那就是undefined的。最后才会继续执行son class构造函数中super.new()以下的语句。因此在给父类构造函数传输参数,如果用子类定义的变量,那么结果会是undefined的,因此,来不及初始化啊。例子如下:

-

Verilog

+关注

关注

28文章

1352浏览量

110520

发布评论请先 登录

相关推荐

[启芯公开课] SystemVerilog for Verification

更好地理解SystemVerilog的多态Polymorphism

SystemVerilog Assertion Handbo

SystemVerilog的断言手册

SystemVerilog语言介绍汇总

SystemVerilog中枚举类型的使用建议

SystemVerilog中$cast的应用

SystemVerilog中的package

Systemverilog中的union

SystemVerilog中class的基本概念

SystemVerilog中class是什么意思

FPGA学习-SystemVerilog语言简介

SystemVerilog里的regions以及events的调度

Systemverilog里class类型的记录

Systemverilog里class类型的记录

评论