本篇继续介绍数电第二章——门电路的相关内容。本章虽然个人感觉重要程度不如之后的几章,但是也是相当重要的一部分,并且学习起来有一定的困难,因此需要对于一些重点部分进行适当的重视。

1考点总结

1.分析所给TTL电路的逻辑(真值表和逻辑式)

2.计算TTL门电路的扇出系数

3.OC门负载电阻的计算

4.分析所给的CMOS电路的逻辑(真值表和逻辑式)

2各考点分析

首先这些电路都是不需要会画的,会分析就行,因此在复习的时候不要花大把的时间去记忆电路图,熟悉熟悉就可以,重点在于分析。

1.TTL门电路

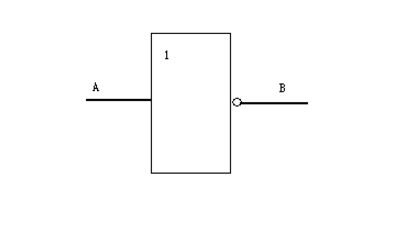

①TTL反相器

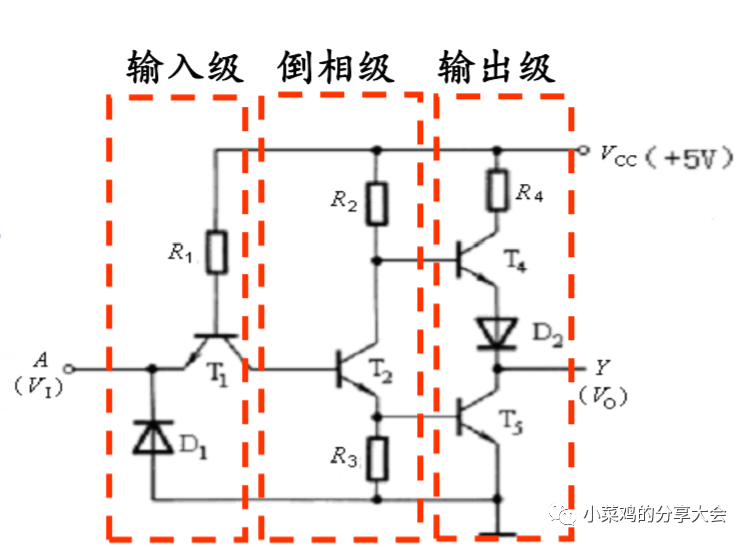

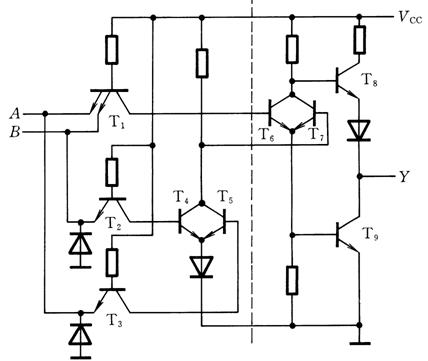

电路如图分为输入、倒向、输出三级。后两级都是我们在模电中就已经熟知的结构,在这里不再赘述。输入级的D1管的作用就是保护,对电路本身没有太大影响。我们在这里给定一定的条件,借以分析。

设:VCC=5VVIL=0.2V,VIH=3.4V,VON=0.7V,R1=4kΩ。(注意这里的VCC=5V,所有的TTL电路的VCC都必须是5V.另外R1=4KΩ也是一个定制,在TTL反相器中一般不改变。)

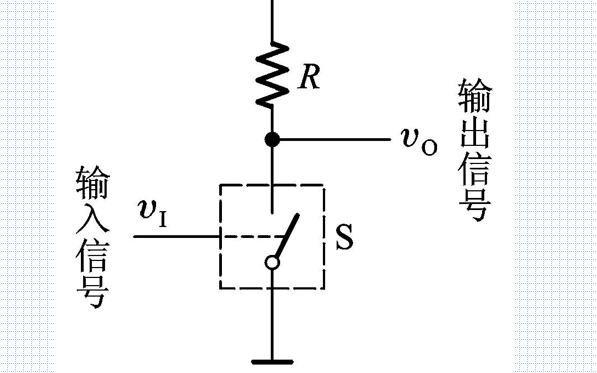

所谓的逻辑分析,就是画真值表,给定输入的高低电平所有情况,观 察对应的输出,并写出逻辑表达式的过程。因此我们分输入的高低电平两种情况讨论:

1>VI=0.2V。

此时的T1管必定导通,因此Vb1被钳位在0.9V.观察c1和b2,这两个电流从理论上讲应当是相反的,因此都等于零。从而可以算出ib1=ie1≈1mA。而Ibs≈0,进而满足了ib1>>Ibs这一深度饱和条件。我们知道深度饱和的条件下,VE=VES<0.3V,这里我们取0.1V,显然T2管是截止的,那么R2是没有大电流流过的,可以认为Vb4处于高电平状态,同理Vb5处于低电平状态,即T4导通,T5截止,Y处于高电平状态。

2>VI=3.4V。

这一情况请读者自行依照上文分析,最后可以得到Y处于低电平状态。

综合上述画出真值表,写出逻辑表达式:

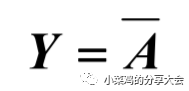

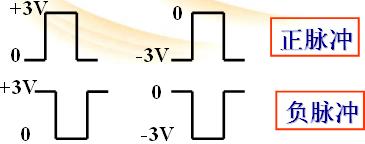

这里必须提到的一点还有TTL反相器的输入伏安特性曲线,如下图。请读者记住图中对应高低电平下的输入电流值,在与非门和或非门的电路分析中需要使用到。

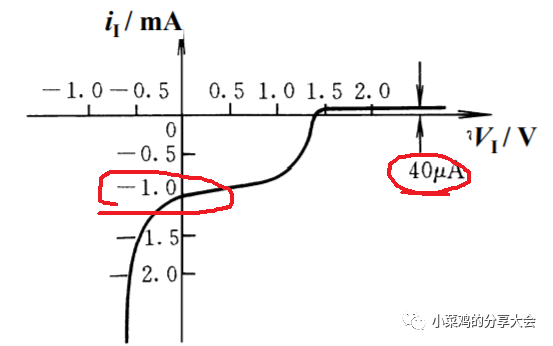

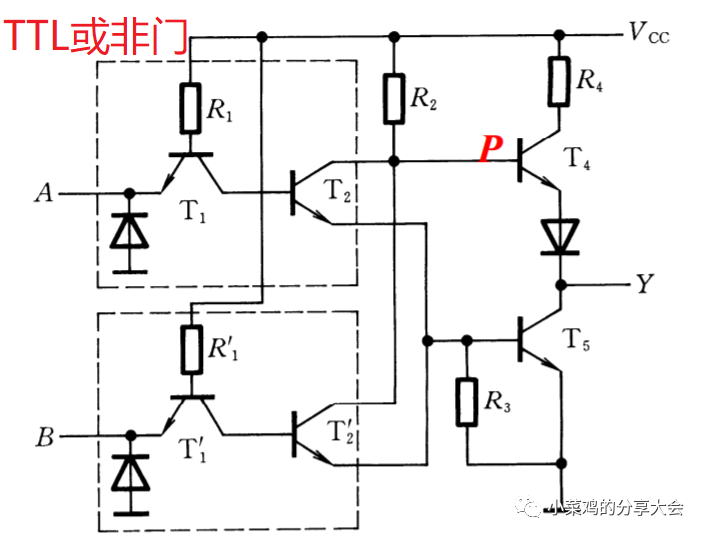

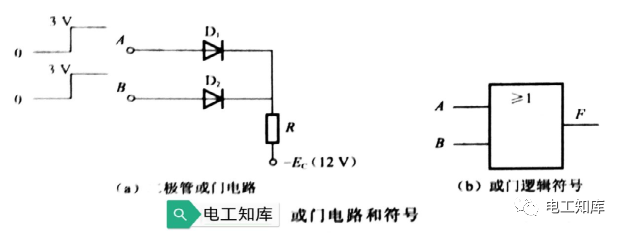

②TTL与非门和或非门

电路图如下:

由于TTL电路的分析过程大同小异,这里就不再做过多的叙述,值得注意的一点是TTL与非门输入级的双输入端结构。这个结构导致与非门在低电平时虽然有两个输入端,但是输入电流依然只有-1mA,而高电平时要按照两个计算,为40*2=80uA。另外在其他计算中,请一定要格外注意与非门和或非门的多输入端结构导致的电流加倍问题,题设一般给的都是一端输入的电流要求。

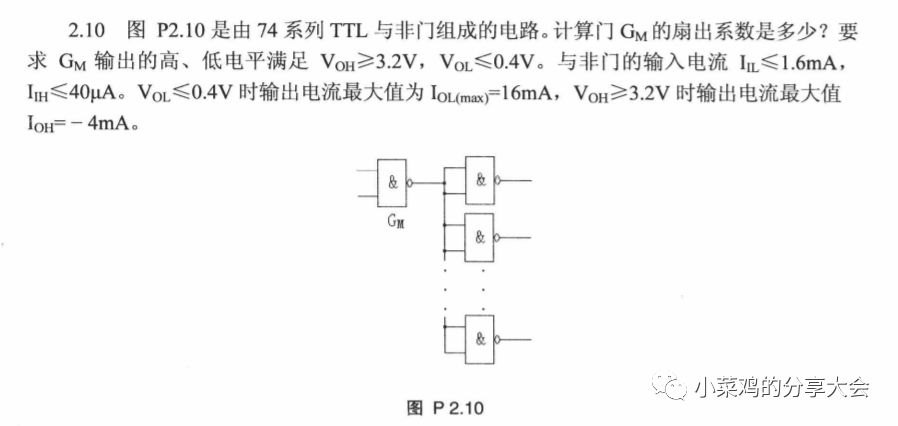

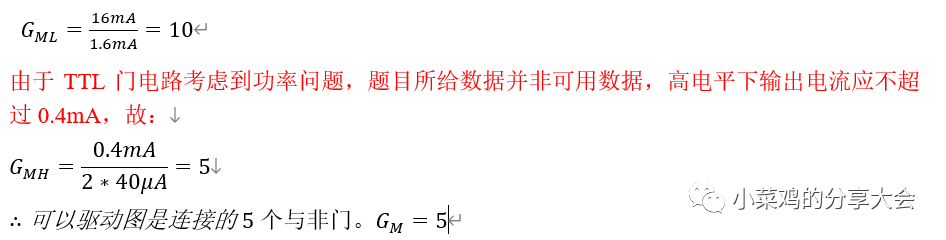

2.TTL门电路的扇出系数计算

扇出系数的定义是:一个TTL门电路可以带动相同门电路的数目。一般是指电流的允许值。这里给出一道例题借以讲述:

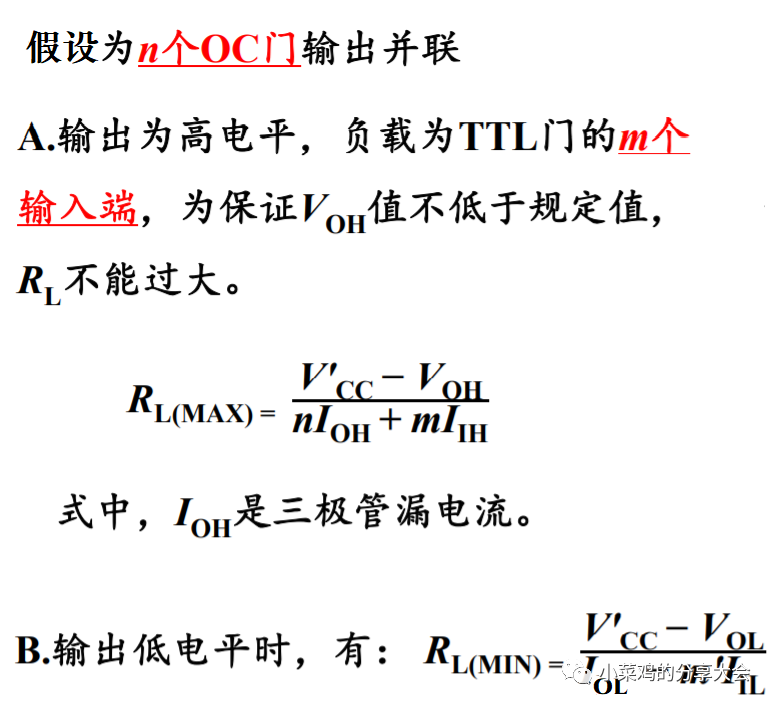

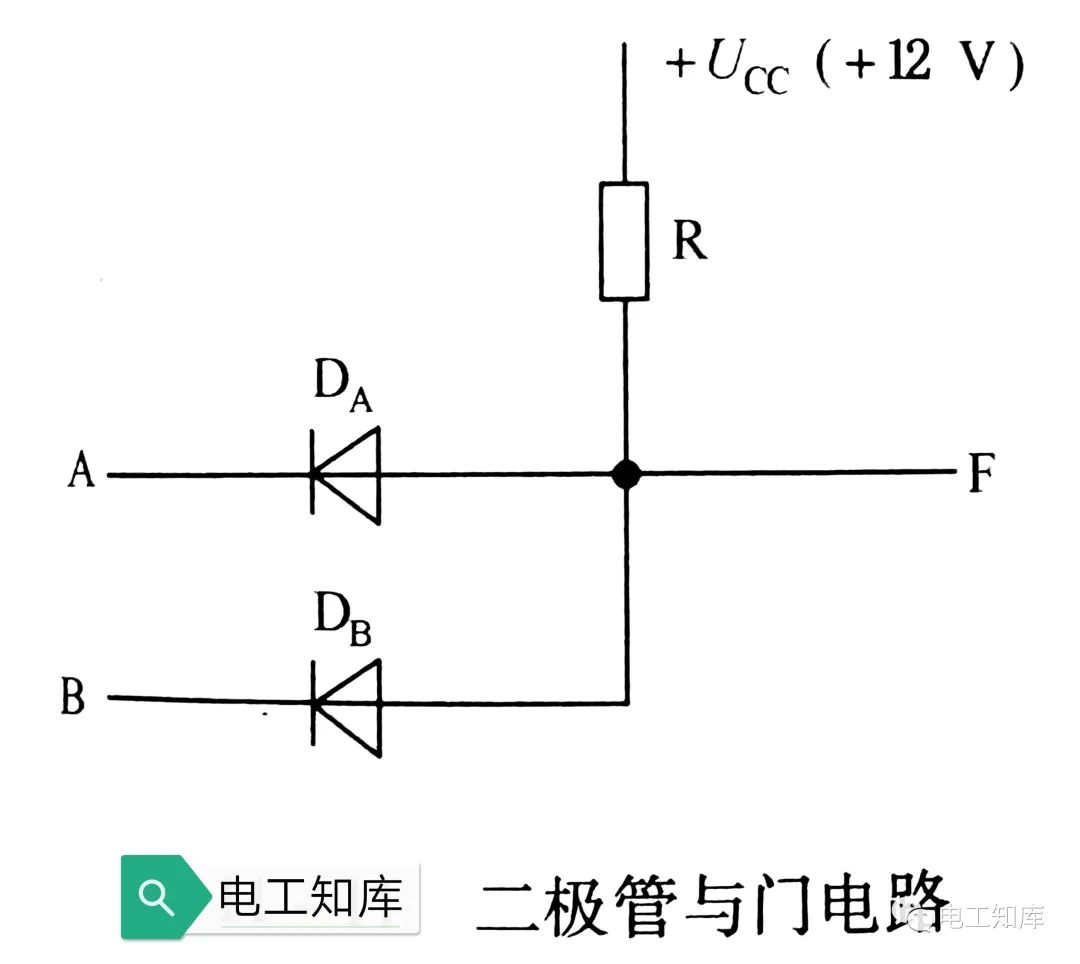

3.OC门负载电阻的计算

OC门即为集电极开路门电路,是为了实现“线与”这个逻辑而存在的一种电路,只要把几个OC门的输出Y直接用导线连在一起,就可以得到这几个输出的“与”逻辑,但是OC门对于负载电阻RL有着严格的要求:

这里需要特别注意,针对与非门,m为输入端数,m'为负载门数;针对或非门,m和m'都是输入端数,这是上文提到的与非门输入电流问题导致的。

4.CMOS集成门电路

CMOS门电路相较于TTL电路简便许多,并且不会存在温漂等问题,分析起来要简单的多,因此实际电路设计中,TTL电路已经逐步被CMOS工艺所替代。由于过于简单,CMOS电路的分析请读者自行学习,这里强调的一点是,请一定要注意COMS电路中NMOS和PMOS的上下位置关系不要颠倒,以及N和P型的电压导通情况不要搞混。

-

CMOS

+关注

关注

58文章

5790浏览量

236602 -

电路图

+关注

关注

10365文章

10726浏览量

534970 -

TTL

+关注

关注

7文章

508浏览量

70678 -

反相器

+关注

关注

6文章

314浏览量

43641 -

门电路

+关注

关注

7文章

200浏览量

40339

发布评论请先 登录

相关推荐

与门电路、或门电路、非门电路及实例

什么是门电路 门电路是什么意思

基本逻辑门电路

门电路作用是什么_门电路有几种电路

门电路的相关知识

门电路的相关知识

评论