作者:Rahul Singhal 和 Giri Podichetty

部署在汽车、医疗和航空航天等安全关键应用中的集成电路 (IC) 或芯片的运行故障可能会产生灾难性后果。这些故障可能源于芯片中逃脱制造测试的缺陷,或者由于操作环境等因素在系统运行期间可能发生的暂时性故障。为了避免此类故障,这些IC需要最高质量的制造测试,以实现低于百万分之一(DPPM)的缺陷率和系统内测试功能,以确保芯片在ISO 26262标准定义的系统运行期间的安全功能。IC设计人员通常基于高级故障模型(如单元感知、路径延迟、转换等)生成扫描测试模式。以满足 激进 的 测试 质量 目标, 并 添加 可 测试 性 设计 (DFT), 例如 逻辑 BIST 用于 系统 内 测试。

逻辑BIST是系统内测试的关键DFT组件,用于测试设计的非存储器部分。与使用带有扫描测试引脚的自动测试设备(ATE)施加模式的扫描测试不同,逻辑BIST测试图案是使用伪随机码型生成器(PRPG)在芯片上生成的,并且测试模式响应使用多输入移位寄存器(MISR)累积到签名中。将MISR签名与片内或片外的预期签名进行比较,以确定测试通过/失败状态。除了要求高测试覆盖率外,安全关键应用中IC的在系统测试必须具有较短的测试时间,因为测试是在芯片的功能操作期间进行的。影响逻辑BIST测试时间和测试覆盖率的主要因素之一是设计中的路径生成未知(即X)仿真值,因为X会破坏在多个测试模式或测试间隔中累积的MISR特征。这会导致测试覆盖率丢失或需要更多的测试模式来实现目标测试覆盖率,从而增加测试时间。标准逻辑BIST解决方案需要X-clean设计来避免此问题。

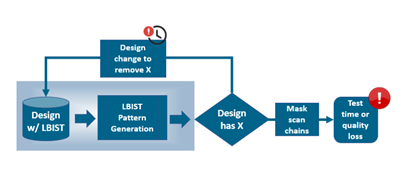

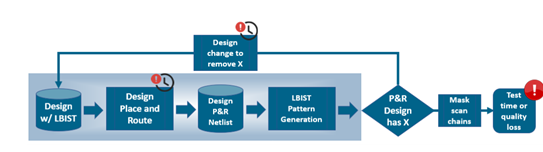

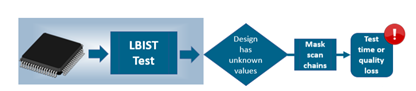

由于各种原因,X出现在设计开发周期的不同阶段,包括未建模的电路行为,缺少设计初始化以及静态时序分析(STA)中未考虑的时序路径。使用标准逻辑 BIST,设计人员遵循一种通过设计更改或通过在模式生成期间屏蔽扫描链来处理 X 的方法,以牺牲设计进度或测试质量为代价。为了在布局布线过程之前消除X,设计人员通常会选择设计更改而不是屏蔽扫描链,因为在此阶段设计更改的周转时间很短(如图1所示)。但是,在放置和路由过程之后,通常会在添加计时信息的情况下出现新的 X。这种情况如图 2 所示,设计人员被迫在设计更改/重新旋转导致的显著延迟和链掩蔽导致的测试质量降低之间做出权衡。未知的逻辑值对硅后提出了更严峻的挑战。随着当今激进的设计实践和技术节点,由于复杂的故障模型、时序边际和工作参数变化等因素,几乎不可能预测硅后出现的未知值。如图3所示,在硅片中不可能进行设计更改,唯一的选择是通过屏蔽链来在测试覆盖率和测试时间上妥协。由于这些因素,设计人员必须牺牲标准逻辑BIST的设计进度或测试质量。

图 1:在布局布线过程之前消除 X 的设计流程。

图 2:在布局布线过程后消除 X 的设计流程。

图 3:在硅后设计中处理未知值的流程。

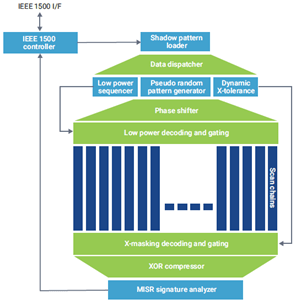

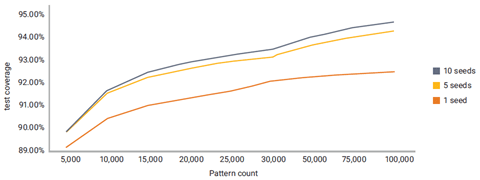

X容忍逻辑BIST(如TestMAX XLBIST)使设计人员能够避免这些权衡,最大限度地减少Xs对整个链掩码造成的测试质量的影响,同时还消除了设计更改的需要。TestMAX XLBIST可以对包含Xs的扫描单元执行动态屏蔽,而不是屏蔽导致高测试覆盖率损失的整个扫描链。 扫描单元掩码允许链可观察性,并在大多数场景中实现与X-clean设计相似的测试时间和覆盖范围,而无需相关的开销。TestMAX XLBIST 通过智能地使用其 PRPG 重新播种功能、动态 X 容忍解码器和 X 掩码解码逻辑来实现测试目标(如图 4 所示)。图 5 显示了给定数量的模式种子的测试覆盖率与模式计数的示例比较。

图 4:TestMAX XLBIST 架构。

图5:TestMAX XLBIST通过多个种子实现了高覆盖率。

除了测试时间和覆盖范围要求外,安全关键应用中使用的IC还需要在其功能操作的不同阶段进行测试,以确保及早发现和减轻任何潜在缺陷及其影响。TestMAX XLBIST支持系统内测试的三个主要阶段:上电系统测试(POST),功能操作期间的测试和断电系统测试。TestMAX XLBIST架构还设计用于支持用于制造测试的确定性测试模式生成,当芯片需要制造和系统内测试时,无需单独的编解码器逻辑。除了X容差功能外,TestMAX XLBIST还可以生成硬件,为系统内测试和制造测试启用功耗感知模式。它还支持基于高级故障模型(包括单元感知、路径延迟和转换)的系统内测试模式。

在当今充满复杂设计的竞争格局中,设计人员不能在IC的设计进度和测试质量之间做出妥协,尤其是在安全关键型应用中。通过进行设计更改迭代或按照标准 LBIST 的要求添加更多测试模式来实现 X-clean 设计以满足测试目标是不可接受的解决方案。TestMAX XLBIST 在 X-clean 设计上以最佳方式执行,同时还能够处理具有 X 值的设计,而无需更改设计或屏蔽整个扫描链,从而满足设计进度和测试质量目标。

审核编辑:郭婷

-

芯片

+关注

关注

463文章

54429浏览量

469362 -

集成电路

+关注

关注

5464文章

12686浏览量

375727 -

解码器

+关注

关注

9文章

1225浏览量

43770

发布评论请先 登录

基于BIST利用ORCA结构测试FPGA逻辑单元的方法

求助,关于S32k322 BIST问题求解

为什么S32K344运行Bist_Run(BIST_SAFETYBOOT_CFG)进入Hardfault?

DFT和BIST在SoC设计中的应用

BIST测试是否正确

数字BIST的基本原则

ZC706 BIST编译在Linux上失败

S32K BIST当sw调用api Bist_Run() 以启动bist时,mcu重置了怎么处理?

基于LFSR优化的BIST低功耗设计

基于BIST的编译码器IP核测

针对FPGA可编程逻辑模块的离线BIST测试方法

电源技巧:不要让USB电压下降减慢充电器的速度资料下载

不要让X成为逻辑BIST的问题

不要让X成为逻辑BIST的问题

评论