虽然减少工艺节点在电路密度和提高计算能力方面带来了巨大的好处,但也有一个相关的缺点——增加设计可变性。这种可变性源于对裕量的需求,即工程师为提高设计稳健性和降低流片风险而引入的规范保护带。规格设置得越严格,失败的风险就越大,从而影响最终成本。设计人员需要新的工具来有效且高效地最大限度地减少他们指定的过多设计裕量,从而降低成本和风险。

这篇由两部分组成的文章的第一部分将探讨设计人员在开发针对节能设计的 SoC 时面临的问题,以及 Synopsys 的 PrimeShield™ 技术如何帮助优化低功耗设计,同时实现积极的上市时间目标。

现实

长期以来,半导体一直根据最坏情况的工艺、电压和温度(PVT)进行指定。在设计阶段,设计人员必须平衡性能与功耗和面积(PPA),努力实现所需的每瓦性能目标。为了评估可变性对电路性能的影响,设计人员采用静态时序分析(STA)来评估每个时序路径。由于影响PPA的因素很多,设计人员经常执行SPICE仿真以获得更准确的结果。

然而,随着工艺节点的进步和电路密度的增加,上市时间的压力也越来越大。结果是,设计团队可以执行预签核的鲁棒性分析量有限,导致过度悲观(增加设计裕量以确保达到性能和功耗目标)。在设计和制造中,不言而喻的是,越早发现错误或进行优化,影响就越低——鲁棒性改进也不例外。

这种过度设计的最终结果是鲁棒性降低,直接影响最终产品PPA、上市时间和材料成本——所有这些因素都可能使半导体供应商在市场上失去竞争力。需要一种强大的统计鲁棒性分析工具,该工具可以在设计周期的早期应用,并帮助提高设计对变化的抗扰度。

进入***盾

蒙特卡洛类固醇

虽然蒙特卡洛SPICE仿真一直是电路分析的黄金标准,但它无法适应当今的电路密度。就其本质而言,蒙特卡罗模拟必须重复相同的分析数千次甚至数百万次才能获得高西格玛精度,因此仅适用于数十个细胞。

PrimeShield 利用 Synopsys 的 PrimeTime® 黄金签核引擎,在几秒钟内执行 SPICE 精确的时序计算和变化建模。为了实现所需的吞吐量,PrimeShield利用蒙特卡洛分析的重复性,并使用获得专利的机器学习技术来大大提高分析性能。结果是分析通量提高了 100 到 10,000 倍,在几分钟内对具有数十亿个细胞的大规模 SoC 中的关键时序路径执行统计仿真,而不是传统统计仿真所需的数天或数周。

用于低功耗设计的PrimeShield

PrimeTime引入了先进的电压调节技术,使设计人员能够在广泛的范围内对任何电压电平进行准确分析。设计人员现在有一种方法可以扫描电压范围,在不同的电压电平下试运行相同的设计,并最终找到所需的PPA或每瓦性能目标的电压最佳点。虽然 PrimeTime 解决方案已被证明既准确又有效,但扫描过程既耗时又耗费资源。

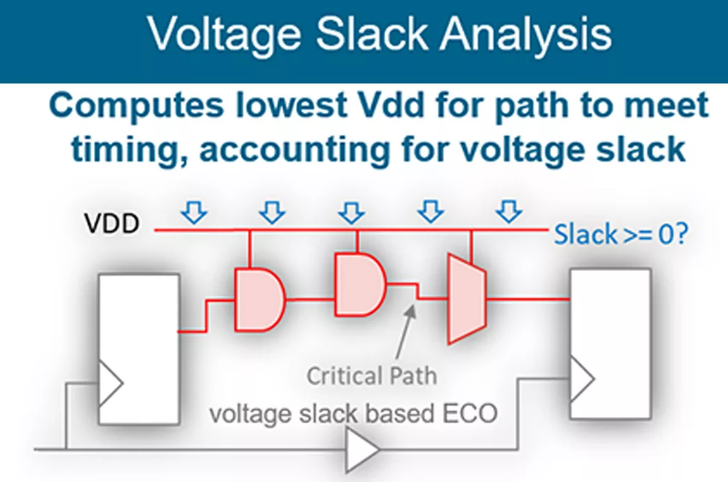

PrimeShield扩展了PrimeTime核心技术,并引入了一种新的PPA签核分析类型,称为电压松弛,它表示设计满足性能要求的每个单元或每个路径的最低电压。这种签核分析使设计人员能够有效地查明电压瓶颈,以提高IR压降鲁棒性,提高电压裕量均匀性,并发现直接微调工作电压的机会。可变电压现在可用作 PPA 优化指标。

电压松弛的大小决定了路径对电压变化的敏感性。具有小电压松弛的路径被认为是工作电压关键型的。PrimeShield优先考虑具有较小电压缓冲的固定路径,以提高设计对IR压降的弹性。它还通过降低工作电压或通过提高工作电压来提升频率,从而实现节能。此外,PrimeShield支持基于电压松弛的优化,并且已被发现对混合V非常有益。T设计。

动态或开关电源已成为功耗优化的重中之重,尤其是对于高级节点 HPC 应用。虽然降低工作电压可以直接降低动态功耗,但工作电压长期以来一直是设计流程中的静态指标。高级节点上更高的电池和功率密度也使得降低电压供应水平成为一项极其困难的任务。尽管如此,较低的电压水平对于实现有竞争力的每瓦性能目标至关重要。因此,一个新的购电协议权力机会出现了。

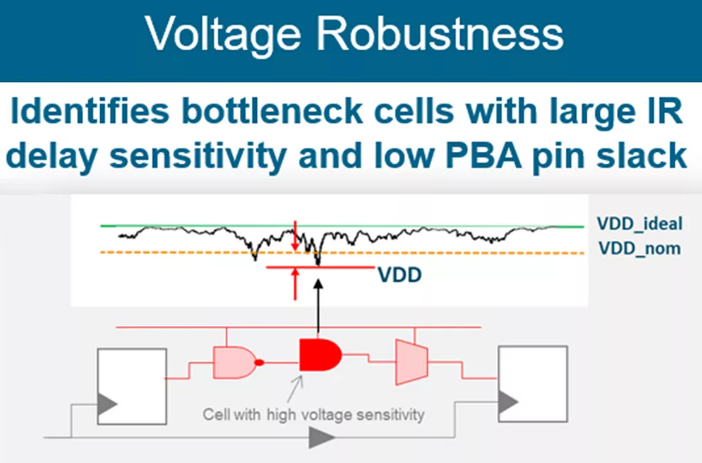

功率与电压有关,但降低工作电压会影响性能。PrimeShield 计算每条路径满足时序要求的最低工作电压,准确考虑电压松弛。利用这些数据,PrimeShield执行电压鲁棒性分析,以识别具有大IR压降灵敏度和引脚松弛不足的瓶颈电池。因此,设计人员可以对设计进行微调,以实现最低的工作电压,同时达到性能目标。

因此,PrimeShield电压松弛和鲁棒性分析使用户能够提高超低功耗设计中对电压变化的设计弹性,并进一步节省功耗以获得最佳能效。

审核编辑:郭婷

-

半导体

+关注

关注

339文章

31279浏览量

266792 -

仿真

+关注

关注

55文章

4539浏览量

138700 -

SPICE

+关注

关注

6文章

199浏览量

44716

发布评论请先 登录

面对不断增加的设计可变性,提高稳健性并最大限度地减少过度悲观情绪

面对不断增加的设计可变性,提高稳健性并最大限度地减少过度悲观情绪

评论