长期以来,IC测试的基本挑战一直保持不变。所有测试策略的核心是可控性和可观察性。首先,使用已知的测试向量控制芯片的状态,然后观察芯片以确定其行为是良好还是错误。多年来,已经有许多创新使所需的芯片测试更容易处理。得益于 EDA 社区的创新,可测试性设计 (DFT) 和自动测试模式生成 (ATPG) 为 IC 测试 的挑战带来了丰富的方法。

当前限制

这些方法的主要内容是扫描测试。在这里,普通人字拖被具有双重用途的扫描人字拖所取代。在正常操作中,它们的功能与任何其他翻牌一样。然而,当启用扫描模式时,这些器件形成一个链,允许将测试向量转移到电路中,基本上将电路的状态设置为已知值。这解决了测试挑战的可控性部分。然后,这些触发器返回正常工作状态,以允许电路处理已知数据。然后,重新启用扫描模式,并将内部数据值移出电路,以便在芯片的主输出端口进行检查。这将处理测试质询的可观测性部分。

虽然简单而优雅,但基于扫描的设计有两个基本限制。首先,这个过程可能很慢,需要许多时钟周期来扫描数据,然后扫描出来进行观察。请记住,您是在生产测试仪上运行这些测试。这些是非常大且昂贵的设备,每一秒的使用都会增加额外的成本。第二个问题是芯片I/O子系统的负担。扫描设计需要大量额外的引脚,而芯片I/O通常供不应求。因此,支持许多芯片I/O的扫描模式的额外开销可能很麻烦。

目前的方法还有第三个缺点,相对较新。如上一篇文章所述,芯片测试在零件交付时不再停止。随着硅生命周期管理(SLM)的兴起,从芯片收集数据将贯穿其整个生命周期。这里描述的扫描测试方法依赖于IC测试仪提供的大量特殊设置。外地没有这种设备。

建议的解决方案

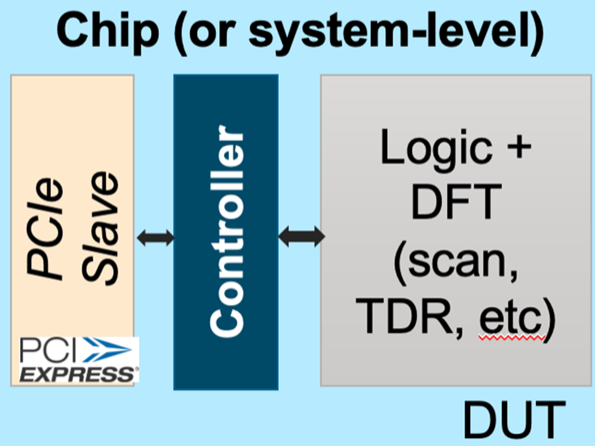

解决这些问题的新方法隐藏在众目睽睽之下。I/O几乎是每个设计的瓶颈,因此高速协议已成为最小化此问题的常用方法。几乎每个芯片都有一个PCIe或USB接口。这些是支持各种 I/O 要求的高性能端口。如果这些端口成为未来设计的新扫描端口会怎样?测试性能将得到增强(成本将下降),引脚电子器件将更简单,在现场访问芯片的测试功能将容易得多。将扫描测试与系统级测试相结合,还有另一个潜在的成本优势。下图说明了为板载 PCIe 接口创建另一种模式的基本方法。

图 1: 新的测试访问电子设备

交付解决方案

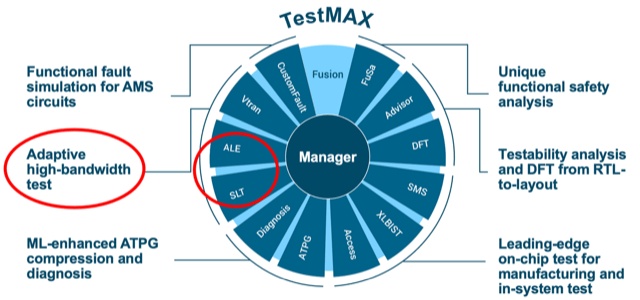

Synopsys TestMAX 系列测试产品于今年 3 月推出。它代表了业界最全面的测试解决方案集,可满足制造测试要求以及汽车和其他功能安全相关应用的快速发展的在系统测试要求。该平台提供广泛的测试支持,如下所示。

该平台的两个部分,TestMAX SLT和TestMAX ALE实现了这种革命性的新扫描测试方法。让我们来看看这是如何工作的。

图2:TestMAX平台

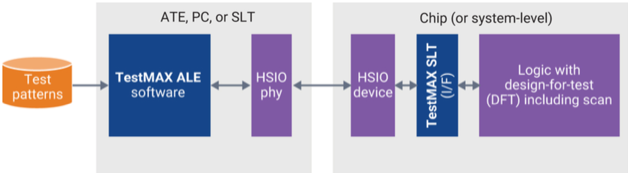

首先,TestMAX SLT在现有的高速接口(HSIO,例如USB,PCIe)和DFT逻辑之间生成前面描述的片上接口,DFT逻辑通常由扫描和压缩功能组成。然后,TestMAX ALE为HSIO提供类似于软件设备驱动程序的软件接口。它支持操作系统文件 I/O 与驱动主机 HSIO 的软件层之间的通信。下图说明了完整的端到端双向路径。

图3:一种新的扫描测试方法

这种方法的好处包括:

高带宽测试数据,降低测试成本

引脚数最少的接口,适用于大多数设计

轻松适应支持不同的高速输入输出接口 (HSIO)

更简单的自动测试仪设备 (ATE) 引脚电子元件,可降低测试仪成本

通过应用初始制造测试(硅生命周期管理支持)确保系统内器件的高质量

我们对IC测试的这种新范式感到非常兴奋,并相信它将降低测试成本,同时提高质量。我们还与测试领导者爱德万测试和泰瑞达合作,以确保这项新技术的顺利部署。

审核编辑:郭婷

-

芯片

+关注

关注

455文章

50697浏览量

423046 -

接口

+关注

关注

33文章

8569浏览量

150999 -

eda

+关注

关注

71文章

2754浏览量

173179

发布评论请先 登录

相关推荐

泰克在2013 IDF展示业界最完整、最灵活的高速串行信号测试解决方案

FPGA的PCIE接口应用需要注意哪些问题

如何进行PCI-Express的一致性测试和分析

高速 ADC/DAC 测试原理及测试方法

对RIFFA架构的的DMA性能(Scatter-Gather DMA)进行测试

基于USB接口的通用测试仪的设计与实现

测试行业三家企业联手,举办2021高速数字接口测试巡回研讨会

网络研讨会-高速接口测试:PCIe5.0测试方案

M8040A误码仪助力高速数字接口测试

使用高速PCIe或USB接口提高测试性能并允许在现场进行测试

使用高速PCIe或USB接口提高测试性能并允许在现场进行测试

评论