随着物联网 (IoT) 设备的迅速普及和部署,各个层面都出现了安全风险。它可能在可用性级别,例如社会工程、借口、网络钓鱼;在原始级别,例如密码分析;在软件级别,例如客户端脚本、代码注入;现在甚至在硬件级别。在硬件运行过程中,我们经常看到侧信道分析、冷启动、故障注入等风险;或在硬件设计和制造周期中。显著的风险包括 IP 盗窃、逆向工程、克隆和硬件木马。

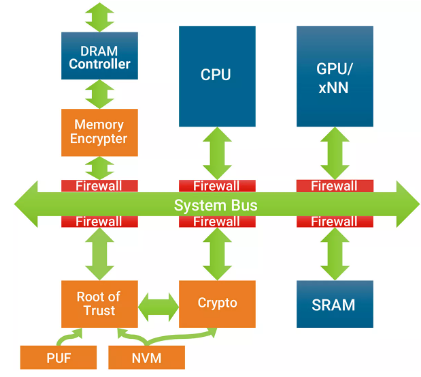

图 1:SoC 中的安全基础架构

一个安全的系统也需要各个级别的实施支持。在每个级别上,基于以下假设来评估安全机制的强度:基础实现满足一组给定的安全要求,这些要求随后在较低级别强制执行。最常见和最重要的安全要求是机密性和完整性。机密性要求系统不会无意中泄露信息,并且通过部署秘密加密密钥来实现。完整性要求系统执行的功能不多于也不少于预期,并通过验证和测试技术进行检查。确保系统执行的功能不超过预期是一个更困难的问题,但现在正在开发许多解决方案。最近,DARPA授予Synopsys为其安全硅自动实施(AISS)计划的主承包商,该计划非常专注于硬件硅安全实施和自动化。

作为核心的 EDA 工具业务部门,Synopsys 的设计团队是 AISS 计划的关键部分。尽管安全实现在IC设计中并不是一个新概念,但许多设计人员并不了解用于实现的技术。这包括限制逻辑不关心、禁用未使用的有限状态、安全内核中的静态代码加密、动态代码完整性验证,以及容错设计和水印等。作为安全实现专家的实施工程师还必须考虑安全性、功耗、成本和性能之间的权衡;对于普通设计师来说,这是一项艰巨的任务。DARPA的AISS计划旨在为这一领域提供实用的解决方案。这项工作不仅可以自动化和解决安全设计挑战,而且在工具内部设置安全性还可以提高安全级别,因此您不必向更广泛的开发社区公开某些安全机制。

AISS是一个为期4年,3阶段的计划。第 1 阶段是将安全系统组合在一起,第 2 阶段是为其添加一些自动化,第 3 阶段是优化功能,这是 EDA 真正可以大放异彩的地方。例如,设计人员知道如何运行简单的流,但为了安全起见,可能有一些我们不想向设计人员公开的特殊功能。我们只想将该结构放入设计中,将所有实现留给工具和自动化,而不会公开设计意图。有时,一个域所需的自动化与安全域的需求不一致。例如,扫描插入,您可以完全访问设计中的每个触发器,对于邪恶的参与者来说,这是一个非常容易进入并控制输入或观察输出以查看设计内部发生的事情的目标。添加压缩会使这变得更加困难,因为我们在前端使用多路复用器或在后端使用专用OR门。我们还可以添加压缩函数,在前端具有线性反馈移位寄存器,在后端具有多个输入签名寄存器。尽管这进一步混淆了进出的数据,但它仍然容易受到不良行为者的攻击。

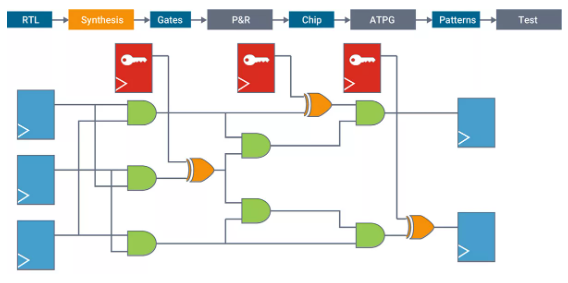

从流程的角度来看,用户会期望某些事情。例如,当他们将 RTL 转换为门时,他们希望能够运行流验证,并且一切都很好并且有效。在某些情况下,我们会有一些 RTL 到 RTL 的转换,因此我们需要确保当我们在这里和那里之间插入某种键或锁定函数时,这些额外的寄存器或额外的组合锥体仍然可以从一个 RTL 识别到另一个。同样,如果我们在综合时在RTL和门电平之间插入一些门,我们希望确保我们之前放入的东西不会被擦除,并且在综合优化通过并从安全角度影响设计后突然不起作用。然后,之后,我们希望完全验证工作,因为我们添加了额外的密钥和修改的锥体,也许密钥是已知的或未知的。

图 2:添加到设计逻辑中的混淆和锁定

AISS将把我们自摩尔定律以来业界使用的PPA驱动的实施概念扩展到PPAS,“S”表示安全约束。虽然PPA(功率、性能和面积)以瓦特、赫兹和纳米为单位定义,但以算法驱动的自动化所需的定量方式定义安全性更为复杂。事实上,不仅风险水平本身需要定量规范,而且需要对与风险相关的安全成本进行定量评估,以生成用于优化的高级成本函数。一旦定义了这些参数,我们将需要对这些相关的安全级别定义和测量进行行业标准化。与PPA不同,安全设计是一个复杂的组合问题,其中存在的特殊情况比倾向于NP困难的一般情况具有较低的复杂性。它不仅仅是一种依赖于控制和基于数据流的安全分析的优化算法,这使得这项工作非常令人兴奋。

为了提供更多的颜色,例如,为了保护供应链,我们正在应用水印。我们正在为IP加水印,因此当它进入现场时,我们可以看到IP是否属于我们的。为了防止逆向工程,我们提供了逻辑锁定和混淆功能,我们可以选择实现这些功能。我们可以利用这些安全工具或实现细节,并将这些功能应用于 RTL 或基于我们的安全目标的设计。如果我们试图提高供应链的安全性,则可以实施水印或锁定。对于逆向工程,混淆可以与锁定结合使用。您可能希望为这四种安全问题(供应链、逆向工程、侧信道攻击、特洛伊木马)设置不同级别的保护,我们可以拨入这些内容,选择一定数量或选择一定数量的修改并达到一定级别:128 位锁或 256 位锁。水印是 50 步还是 1,000 步?

我们的最终目标是将从架构到安全强化 RTL 的时间从一年缩短到一个月,甚至一周,并且成本大幅降低。设计流程片段需要相互交互,以便在前面的步骤中插入的特征不会在后面的流程步骤中丢失。需要保持数据元素及其在设计和部署中的使用之间的协调,以便密钥可以解锁设备功能,并且可以在现场验证水印。

审核编辑:郭婷

-

寄存器

+关注

关注

31文章

5382浏览量

121414 -

eda

+关注

关注

71文章

2792浏览量

174097 -

IOT

+关注

关注

187文章

4232浏览量

197923

发布评论请先 登录

相关推荐

EDA是设计安全系统的基础

EDA是设计安全系统的基础

评论